转帖:新版vivado2019.2新增增量综合功能

从 Vivado 2019.1 版本开始,Vivado 综合引擎就已经可以支持增量流程了。这使用户能够在设计变化较小时减少总的综合运行时间。

Vivado IDE 和 Tcl 命令批处理模式都可以启用此流程。如需了解有关此流程的详情,请参阅《Vivado Design Suite 用户指南:综合》 (UG901)。

在我们开始讨论增量综合之前,我们先来讨论一下一些重要的概念,以便能够更好地理解该流程。

1. 并行综合

为了缩短总运行时间,如果设计足够大,并且可以获益于并行流程,Vivado 综合即会启动并行流程。

并行流程会将设计划分为更小的、由并行进程独立处理的“RTL 分区”。

只有当设计规模足够大时,Vivado 综合才会决定使用并行流程。设计规模应该至少有 5 个 RTL 分区是大于 10K 实例大小才行。

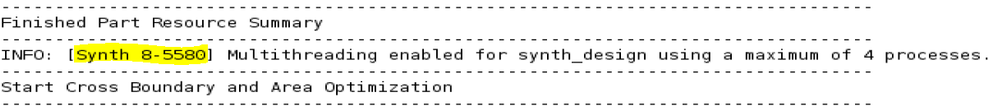

要检查该工具是否已使用并行流程,您可以在综合日志中查找“Multithreading enabled for synth_design…”消息。

以下消息确认已使用并行流程完成了“Synthesis”,且设计与增量综合运行兼容:

"INFO: [Synth 8-5580] Multithreading enabled for synth_design using a maximum of 4 processes." (INFO:[Synth 8-5580] 为 synth_design 启用多线程,最多使用 4 个进程。)

2. RTL 分区

Vivado 综合会基于实例将大型设计划分为多个分区,以便启用并行流程进行综合。

以下快照示出的是工具如何在“Vivado 综合”日志文件中报告分区情况:

RTL 分区报告:

+------+----------------------------+------------+----------+

| |RTL Partition |Replication |Instances |

+------+----------------------------+------------+----------+

|1 |Partition_name1 | 1| 31536|

|2 |Partition_name2 | 1| 21130|

|3 |Partition_name3 | 1| 18061|

……..

……..

如果设计符合并行综合的要求,工具就会将所有分区写入.runs/synth_1/runme.log 文件。

如果使用的是增量运行,这些分区可以帮助工具识别哪些分区已更改并需要重新综合,并跟踪哪些分区是完整的(以保留这些分区)。

注意:作为参考的运行结果中使用并行综合是进行增量综合的必要条件。如果 50% 或更多的分区已被更改,这个工具即会使用默认流程,而不使用增量流程。

下图显示的是增量综合的流程描述:左侧显示的是增量流程的输入集及生成的输出文件,右侧显示的是相应的命令。

如需了解有关工程级和非工程级流程的详情,请参阅《Vivado Design Suite 用户指南:综合》 (UG901)。

修订后的设计要点:

修订后的设计在顶层不应有变化。

修订后的流程与初始“synth_design”命令使用的“Global Synthesis Settings”应完全相同。

如需对较低层级模块进行工具选项或属性的改动,则需对该层级使用 BLOCK_SYNTH 属性。如需了解有关 BLOCK_SYNTH 流程的详情,请参阅《Vivado Design Suite 用户指南:综合》 (UG901)。

如果 50% 以上的设计已更改(分区被更改),则该工具会使用默认综合,而不会使用增量综合。

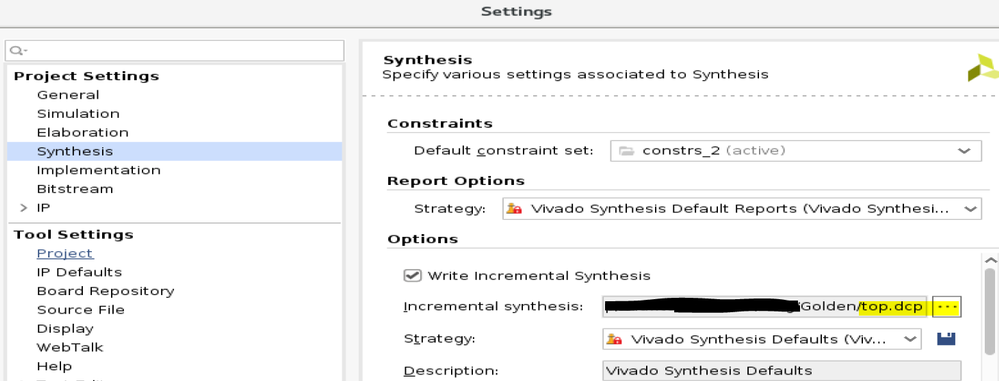

工程流程的增量综合运行示例:

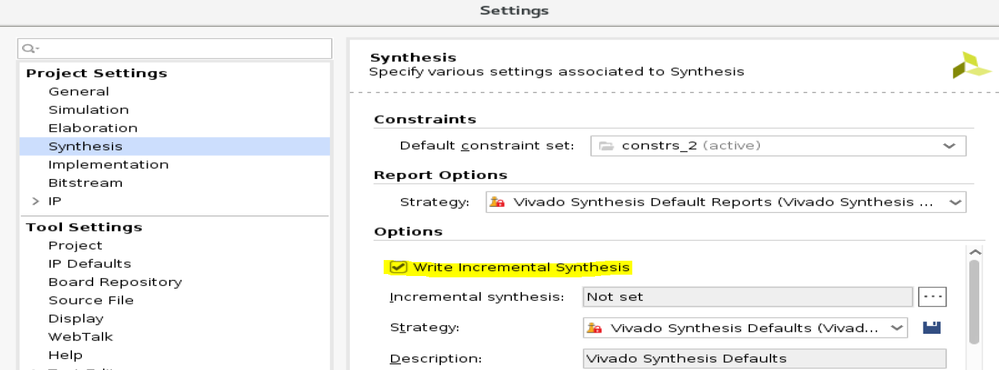

要开启增量综合流程,在最初对设计进行综合时,请确保选中“Write Incremental Synthesis”选项以便为增量运行生成增量 checkpoint。

请通过“Synthesis Settings”窗口来设置此选项:

启动综合后,请查看日志文件以确认是否使用了并行综合。

在综合日志文件中查找 INFO:Synth 8-5580。

此外,您可以在日志文件中查看打印的“RTL 分区”详情,如下所示:

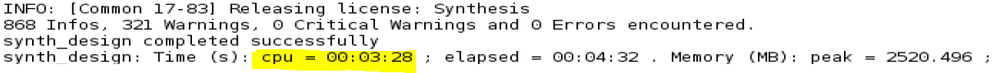

在日志文件的末尾,您可以查看到综合运行所花费的总时间。

完成综合后,您可以保存生成的、将用于增量流程的 checkpoint 文件,也可以使用工具选项“Automatically use the checkpoint from the previous run”(自动使用上一次运行的检查点)。

您现在就可以修改设计或 RTL 了。

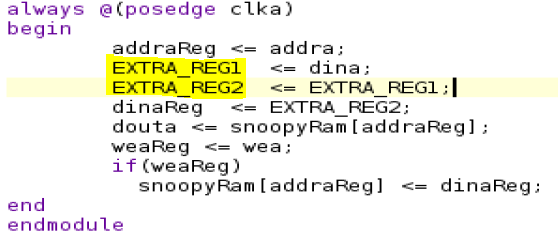

现在我们一起来看一下一个简单的例子。在这个示例中,我在数据路径中添加了两个寄存器。

下面的屏幕截图示出的是为增量综合设置增量 checkpoint 的示例。

要确认该工具是否读取了增量 checkpoint,请在生成的综合日志文件中查看“Command: read_checkpoint -incremental ./top.dcp”的消息。

该工具会分析已更改和未更改的设计,并报告摘要(该摘要可帮助用户了解设计改动和所需的重新综合的部分)。

以下是一个“增量综合摘要报告”示例:

变更摘要详情:

- 模块名称:在设计分区内 RTL 被更改的模块。请注意,一个分区下可能包含不止一个模块。

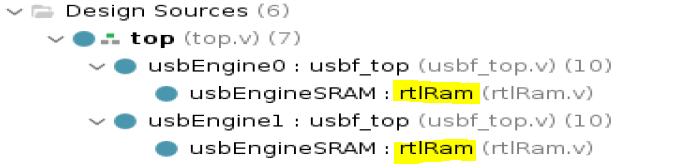

- 复制:所提到模块的实例化总数(在本例中为“rtlRam”)。复制数取决于直接实例化的数量。

例如(参见下面的屏幕截图),“rtlRam”仅由“usbf_top”实例化一次(因此 Replication = 1),即使 usbf_top 被调用两次也是如此。

1. 实例:在 elaboration 阶段之前“rtlRam”下的单元/原语数。在 elaboration 和综合阶段之后,这个数字可能会有所变更。

2. 变更百分比:RTL 变更 (66)/未变更设计总数 (801353) * 100 = 0.008%

3. 整个设计的大小:整个设计中的单元总数(包括已更改和未更改的设计)

4. 再综合设计的大小:请注意,如果属于分区的某一个模块中有任何更改,工具即会重新综合整个分区。在这个例子中,更改的分区大小为 30279,在设计中被调用了两次,因此“Resynthesis Design Size”数为 ~60555。

此外,工具将重新综合那些被传递了最优化的分区,并且“Resynthesis Design Size”的数量可能会相应地有所变化。

5. 重新综合设计的大小:重新综合的单元数= 60555/801353 * 100 = 7.55%

正如您在下面的综合日志快照中所看到的那样,与之前 3 分 28 秒的默认综合运行时间相比,增量流程后的运行时间仅为 1 分 35 秒。 7. 重新综合设计的大小:重新综合的单元数= 60555/801353 * 100 = 7.55%

设计变化较小时,增量综合是一个非常强大的功能。请随时使用此功能并与我们分享您的反馈。谢谢阅读!

浙公网安备 33010602011771号

浙公网安备 33010602011771号