这次我们来介绍一下UART的基本时序,了解一下底层信号怎么传送的。方便以后使用Verilog HDL实现收发逻辑。

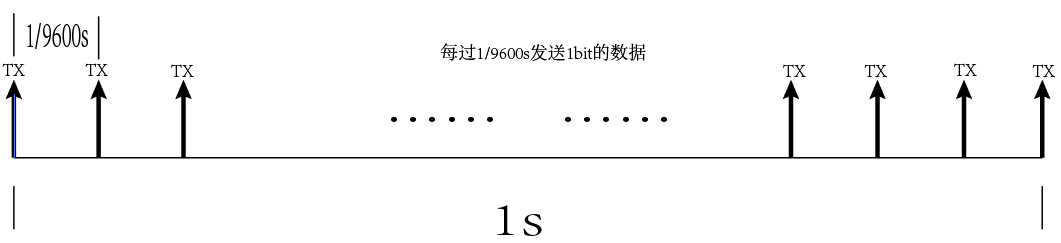

9600bit/s 的意思是每秒发送9600bit,因此可以理解为将1s分解为9600等分,对于发送端来说,每bit电平的维持时间是1/9600s,对于接收端来说,在1/9600s内要完成数据的采样。因此对于不同时间源的设备,如何实现这个发送“节拍”以及设置接收采样频率非常重要,即主从设备对各自主时钟(SCLK)的分频非常重要。

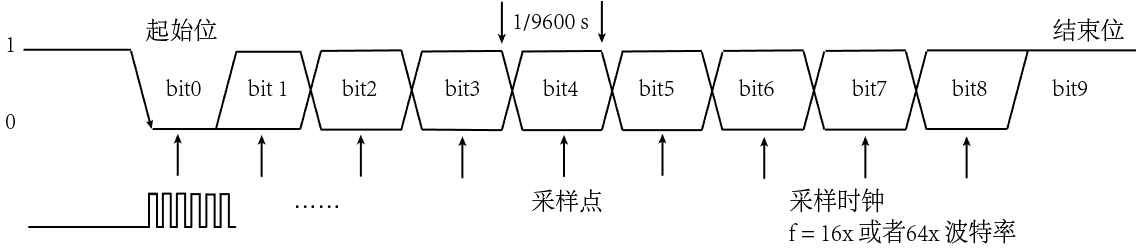

UART的基本时序:

发送端

接收端

UART的每一帧数据一般有10位分别为初始位,8位数据和结束位。对于发送端,将待发送的数据存入发送寄存器,产生起始位即将电平拉低,随后每1/9600s将寄存器中的数据一位一位的发送出去。当数据发送完毕后,将电平拉高等待下一次的发送。对于接收端来说首先要检测是否有数据来,采用下降沿检测的方式来检测起始位。对于数据位的采样,选取数据位的中点位置的电平作为采样数据,中点位置的电平较为稳定。设采样间隔为N,当采样8N后,就可以停止采样了。

采样时钟的如何获取,其实是通过设备的主时钟分频得到的。取16x或者64x倍的波特率时钟作为采用时钟是实践总结出来的,主要是为了无失真的获取数据,同时也为了方便编程。下面举个例子:

主时钟为SCLK = 40Mhz,波特率为9600,则采用频率fs = 16*9600 = 153600。Tsclk = 25ns,Ts = 1/fs = 6510.4167ns,N = Ts / Tsclk = 260.4167。也就是说在每个Ts下有260个Tsclk,以上升沿作为计数标准的话,数130下就为一个Ts,即每数130个Ts的上升沿,采样时钟的电平就翻转一次。采用这种方式就可以得到采样时钟了。对于采样间隔N的计算,每个bit电平的维持时间是Tbit = 16 * Ts = 104166.667ns = 16Ts。bit0采样的是下降沿检测,等待16Ts后,进入bit1的电平时间,在中点采样。因此第一个采样点的时间是(16+8)Ts = 24Ts,以此类推后面的采样点分别为:40,56,72,88,104,120,136,152。

对于发送端,只需要根据波特率对SCLK进行不同的分频就好了。现总结分频如下:

| 波特率 | T | 计数上限 | FPGA50Mhz频率下的计数值;Tsclk =1 / 50Mhz = 20ns |

| 9600 | 104166.667 | T/Tsclk | 5208-1 |

| 19200 | 52083.333 | T/Tsclk | 2604-1 |

| 38400 | 26041.667 | T/Tsclk | 1302-1 |

|

57600 |

17361.111 | T/Tsclk | 868-1 |

|

115200 |

8680.556 | T/Tsclk |

434-1 |

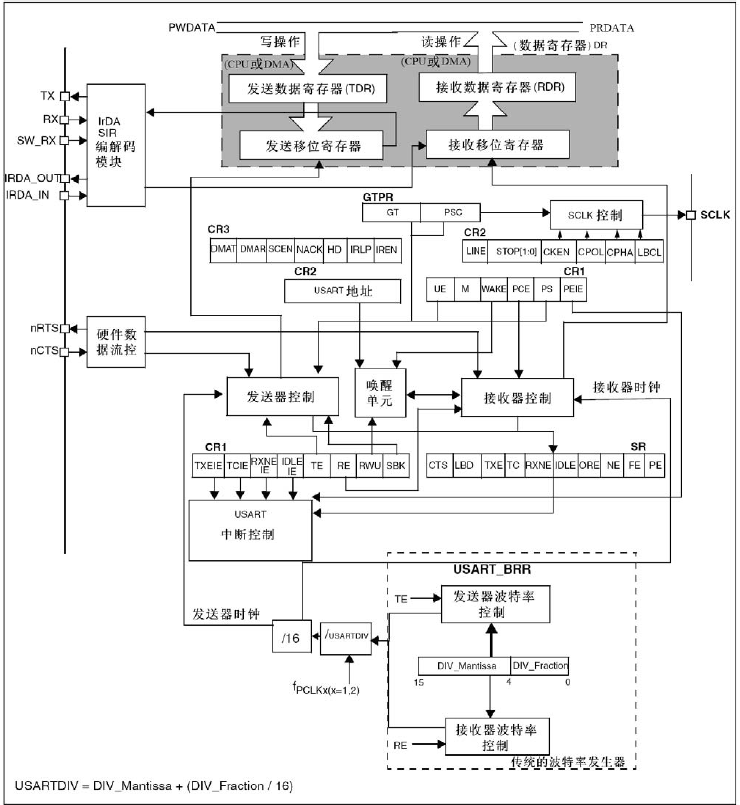

综上所述,对于整个串口而言比较重要的的部分是:波特率发生器、采样时钟发生器、发送模块、接收模块、标志寄存器和中断模块。

对于STM32中的USART,组成部分如下图所示: