内存颗粒封装技术

预备知识

集成电路封装(英语:integrated circuit packaging),简称封装,是半导体器件制造的最后阶段,之后将进行集成电路性能测试。器件的核心晶粒被封装在一个支撑物之内,这个封装可以防止物理损坏(如碰撞和划伤)以及化学腐蚀,并提供对外连接的引脚,这样就便于将芯片安装在电路系统里。

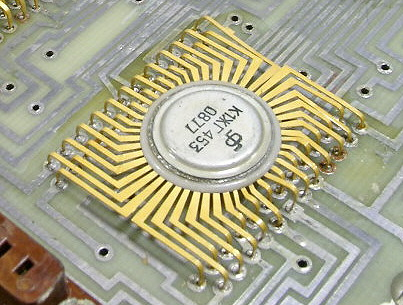

前苏联 1977 年制造的集成电路 K1ZhG453

内存颗粒(芯片)封装是集成电路封装的一类。内存颗粒封装是内存芯片制造工艺的最后一步,也是最关键的一步。采用不同封装技术的内存条,其性能上会存在较大差距。衡量封装技术先进与否的重要指标是芯片面积与封装面积之比,这个比值越接近1越好。内存颗粒封装技术主要有DIP,TSOP,BGA,CSP。

DIP封装

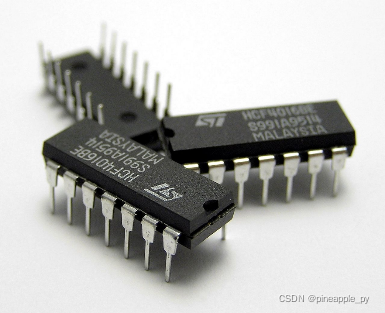

双列直插封装(英语:dual in-line package) 也称为DIP封装或DIP包装,简称为DIP或DIL,是一种集成电路的封装方式,集成电路的外形为长方形,在其两侧则有两排平行的金属引脚,称为排针。DIP包装的元件可以焊接在印刷电路板电镀的贯穿孔中,或是插入在DIP插座(socket)上。

DIP包装的元件一般会简称为DIP*n*,其中n是引脚的个数,例如十四针的集成电路即称为DIP14,下图即为DIP14的集成电路。

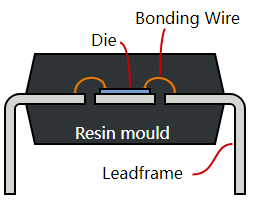

双列直插封装芯片的剖面图

上个世纪的70年代,芯片封装基本都采用DIP。DIP封装形式封装效率是很低的,其芯片面积和封装面积之比为1:1.86,这样封装产品的面积较大,内存条PCB板的面积是固定的,封装面积越大在内存上安装芯片的数量就越少,内存条容量也就越小。同时较大的封装面积对内存频率、传输速率、电器性能的提升都有影响。

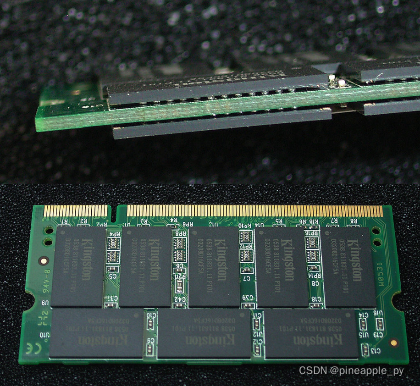

TSOP封装

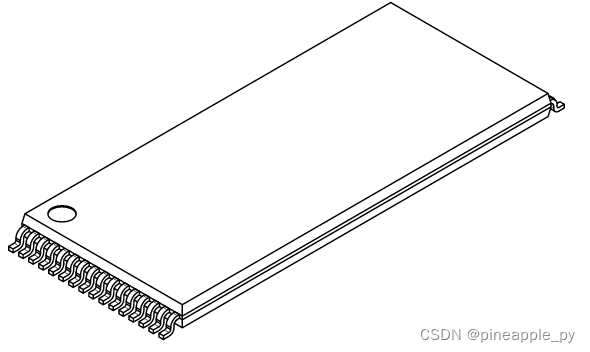

薄型小尺寸封装(英语:thin small outline package)这种封装很薄(约 1 毫米)并且具有紧密的引线间距(低至 0.5 毫米)。TSOP技术是在芯片的周围做出引脚,采用SMT技术(表面安装技术)直接附着在PCB板的表面。

32个引脚的TSOP封装芯片

TSOP I 型:Atmel AT29C010A

由于引脚数多且体积小,它们经常用于 RAM 或闪存 IC。在某些应用中,它们正被球栅阵列封装所取代,后者可以实现更高的密度。TSOP除了用于内存封装外,也适合SRAM、闪存、FSRAM和E2PROM等。

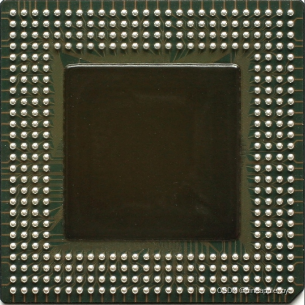

BGA封装

球栅阵列封装(英语:Ball Grid Array)技术为应用在集成电路上的一种表面黏着封装技术,此技术常用来永久性固定如微处理器之类的装置。

一颗Intel嵌入式的Pentium MMX处理器底视图,可见到这些锡球的颗粒

BGA封装能提供比其他如双列直插封装(Dual in-line package)或四侧引脚扁平封装(Quad Flat Package)所容纳更多的接脚,整个装置的底部表面可全作为接脚使用,而不是只有周围可使用,比起周围限定的封装类型还能具有更短的平均导线长度,以具备更佳的高速效能。

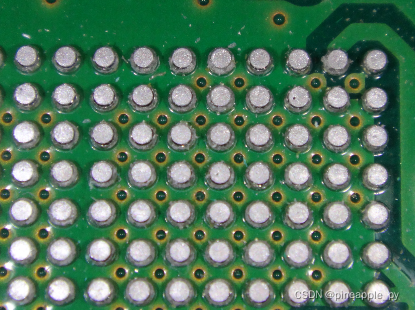

焊接BGA封装的装置需要精准的控制,且通常是由自动化程序的工厂设备来完成的。BGA封装装置并不适用于插槽固定方式。

在移除集成电路芯片后,印刷电路板上的焊球网格阵列。

BGA封装技术是从插针网格阵列(pin grid array; PGA)改良而来,是一种将某个表面以格状排列的方式覆满(或部分覆满)引脚的封装法,在运作时即可将电子讯号从集成电路上传导至其所在的印刷电路板(PCB)。在BGA封装下,在封装底部处引脚是由锡球所取代,每个原本都是一粒小小的锡球固定其上。

这些锡球可以手动或透过自动化机器配置,并透过助焊剂将它们定位。装置以表面贴焊技术固定在PCB上时,底部锡球的排列恰好对应到板子上铜箔的位置。产线接着会将其加热,无论是放入回焊炉 (reflow oven) 或红外线炉,以将锡球熔化。表面张力会使得融化的锡球撑住封装点并对齐到电路板上,在正确的间隔距离下,当锡球冷却并固定后,形成的焊接接点即可连接装置与PCB。

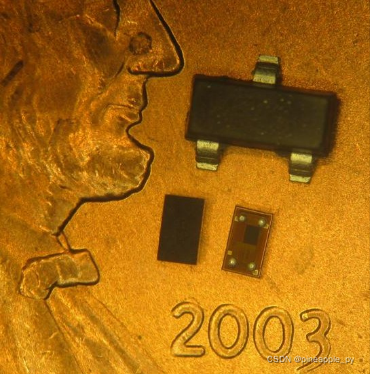

CSP封装

芯片级封装(英语:Chip Scale Package)是最新一代的内存芯片封装技术,其技术性能又有了新的提升。CSP封装可以让芯片面积与封装面积之比超过1:1.14,已经相当接近1:1的理想情况,绝对尺寸也仅有32平方毫米,约为普通的BGA的1/3,仅仅相当于TSOP内存芯片面积的1/6。与BGA封装相比,同等空间下CSP封装可以将存储容量提高三倍。

WL-CSP封装设备,与美国一分钱币的对照。采用SOT - 23器件进行比较

参考链接

若你喜欢我的文章,欢迎关注👇点赞👇评论👇收藏👇 谢谢支持!!!

浙公网安备 33010602011771号

浙公网安备 33010602011771号