AD8253芯片手册阅读

1.是什么

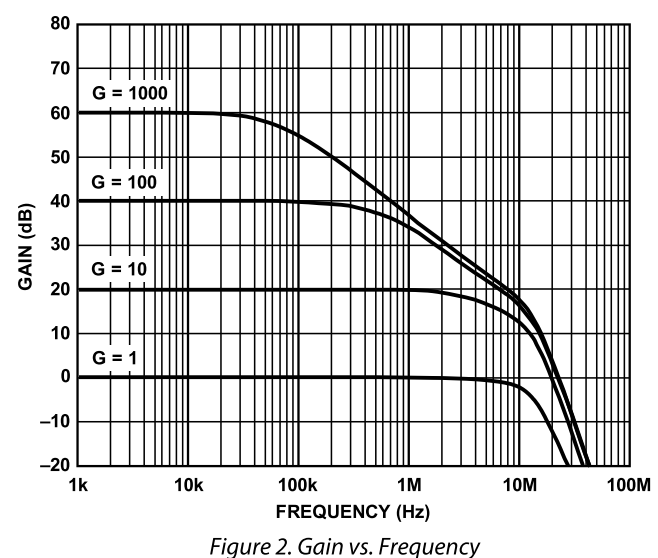

10 MHz,20 V /μs,G = 1,10,100,1000 iCMOS可编程增益仪表放大器(可编程放大器)。

AD8253是一款仪表放大器,具有数字可编程增益,具有千兆欧姆(GΩ)的输入阻抗,使其适合与传感器接口并驱动高采样率模数转换器(ADC)。

高精度直流性能与高速能力的结合使AD8253成为数据采集的理想选择。

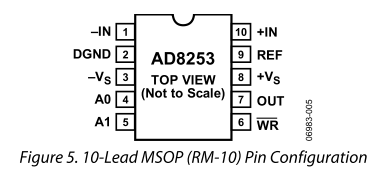

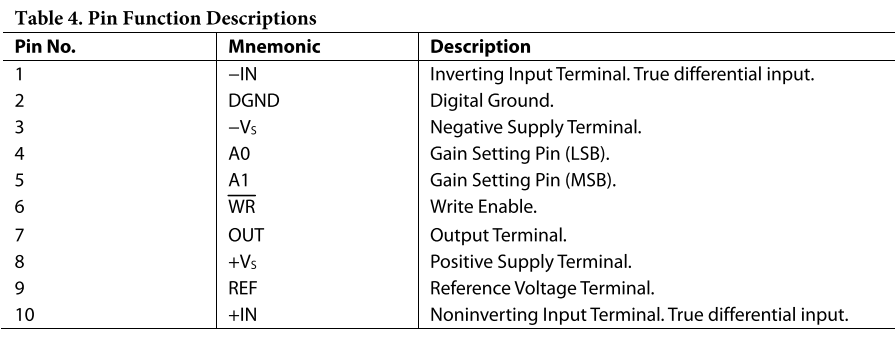

2.引脚配置和功能说明

pin1:反相输入端,差分输入

pin2:数字地

pin3:负供电端子

pin4:增益设置引脚

pin5:增益设置引脚

pin6:写入使能

pin7:输出端子

pin8:正供电端子

pin9:参考电压端子

pin10:同相输入端子,差分输入

3.操作理论(怎么用)

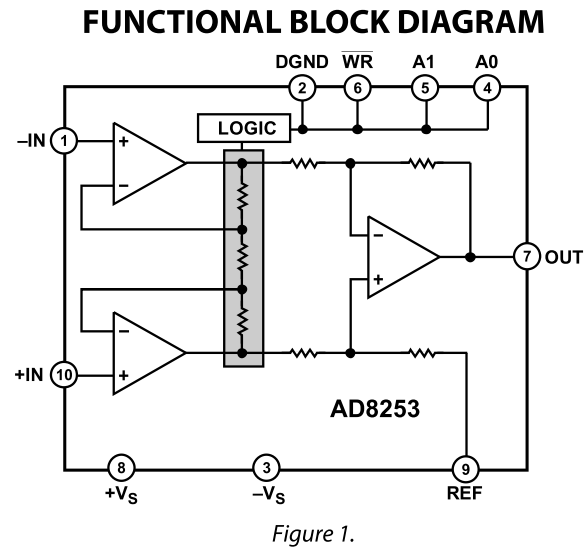

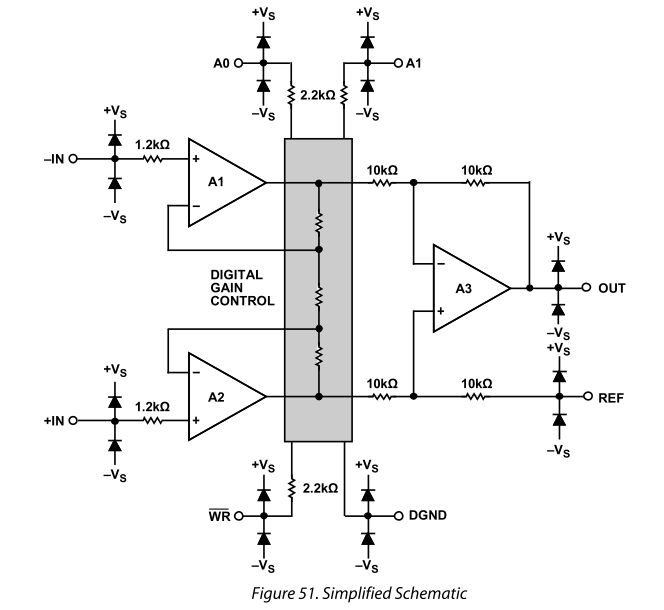

AD8253是一款基于经典3运算放大器拓扑的单片仪表放大器,如图51所示。 并行接口允许用户数字编程1、10、100和1000的增益。通过切换内部精密电阻器阵列中的电阻器来实现增益控制(如图51所示)。

(1)增益模式选择

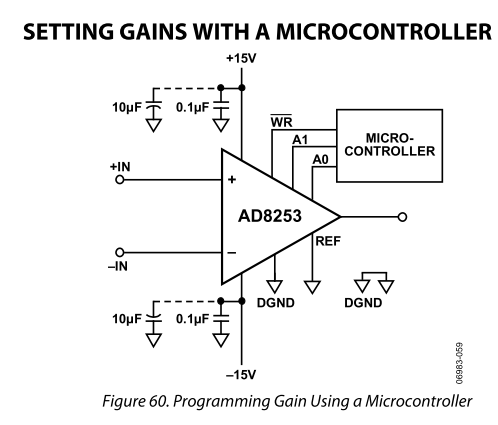

可以使用两种方法设置AD8253的增益:透明增益模式和锁存增益模式。 无论采用哪种模式,都应使用上拉或下拉电阻在A0和A1引脚上提供定义良好的电压。

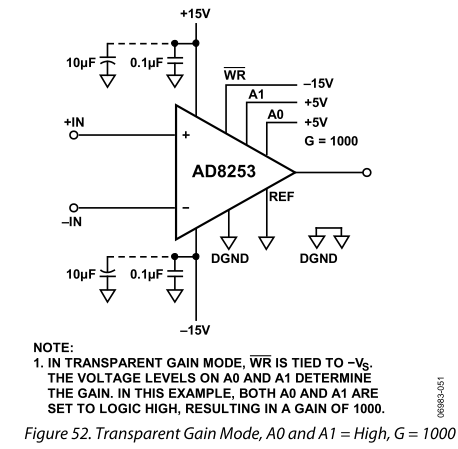

透明增益模式:

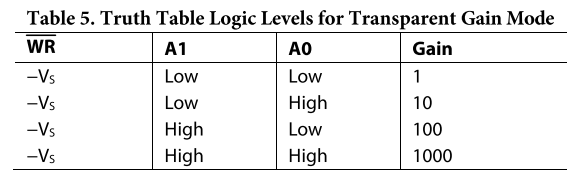

设置增益的最简单方法是 直接通过施加到A0和A1的逻辑高或逻辑低电压对其进行编程。 图52显示了这种增益设置方法的示例,在整个数据手册中都将其称为透明增益模式。 将WR连接至负电源以进入透明增益模式。 在这种模式下,施加到A0和A1的电压从逻辑低到逻辑高的任何变化,反之亦然,立即导致增益变化。 表5是透明增益模式的真值表,图52显示了配置为透明增益模式的AD8253。

锁存增益模式:

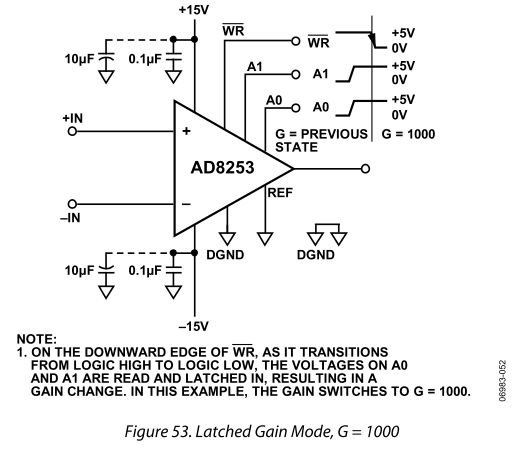

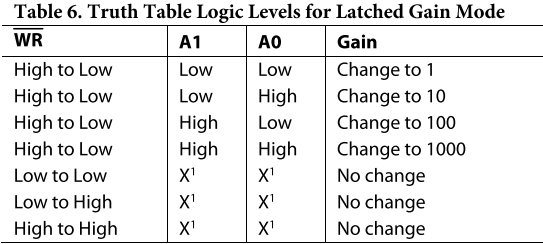

某些应用在同一PCB上具有多个可编程设备,例如多路复用器或其他可编程增益仪表放大器。 在这种情况下,设备可以共享数据总线。 可以使用WR作为锁存器来设置AD8253的增益,从而允许其他器件共享A0和A1。 图53显示了使用这种方法的原理图,称为锁存增益模式。 当WR保持在逻辑高电平或逻辑低电平,通常分别为5 V和0 V时,AD8253处于此模式。 当WR信号从逻辑高电平变为逻辑低电平时,在WR信号的下降沿读取A0和A1上的电压。 这会锁存A0和A1的逻辑电平,从而导致增益变化。 有关这些增益变化的更多信息,请参见表6中的真值表。

(2)电源调节和旁路

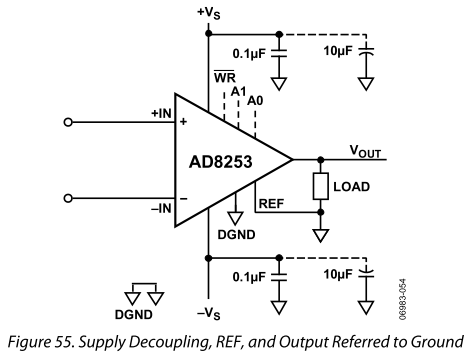

为了获得最佳性能,应使用稳定的直流电压为仪表放大器供电。 电源引脚上的噪声可能会对性能产生不利影响。 与所有线性电路一样,必须使用旁路电容器对放大器进行去耦。

在每个电源引脚附近放置一个0.1 F电容。 可以在离该器件较远的地方使用一个10 F钽电容(见图55),并且在大多数情况下,它可以由其他精密集成电路共享。

(3)输入偏置电流返回路径

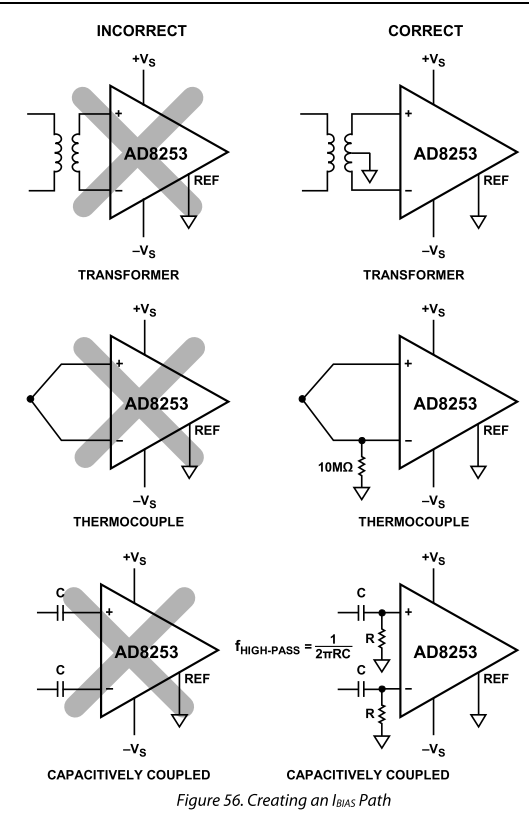

AD8253的输入偏置电流必须具有返回其本地模拟地的返回路径。 当电源(例如热电偶)无法提供返回电流路径时,应创建一个(请参见图56)。

(4)输入保护

AD8253的所有端子均具有ESD保护。 应在每个输入端串联一个外部电阻,以限制电流超过任一电源轨时大于0.5 V的电流。

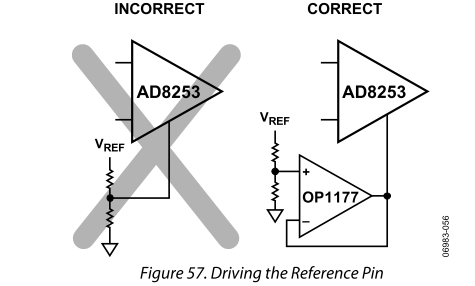

(5)参考端子

参考端REF位于10kΩ电阻的一端(请参见图51)。 仪表放大器的输出以REF端上的电压为参考; 当输出信号需要偏移到其本地模拟地以外的电压时,这很有用。 例如,可以将一个电压源连接至REF引脚,以对输出进行电平转换,以便AD8253可以与单电源ADC接口。 允许的参考电压范围是增益,共模输入和电源电压的函数。 REF引脚的+ VS或-VS不得超过0.5V。

(6)pcb布局

请勿在设备下方铺设数字线路。 将模拟接地层置于AD8253下方。

用数字地屏蔽快速开关信号,以免将噪声辐射到电路板的其他部分,并且切勿在模拟信号路径附近运行它们。

避免数字和模拟信号交叉。 仅在一个点(通常在ADC下)连接数字和模拟地。

电源线应使用较大的走线以确保低阻抗路径。 去耦是必要的; 请遵循电源规则和旁路部分中列出的准则。

(7)射频干扰

(8)驱动模数转换器(ADC)

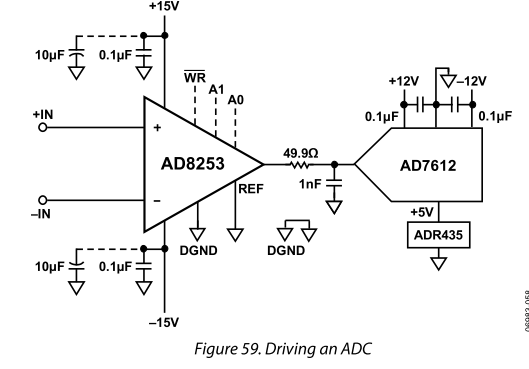

仪表放大器通常用于模数转换器的前面,以提供CMRR。 通常,仪表放大器需要缓冲器来驱动ADC。 但是,AD8253的低输出噪声,低失真和低建立时间使其成为出色的ADC驱动器。

在本示例中,一个1 nF电容和一个49.9Ω电阻为AD7612创建了抗混叠滤波器。 1 nF电容器还用于存储必要的电荷,并将其输送到ADC的开关电容器输入。 49.9串联电阻可减轻放大器的1 nF负载负担,并将其与从AD7612的开关电容输入注入的反冲电流隔离。 选择太小的电阻器可以改善AD8253的输出电压与AD7612(一种ADC)的输入电压之间的相关性,但可能会使AD8253不稳定。 必须在选择足够小以保持精度的电阻和足够大以保持稳定性的电阻之间进行权衡。

4.应用信息

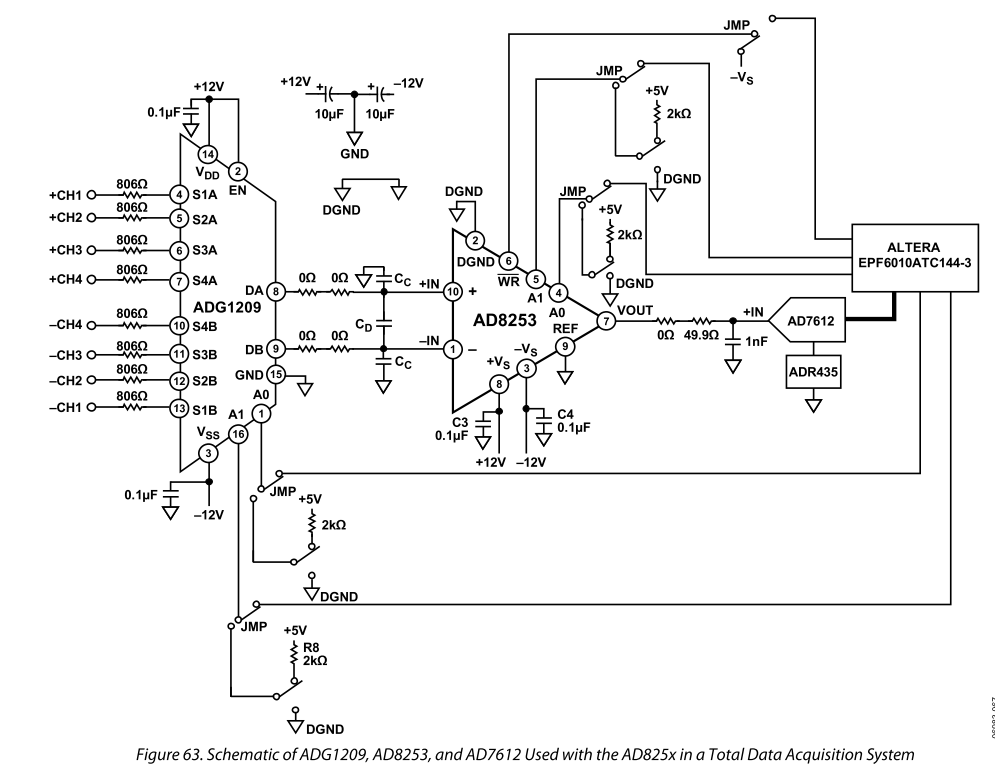

5.数据采集

AD8253是一款出色的仪表放大器,适用于数据采集系统。 其宽带宽,低失真,低建立时间和低噪声使其能够在各种16位ADC之前调节信号。

图63显示了AD825x作为整个数据采集系统的一部分。 AD8253的快速压摆率使其可以调节来自多路复用输入的快速变化的信号。 FPGA控制AD7612,AD8253和ADG1209。 此外,在透明增益模式下,机械开关和跳线使用户可以固定增益。 如图62所示,该系统在1 kHz时可获得−116 dB的THD,信噪比为91 dB。