转:SATA协议简介

SATA协议简介

1、概述

本文档主要介绍SATA的发展历程以及SATA相关协议,为后续SATA驱动框架分析做基础知识准备。

2、SATA简介

2.1 SATA发展历程

2.1.1 PATA硬盘

PATA硬盘叫做并行ATA硬盘(Parellel ATA)。为了限制其信号放大系统产生的高噪声,常采用高达5V的电压来传输正常信号,但是采用大电压导致生产成本上升,同时也不利于高速传输系统的设计和制造。由于数据是并列传输所以它的传输速率受到并行限制,故总体传输率最快能达到133MB/s。

2.1.2 SATA硬盘

SATA硬盘,即SATA(Serial ATA)又被称为串口硬盘。SATA采用差分信号系统,该系统能有效将噪声滤除,因此SATA就不需要使用高电压传输去抑制噪声,只需要使用低电压操作即可。

在数据传输这一方面,SATA的速度比PATA更加快捷,并支持热插拔。另一方面,SATA总线使用了嵌入式时钟频率信号,具备了比以往更强的纠错能力,能对传输指令(不仅是数据)进行检查,如果发现错误会自动矫正,提高了数据传输的可靠性。不过,SATA和PATA最明显的分别,是用上了较细的排线,有利机箱内部的空气流通,某程度上增加了整个平台的稳定性。

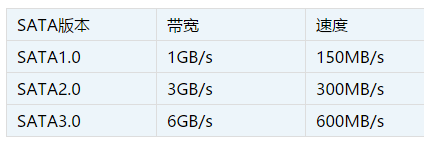

目前SATA接口主要有SATA1.0、SATA2.0、SATA3.0这三个版本,三种主流规范的带宽与传输速度的对比如图 2.1所示。

图 2.1 SATA传输速度对比

SATA是用来取代大容量存储设备并行ATA链接方式的高速串行链接方式。

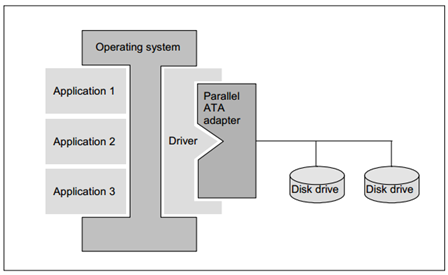

对于并行ATA设备,多个设备通过主/从(master/slave)通信技术链接到并行ATA总线上,其链接方式如图 2.2所示。

图 2.2 PATA拓扑结构

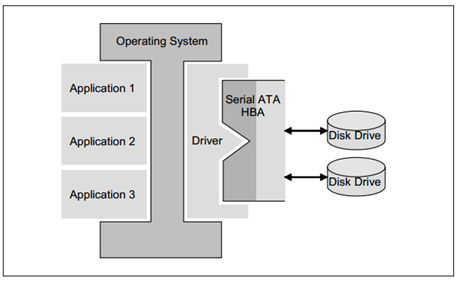

而SATA的拓扑结构是点对点式的,主机可以通过多个链接支持多个设备,每个设备百分百占用总线带宽,并且一个设备的链接出错不会影响其他设备的链接,其链接方式如图 2.3所示。

图 2.3 SATA拓扑结构

2.2.1 SATA接口结构

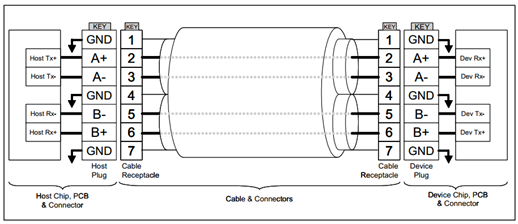

SATA接口使用4根电缆传输数据,其结构图如图 2.4所示。Tx+、Tx-表示输出差分数据线,对应的,Rx+、Rx-表示输入差分数据线。

图 2.4 SATA接口结构图

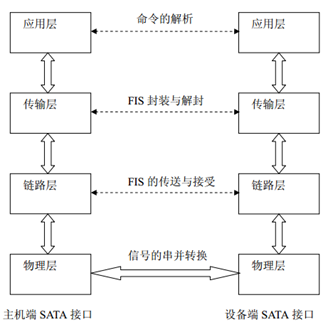

SATA接口协议借鉴TCP/IP模型,将SATA接口划分为四个层次来实现,包括物理层、链路层、传输层、应用层,其体系结构如图 2.5所示。

图 2.5 SATA体系结构

物理层采用全双工串行传输方式,主要功能是进行信号的串并及并串转化。物理层接收来自链路层的数据信息,将接收到的并行的数字逻辑信号转换为串行的差分物理信号,发送到主机端。相应的物理层能将来自主机端的串行差分物理信号转化为并行的逻辑信号传送到链路层。

为了提高 SATA 接口的扩展能力和响应能力, SATA 协议还引进了带外信号(Out Of Band,OOB)来协助物理层进行上电初始化以及复位操作。

2.2.4 链路层分析

链路层的主要功能是通过控制原语的传递来控制信息帧的整个传输过程,保证帧信息能够正确的发送与接收并能进行流量的控制,防止数据发送过快或接受过多。

1)接收来自物理层的信息,对信息帧进行编码、解码、校验和扰码,然后给传输层发送 SOF 原语,通知传输层接收数据,当数据发送完成后,给传输层发送EOF原语,通知传输层该帧传输完成。

2)接收来自传输层的信息,给接收的信息头封装上SOF原语和EOF原语,然后对信息帧进行编码、解码、校验、扰码,传送给物理层。

链路层的控制原语是用来控制和维持串行链路数据传输状态。它们是以32位数据为单位的信息包,控制原语一共有18种,它们都有各自的功能,如:ALIGN原语用来做物理层中数据对齐;SOF、EOF原语用来做数据传输时信息帧的边界定义等。

2.2.5 传输层分析

传输层主要负责FIS帧信息结构的封装与解封。

1)传输层接收到来自应用层的数据传输操作请求后,将相关寄存器中信息按SATA协议规定的标准格式封装为FIS传递给链路层。当链路层正确接收完成后,能给传输层反馈成功完成本次传输的信号。

2)传输层接收到来自链路层的SOF信号后,能接收FIS信息帧,并能判断该FIS的类型,根据FIS类型,判断该FIS是否是有效的FIS。如果是则将该FIS中的命令和数据等按照SATA协议规定进行解析,映射到各个寄存器中,然后能通知应用层接收相应寄存器的值。如果该FIS无效,则丢弃。

2.2.6 应用层分析

应用层能够进行接受来自主机端的命令,根据命令的要求将自身的信息发送给主机端,或是接收来自主机端的以PIO或DMA方式传输的数据,同时写入闪存中,也能从闪存中以PIO或DMA的方式读出数据,传送给主机端。

在应用层采用两个FIFO对数据进行缓冲,一个为读FIFO,一个为写FIFO。应用层能接收来自传输层的数据帧送入写FIFO中或将来自总线的数据保存在读FIFO中,然后通知传输层构造数据帧。

3、参考资料

1、《Serial ATA Revision 3.0