Cadence 16.6 —— 差分对约束 Differential Pair

差分对约束 Differential Pair:差分对约束在PCB走向时,往往对差分对走线阻抗有一定的要求,影响差分对阻抗的因素主要有:线宽、线距、介质介电常数,板层厚度等,PCB走线时能调整的只有线宽和线距。

差分对的约束设置有两种方法:一种是在Electrical规则中设置;一种是在Physical规则中设置。

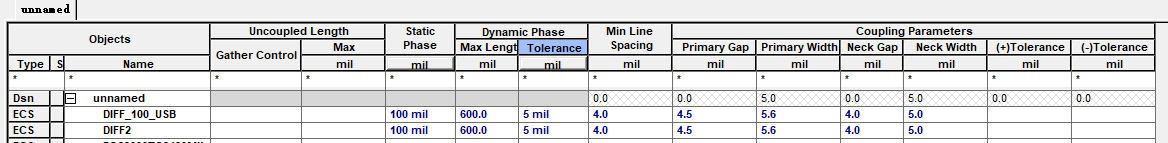

1. 在Electrical规则中设置差分对

设置方法:Electrical Constraint Set - Routing - Differential Pair 中设置电气规则,并在Electrical - Net - Routing - Differential Pair将规则应用到一个差分对上。

Static Phase:静态相位,差分对两根线的总线长误差范围在100mil以内。

Dynamic Phase - Max Length/Tolerance:动态相位,动态等长,也就是实时等长,即,PCB走线时,差分对的两根线无论在那个位置,都必须满足5mil的等长误差范围,并且在600mil的最大长度范围内将误差补偿回来。在高速PC版走线时,这种静态等长和动态等长的设置很重要

Min Line Spacing:最小线距(线间隙),必须小于等于 Neck Gap - Tolerance,Tolerance=0时,该值<=Neck Gap

Primary Gap:优先默认的线距(线间隙)

Primary Width:优先默认的线宽

Neck Gap:Neck 模式下的线距(线间隙)

Neck Width:Neck 模式下的线宽

Tolerance:差分对有阻抗要求,往往不能有偏差,因此设定为0

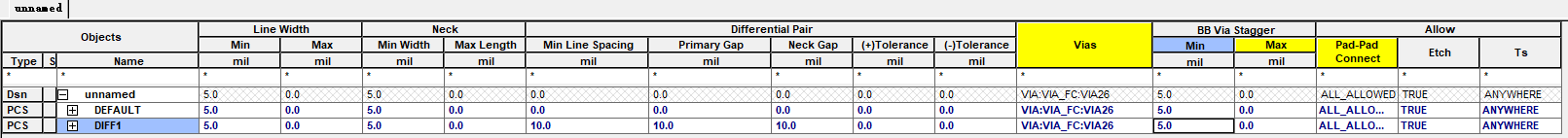

2.在Physical规则中设置差分对

设置方法:Physical Constraint Set - All Layers 中设置规则,在Physical Constraint Set - Net 中应用规则

具体设置方法和 Electrical 中的设置类似,不同的是没有了static Phase 和 Dynamic Phase 的设置。

3.两种方法的比较

Electrical 中设置差分对的参数比较多,对差分对的规则约束更加严格,在高速走线时在 Electrical 中进行规则约束。相对地,在Physical 中的设置就相对较少。

浙公网安备 33010602011771号

浙公网安备 33010602011771号