嵌入式的各种“图”

嵌入式工程识图

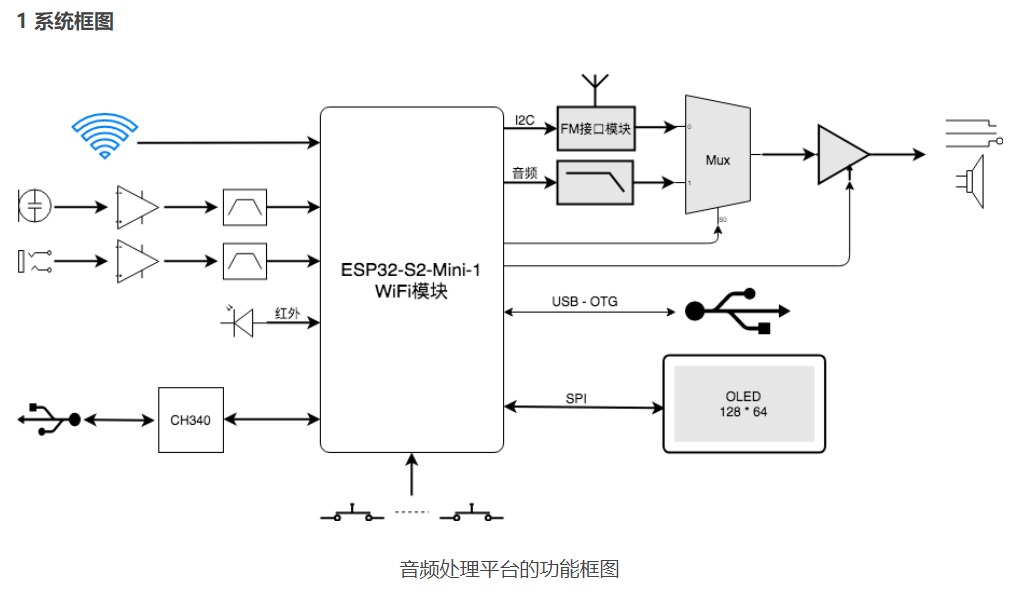

框图

框图框图,顾名思义,就是用一个一个的方框以及线条来表示电路、程序、工艺流程等内在联系。

对于硬件系统来说,一个框图就是一个简单的硬件系统模块。

如上图的OLED模块、FM接口模块、CH340接口模块等。

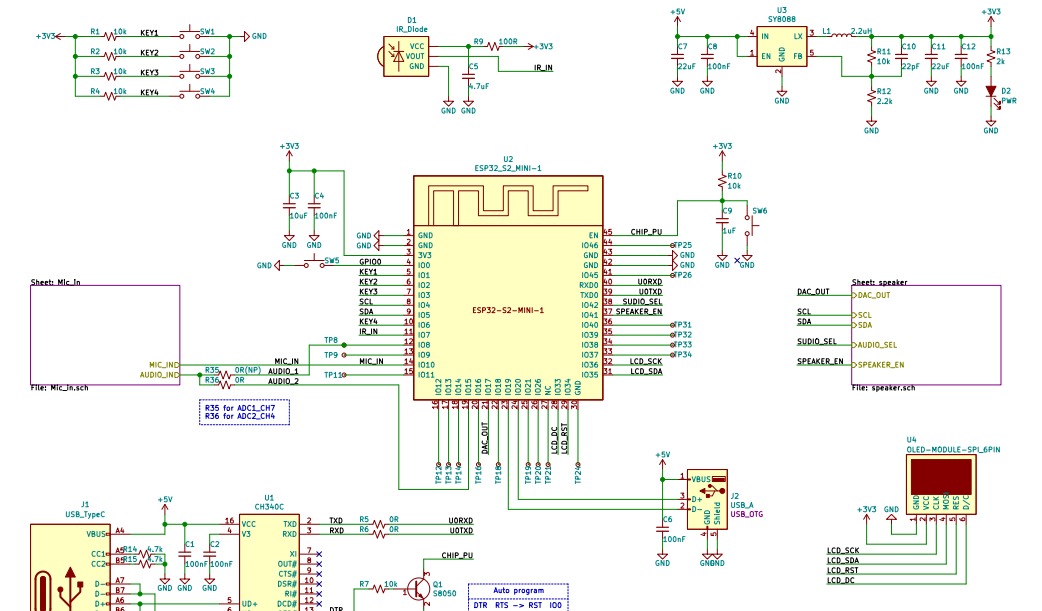

原理图

电路图其实分为两种:电路原理图和印制电路图(PCB)。

电路原理图,简称原理图,用电路元件符号来表示电路连接。

电路元器件的每个引脚都有一个网格标签(net label),如RXD、TXD等,表示引脚的含义,而且同标签名的信号代表要实际链接。

低电平有效表示方法:一种是字符上带画线、一个是字符后面加#、一个是前面加n、一种是再字符前面加/。

等等,还存在这很多的细节。

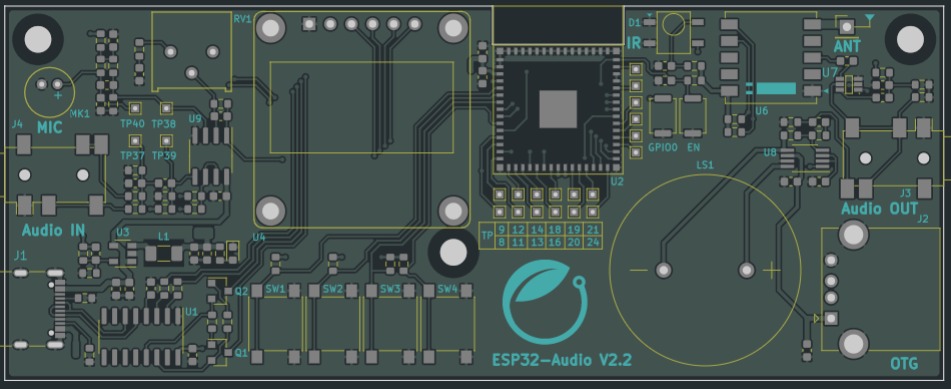

印刷线路图

印刷电路图,就是咱们常说的PCB,很多电子产品里那个绿油油的硬质板子(也有可能是别的颜色),是电子元器件的支撑体,也是电子元器件电气连接的提供者。

印刷电路板的设计都是以电路板为基础的,其中要考虑版图设计、考虑外部连接的布局(各种接口),内部电子元件的优化布局,还要考虑电磁保护、热损耗等种种因素,如果展开说三天三夜也说不完。

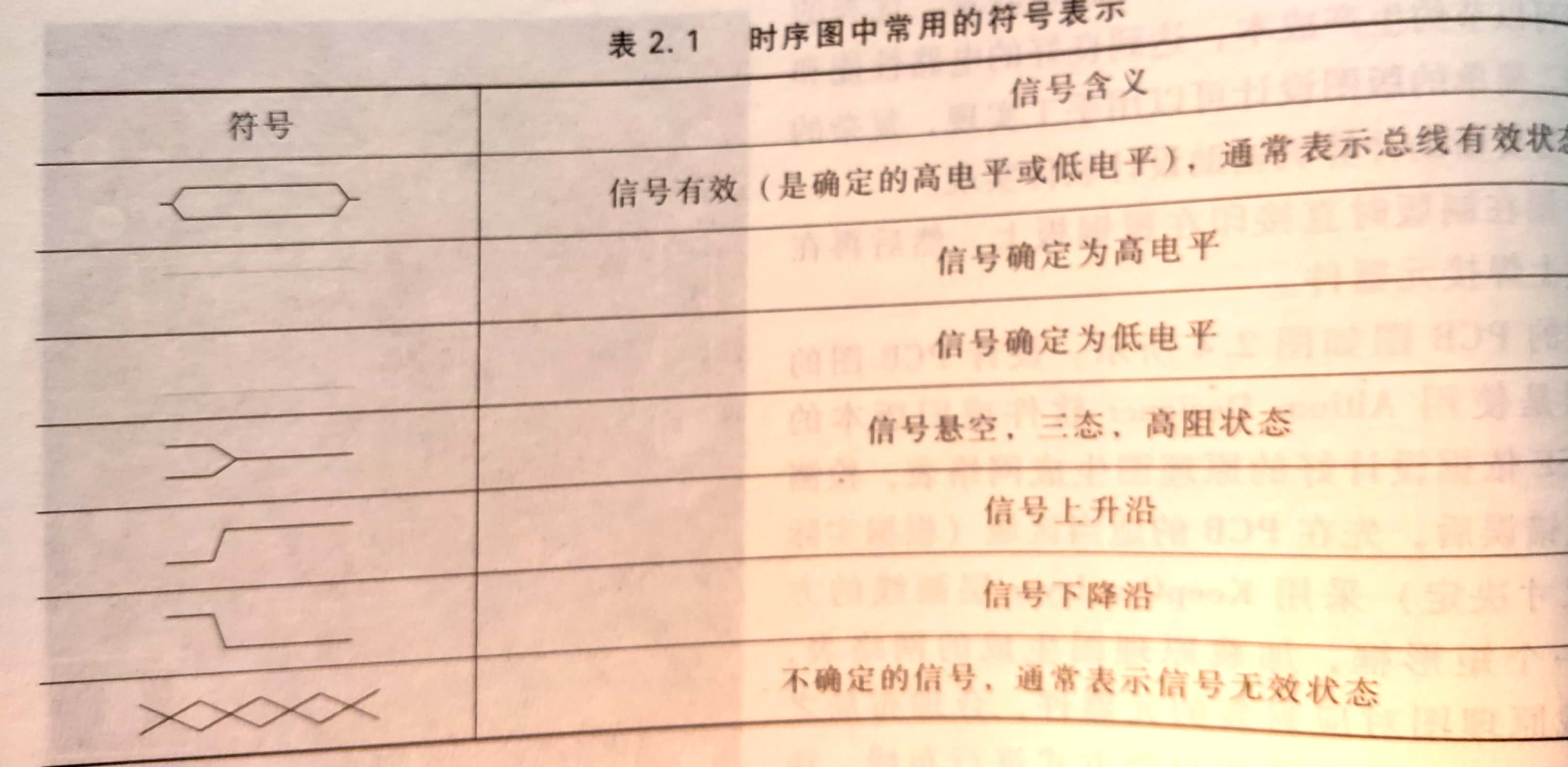

时序图

时序图(sequence diagram),是一种以时间为横轴,在纵轴上表示出信号为0或1的关系。通俗易懂的表示出电路动作状况的图示。

- 时序图从上到下看、从左到右看。

- 时序图最左边一般是某一根引脚的标识,表示此行图线体现该引脚的变化,如RS、R/W、E、DB0~DB7四类引脚的时序变化。

- 有线交叉状的部分,表示电平在变化。

- 两条平行线分别对应高低电平。

- 密封的菱形部分(注意一定注意要密封),表示数据有效,Valid Data这个词也显示了这点。

时序图中常见符号:

示例:

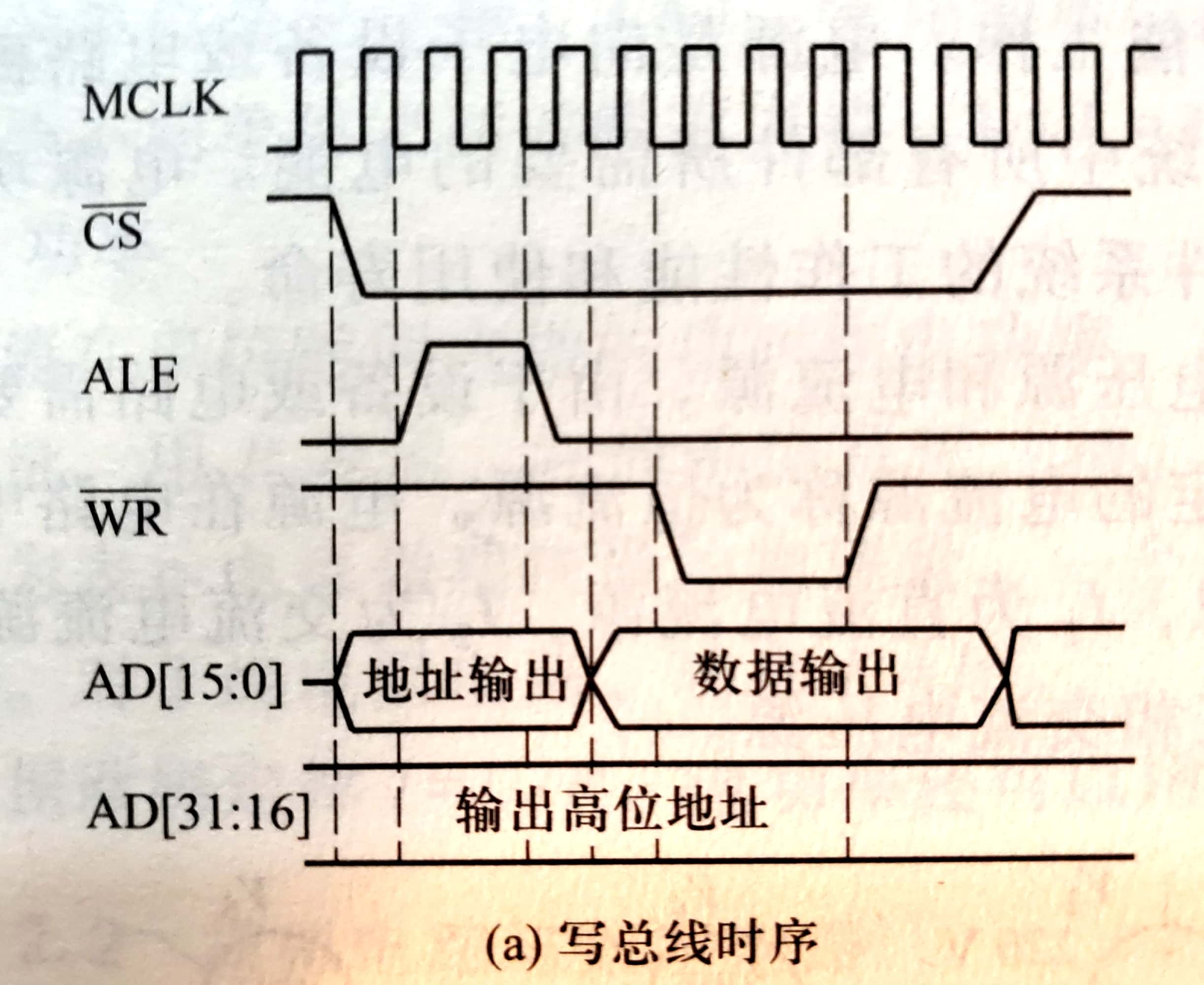

MCLK是总线时钟信号、CS为片选信号(不会加上划线,下同)、WR为写操作信号、ALE为地址锁存允许信号、AD表示地址线与数据线合用。

在片选信号CS低电平有效时,总线地址通过复用的数据线地址线AD[15:0]和高位地址AD[31:16]输出有效地址,再ALE的下降沿,将地址锁存在外接的锁存器,一直在总线操作期间保持不变。