边界扫描的TAP控制器的状态机(空状态机)

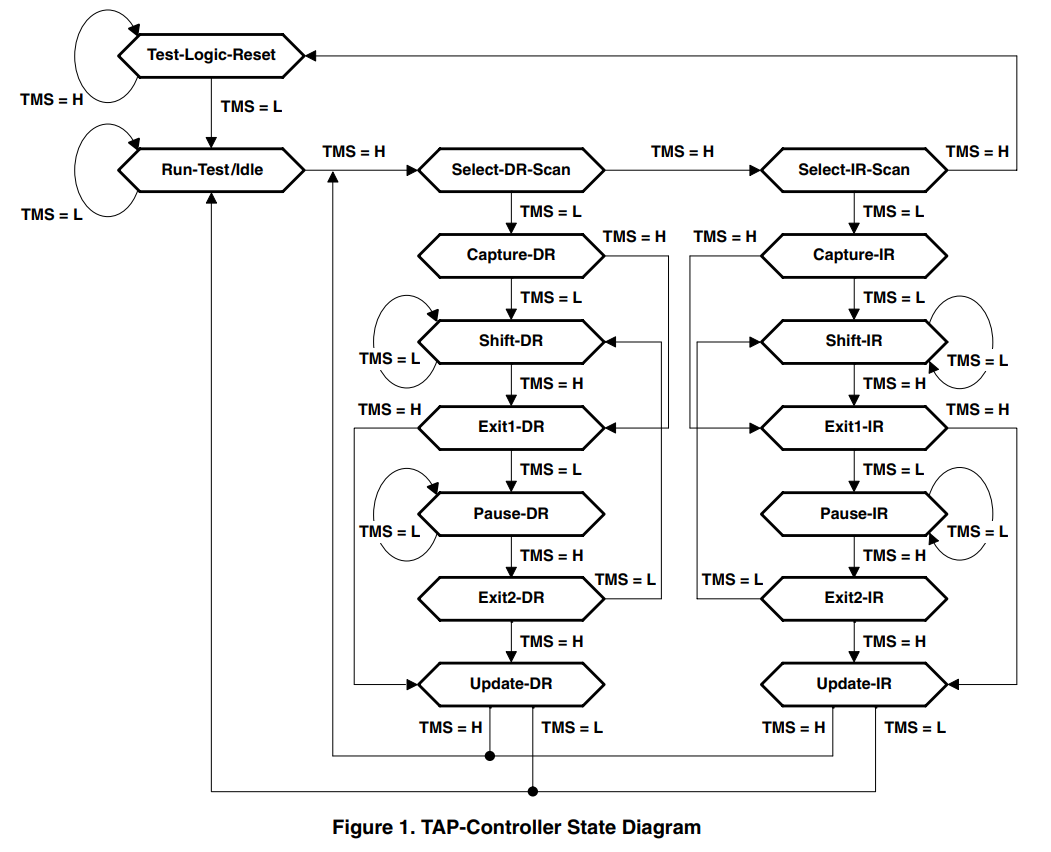

在《边界扫描测试技术及应用》中,介绍了TAP控制器的传统方法,即:

1、对16位状态进行编码,一个触发器有两种状态,16种状态就需要4个触发器。四个触发器的输出就命名为A、B、C、D。那么DBCA的顺序取二进制数字,就可以构成0000到1111这16个状态。

2、状态编码之后,就可以画出状态转化图。状态转化图可以画出真值表,但是真值表通常被省略了。之后,可以画出电路次态的卡诺图,根据卡诺图,可以列写出电路的状态方程。有了状态方程,后续的就都简单了。

在远古时期是没有EDA的,所以这些传统方法如今还在《数字电子技术基础》的书籍中记载着。进入现代社会以后,EDA技术突飞猛进,使用verilog代码的方式获得状态图就简单多了。

1 // 摩尔状态机 2 module tap_exercise 3 ( 4 input logic tck, 5 input logic tms, 6 input logic trst 7 // 其他信号 8 ); 9 10 // TAP的状态机 11 reg [3:0] current_state; 12 reg [3:0] next_state; 13 14 parameter 15 Test_Logic_Rest = 4'b0001, //Idel 16 Run_tese_Idel = 4'b0010, //S1 17 Select_DR_Scan = 4'b0011, //S2 18 Capture_DR = 4'b0100, //S3 19 Shift_DR = 4'b0101, //S4 20 Exit1_DR = 4'b0110, //S5 21 Pause_DR = 4'b0111, //S6 22 Exit2_DR = 4'b1000, //S7 23 Update_DR = 4'b1001, //S8 24 25 Select_IR_Scan = 4'b1010, //S9 26 Capture_IR = 4'b1011, //S10 27 Shift_IR = 4'b1100, //S11 28 Exit1_IR = 4'b1101, //S12 29 Pause_IR = 4'b1110, //S13 30 Exit2_IR = 4'b1111, //S14 31 Update_IR = 4'b0000; //S15 32 33 34 // 输入方程 35 always @ (posedge tck, negedge trst) 36 begin 37 if(trst == 0) 38 current_state <= Test_Logic_Rest; 39 else 40 current_state <= next_state; 41 end 42 43 // 状态方程 44 always @ (tms, current_state) 45 begin 46 case (current_state) 47 Test_Logic_Rest: 48 begin 49 // Test_Logic_Rest 状态下信号处理 50 if(tms) next_state <= Test_Logic_Rest; 51 else next_state <= Run_tese_Idel; 52 end 53 54 Run_tese_Idel: 55 begin 56 // Run_tese_Idel 状态下信号处理 57 if(tms) next_state <= Select_DR_Scan; 58 else next_state <= Run_tese_Idel; 59 end 60 61 Select_DR_Scan: 62 begin 63 // Select_DR_Scan 状态下信号处理 64 if(tms) next_state <= Select_IR_Scan; 65 else next_state <= Capture_DR; 66 end 67 68 Capture_DR: 69 begin 70 // Capture_DR 状态下信号处理 71 if(tms) next_state <= Exit1_DR; 72 else next_state <= Shift_DR; 73 end 74 75 Shift_DR: 76 begin 77 // Shift_DR 状态下信号处理 78 if(tms) next_state <= Exit1_DR; 79 else next_state <= Shift_DR; 80 end 81 82 Exit1_DR: 83 begin 84 // Exit1_DR 状态下信号处理 85 if(tms) next_state <= Update_DR; 86 else next_state <= Pause_DR; 87 end 88 89 Pause_DR: 90 begin 91 // Pause_DR 状态下信号处理 92 if(tms) next_state <= Exit2_DR; 93 else next_state <= Pause_DR; 94 end 95 96 Exit2_DR: 97 begin 98 // 状态下信号处理 99 if(tms) next_state <= Update_DR; 100 else next_state <= Select_DR_Scan; 101 end 102 103 Update_DR: 104 begin 105 // Update_DR 状态下信号处理 106 if(tms) next_state <= Select_DR_Scan; 107 else next_state <= Run_tese_Idel; 108 end 109 110 Select_IR_Scan: 111 begin 112 // Select_IR_Scan 状态下信号处理 113 if(tms) next_state <= Test_Logic_Rest; 114 else next_state <= Capture_IR; 115 end 116 117 Capture_IR: 118 begin 119 // Capture_IR 状态下信号处理 120 if(tms) next_state <= Exit1_IR; 121 else next_state <= Shift_IR; 122 end 123 124 Shift_IR: 125 begin 126 // Shift_IR 状态下信号处理 127 if(tms) next_state <= Exit1_IR; 128 else next_state <= Shift_IR; 129 end 130 131 Exit1_IR: 132 begin 133 // Exit1_IR 状态下信号处理 134 if(tms) next_state <= Update_IR; 135 else next_state <= Pause_IR; 136 end 137 138 Pause_IR: 139 begin 140 // Pause_IR 状态下信号处理 141 if(tms) next_state <= Exit2_IR; 142 else next_state <= Pause_IR; 143 end 144 145 Exit2_IR: 146 begin 147 // Exit2_IR 状态下信号处理 148 if(tms) next_state <= Update_IR; 149 else next_state <= Shift_IR; 150 end 151 152 Update_IR: 153 begin 154 // Update_IR 状态下信号处理 155 if(tms) next_state <= Select_DR_Scan; 156 else next_state <= Run_tese_Idel; 157 end 158 159 default: next_state <= Test_Logic_Rest; 160 endcase 161 end 162 endmodule

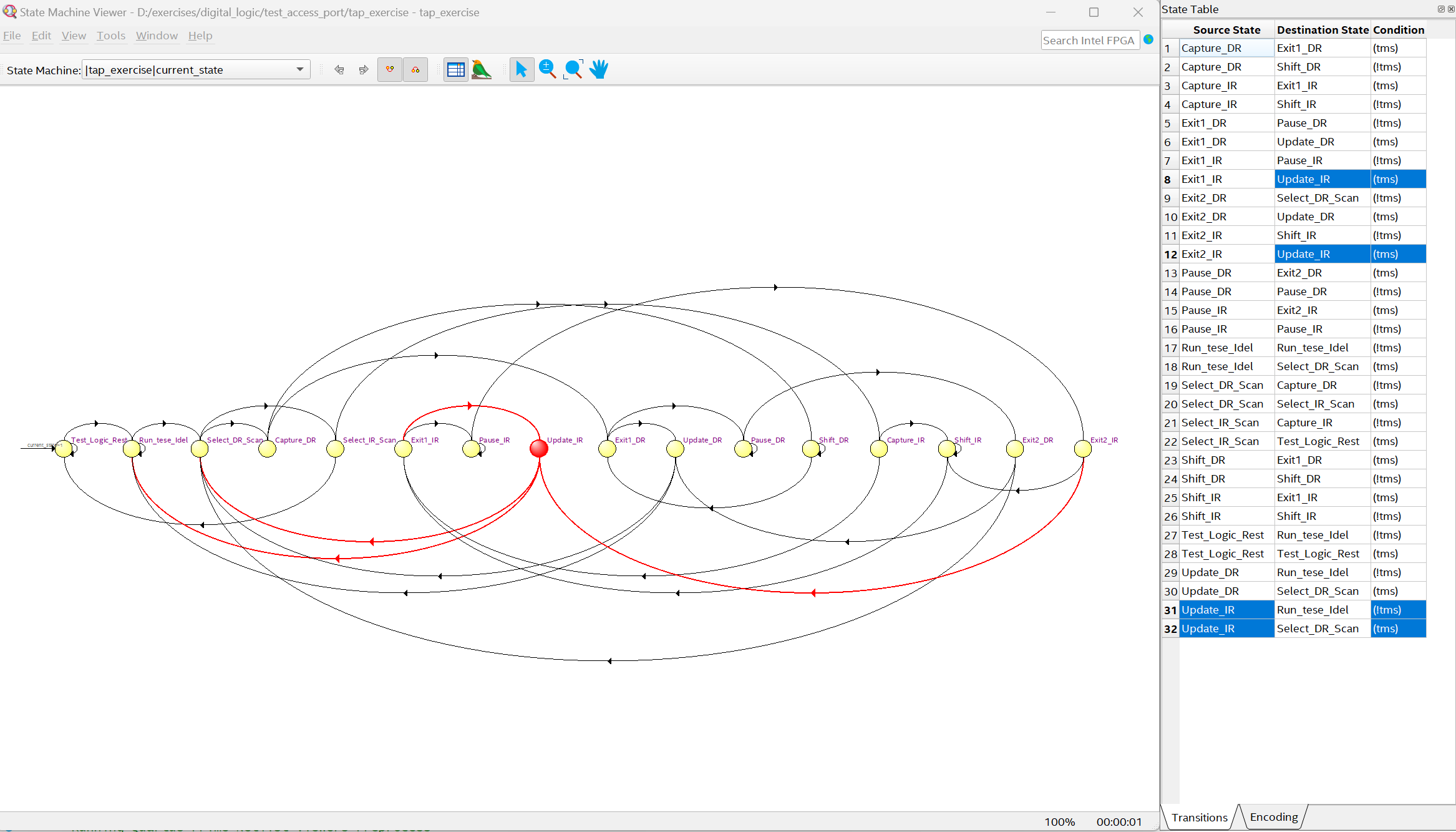

在EDA软件里,还能看到状态图:

最近学习了verilog,顺带使用一些简单的systemverilog,作为练习,就重新温习了一下以前看不太懂的一些需要HDL基础的书籍,把书中的代码,写出来看看。

浙公网安备 33010602011771号

浙公网安备 33010602011771号