每天都有一点新发现:Questa的Verilog仿真

在自己的电脑里安装了Questa Intel Starter和ModelSim Starter版本,因为不熟悉Questa,但是搜索了一下,发现它和ModelSim几乎是完全一样的。准备后续尽可能多的练习Questa的使用。

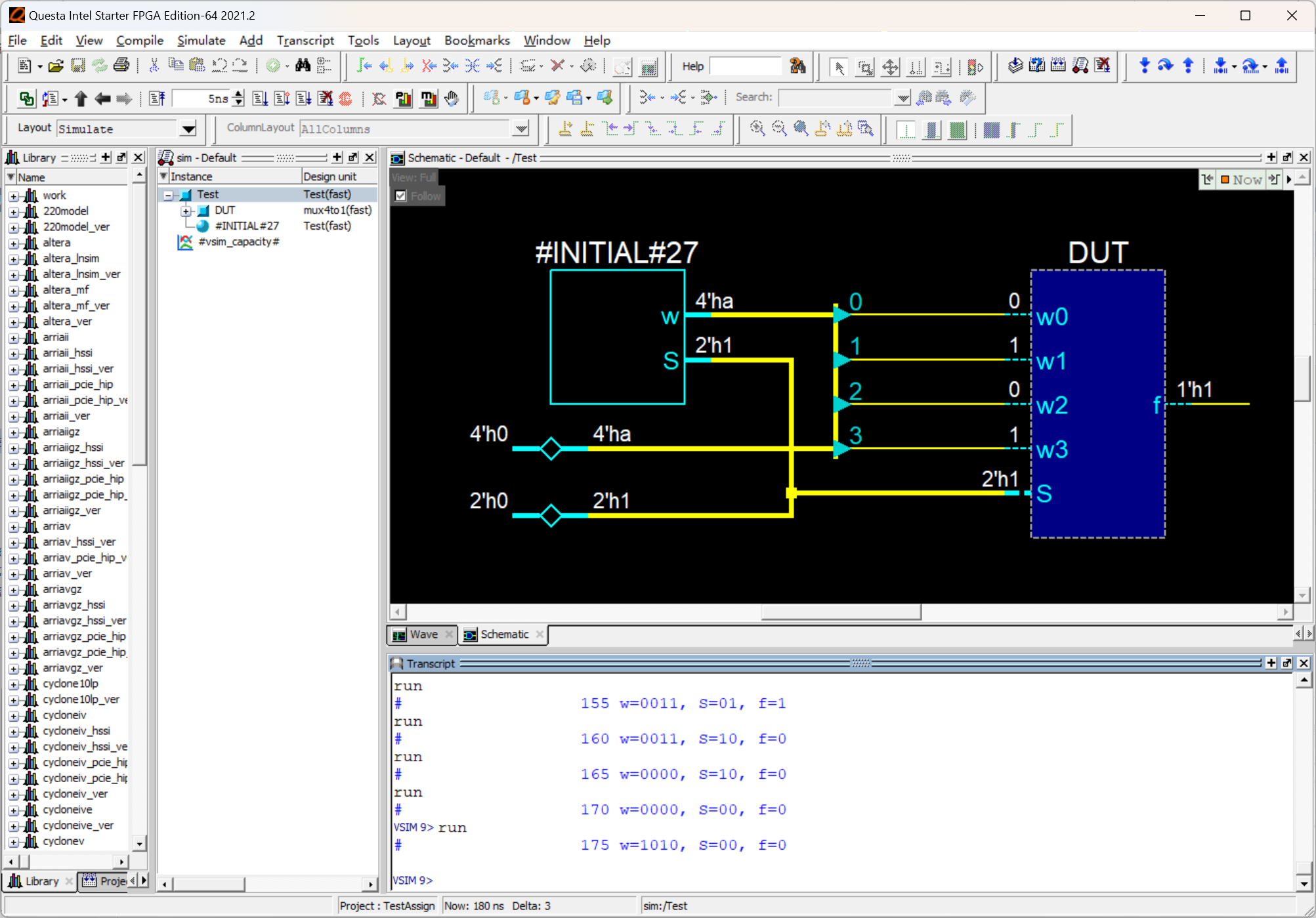

在Verilog里很多教材都会提供代码和生成的电路,今早用Questa试了一下生成的电路,电路如下:

忽然才发现,电路中的信号,是随着仿真变化的,非常直观。我把run的时间步长改成和内部的testbench的步进时间一样,进行仿真的时候,就像看着代码执行一样。嗯,有种当年调试单片机的感觉,每执行一行,看看各个寄存器的变化。

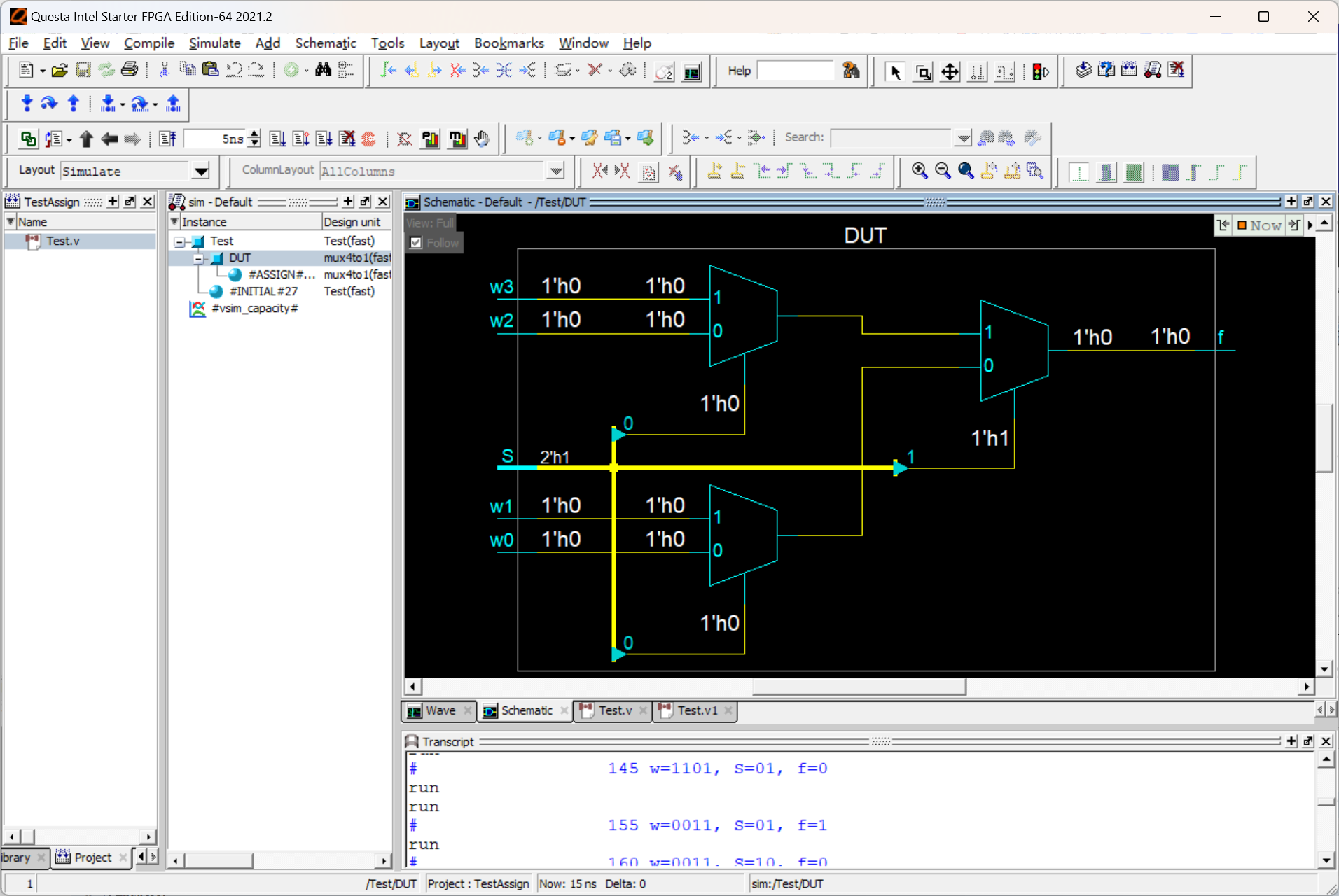

还可以查看下一层模块,不过不知道是不是我设置的不对,还是操作不对,虽然可以查下一层模块的代码,但是并没有完全不同步的显示激励数据和输出数据的变化。如果单纯的想看逻辑图,没有LogSim直观。

学习数字电路,买块开发板,写写代码,编译一下,下载烧录,然后就可以看到和仿真一样的效果。而模拟电路,无论仿真多么完美,想看实物效果,必须得画PCB,买各种元件,制作PCBA,测试调试,还得解决各种供电问题,想看实物波形还得配合示波器。相比之下,数字电路的学习成本真的很低,一个开发板的价格,便宜的和万用表差不多,贵的和示波器差不多。数字开发板的供电,可以用电脑的USB口,也可以买个手机充电器解决。而模拟电路的供电,各种开关电源,偶尔还得自己设计一下电源。在家里搞模拟电路的,一定是真爱;在家里搞数字电路的,可能是加班。

浙公网安备 33010602011771号

浙公网安备 33010602011771号