初级模拟电路:1-2 PN结与二极管

1. 掺杂半导体

上面我们分析了本征半导体的导电情况,但由于本征半导体的导电能力很低,没什么太大用处。所以,一般我们会对本征半导体材料进行掺杂,即使只添加了千分之一的杂质,也足以改变半导体材料的导电特性。通过加入不同特性的掺杂的元素,可以做出两种不同性质的半导体材料:n型半导体材料和 p型半导体材料,下面分别予以介绍。

(1) n型半导体

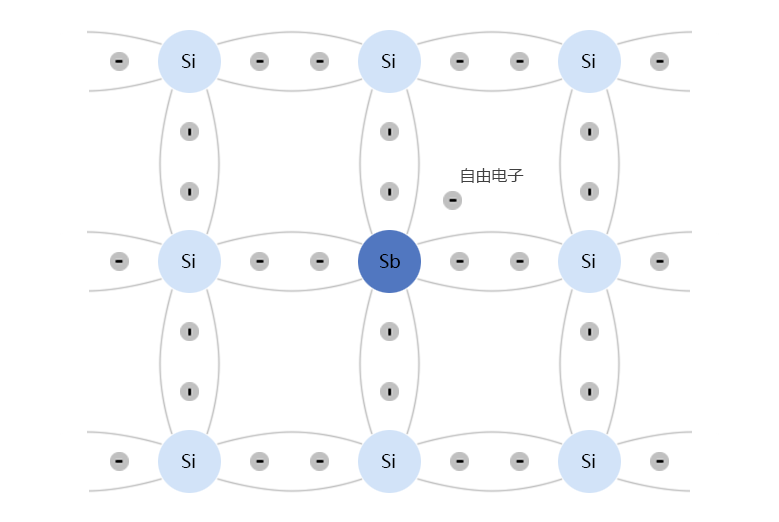

n型半导体材料是通过对本征半导体掺入有5个价电子的元素得到的,常见的5价元素有:锑(Sb)、砷(As)、磷(P),下面以锑作为掺杂元素、硅作为本征基片来举例,见下图所示:

图 1-2.01

在图中我们可以看到,锑的5个价电子中,有4个分别和旁边的硅原子形成了共价键,受到硅原子和锑原子的双重束缚。但是还剩余一个电子没有形成共价键,这个剩余电子本来就处于锑原子的导带和价带之间的重叠地带,所以受锑原子的束缚非常弱,可以在n材料中成为自由电子。这相当于锑原子贡献了一个自由电子,因此这种5价的掺杂原子称为:施主原子(donor atom)。

虽然n型材料中有大量的自由电子,但是n材料中也还是有空穴的,这些空穴由原来的本征硅材料产生,虽然数量非常小,但也不是没有。我们把n材料中的自由电子称为多数载流子(majority carriers),简称多子;而把n型材料中的空穴称为少数载流子(minority carriers),简称少子。

“n”的含义是指,其多数载流子为带负电荷(negtive)的自由电子。需要强调的是,虽然称为n型材料,但材料本身还是中性的,其总正电荷与总负电荷数量相等。

(2) p型半导体

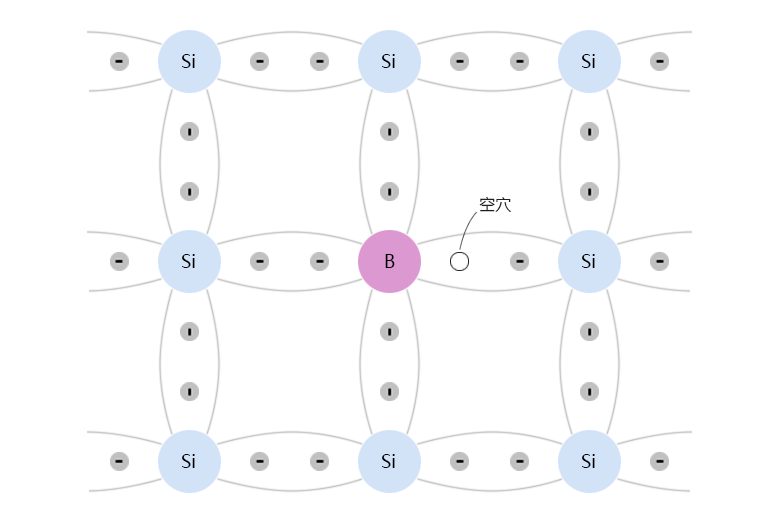

p型半导体材料是通过对本征半导体掺入有3个价电子的元素得到的,常见的3价元素有:铝(Al)、硼(B)、镓(Ga),下面以硼作为硅基片的掺杂元素举例,见下图所示:

图 1-2.02

在图中我们可以看到,由于硼只有3个价电子,导致它和周围的共价键网格中,还缺少1个电子,因此留下一个空穴,这个空位可以方便地接受一个自由电子。这种3价的掺杂原子称为:受主原子(acceptor atom)。

同样的,p型材料中虽然有大量的空穴,但也还是有少量的自由电子的,这些自由电子由原来的本征硅材料产生。所以在p型材料中的多数载流子为空穴,而少数载流子为自由电子。

“p”的含义是指,其多数载流子为带正电荷(positive)的空穴。仍然需要强调的是,虽然称为p型材料,但材料本身还是中性的,其总正电荷与总负电荷数量相等。

2. PN结

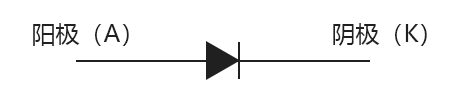

在一块本征硅材料上掺杂,让其一半形成n型材料,另一半型成p型材料,则在交界处会形成一个称为PN结(p-n junction)的结构。这就是一个基本的二极管(diode)。二极管的符号见下图:

图 1-2.03

其中,阳极(Anode)和阴极(Kathode)这两个名词是从更古老的电子管时代遗留下来的(是的,电子管时代就有二极管了),对于现代的晶体管结构二极管,似乎叫P级和N级更合适一些,不过既然已经约定俗称这么叫了,就这么叫吧。

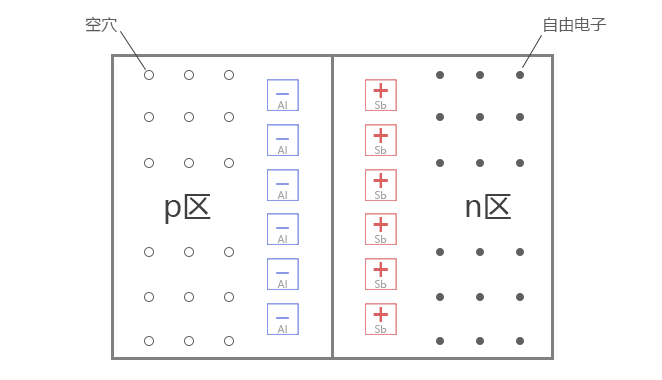

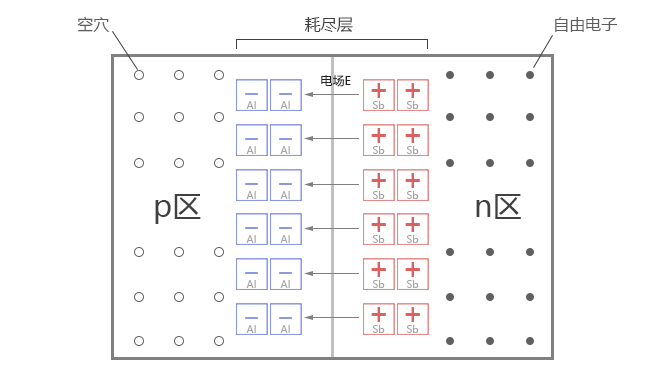

(1) 耗尽层

在p区和n区的交界面附近,处于n区的导带的自由电子,由于热扩散的作用,会有一部分进入到p区,由于p区存在大量的空穴,这些扩散过来的自由电子会很容易与p区的空穴复合。由此产生两个影响:

① 在n区,由于5价的掺杂原子失去了一个电子,因此变成了一个带正电的离子;② 在p区,由于3价的掺杂原子捕获了电子,因此变成了一个带负电的离子,如下图所示(固体中的离子是不能动的,所以图中画成了方形):

图 1-2.04

同样的,处于p区的空穴,由于热扩散的作用,也会有一部分进入到n区,并且与n区的自由电子结合(这里再次声明一下,空穴移动的本质,是价带电子在空穴间移动造成的,但我们将空穴看成为一种带“正电荷”的移动粒子,分析起来会比较方便)。

空穴从p区扩散到n区,同样会产生两个影响:在p区的3价掺杂原子失去一个空穴(失去一个空穴可以理解为失去一个“正电荷”),而变为一个带负电的离子;在n区的某原子获得一个空穴(n区的5价原子和硅原子都可以获得空穴),而变为一个带正电的离子。

可以看到,无论是自由电子的扩散还是空穴的扩散,都会使p区的负离子越来越多,而n区的正离子越来越多。

当这些离子越积越多后,会在pn结附近形成一个内建电场E,如下图所示:

图 1-2.05

而这个内建电场会产生一种阻力,阻碍上面的扩散运动,也阻碍电场自身继续变得更强,这个分析稍微有点复杂。有8种情况要讨论,我们这里仅分析n区的4种情况(p区的4种情况类似,只是方向相反)。

(1) n区电场外部的自由电子,会由于扩散作用而进入电场,当它们一旦进入这个电场,都要受到一个反方向的电场力,使得它们弹回去,不再能轻易到达对面的p区,这个效果阻碍n区的自由电子扩散到p区。(但也不是没有,只有那些动能极高的自由电子,才能穿过电场,到达对面的p区,只不过数量极少)。

(2) n区电场内部的自由电子,其中的大多数自由电子已扩散到p区,并与p区的空穴复合形成了负离子。一旦与p区的空穴结合后,就回不来了,所以在电场内部的n区基本没有自由电子。

(3) n区电场外部的空穴(硅材料原生的,很少),一旦进入这个电场,会受到电场力的作用,加速进入p区,接着与p区的负离子复合,削减电场强度。

(4) n区电场内部的空穴(主要是p区扩散过来的),过来的空穴基本上都已经与n区的自由电子结合,形成了正离子。所以在电场内部的n区也没有空穴。

(5)~(8) p区的情况也是类似,读者可自行推演。

其实,即便你不想烧脑去搞清楚上面(1)~(8)的情况也没关系,只要记住下面2个结论就行了:

● 在pn结的内建电场区域中,既没有自由电子,也没有空穴,所以这个区域称为耗尽层(depletion region)。

● 自由电子和空穴的扩散运动使内建电场增强,而这个内建电场反过来会阻碍扩散运动的继续进行(同时也阻碍电场自己变得更强)。最后两者会达到一个平衡状态,在耗尽层形成一个平衡的电场,进而产生内建电势差,这个电势差也被称为势垒电压(barrier voltage)。在室温下,一般硅基材料的势垒电压大约为0.7V,锗基为0.3V。

(2) PN结反偏

如果把一个外部电压源加到PN结上,使电源正极连接n型材料,电源负极连接p型材料,如下图所示,这种接法称为反向偏置(reverse-bias)。

图 1-2.06

分析时,电源的正极和负极可以看成这样一种抽象:电源正极有吸引电子和排斥空穴的趋势,并可以无限量接收电子和提供空穴;电源负极有吸引空穴和排斥电子的趋势,并可以无限量接收空穴和提供电子。

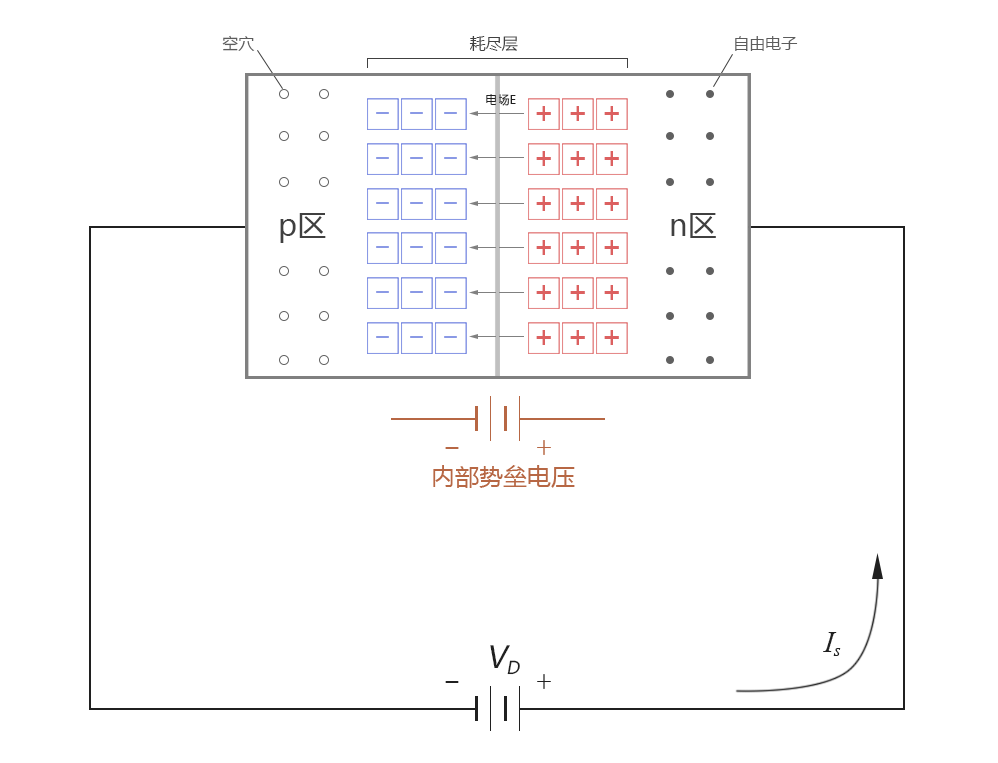

先来分析多数载流子的情况,电源正极吸引n区中的自由电子,从而使得n区产生更多的正离子;而电源负极吸引p区中的空穴,从而使得p区产生更多的负离子;进而使得耗尽层的内建电场和势垒电压变得更大,如下图所示:

图 1-2.07

直到最后内部的势垒电压等于外加的反偏电压,此时,电源正极无法再从n区吸收到自由电子,而电源负极也无法再从p区吸收到空穴,两者达到一种平衡。此时多子流减为0。

然后再考虑少数载流子的情况:在p区的耗尽层外部会有一些极少量的自由电子,它们被电源负极排斥而进入PN结内建电场,然后被内建电场加速而推到n区,最后穿过n区被电源正极吸收;而电源的负极会补给新的自由电子到p区,如此形成持续的少子电流。在n区的少子“空穴”的情况也是类似(在n区的少子空穴,被电源正极排斥而进入并且穿过内建电场,最后被电源负极吸收)。但是由于少子的总数非常小,因此这个少子电流非常微弱(一般在几个微安左右)。

这个在反偏电压下的电流称为反向饱和电流(reverse saturation current),用IS表示。饱和的意思是指:随着反偏电压的增大,反偏电流维持不变,不会持续增大。

(3) PN结正偏

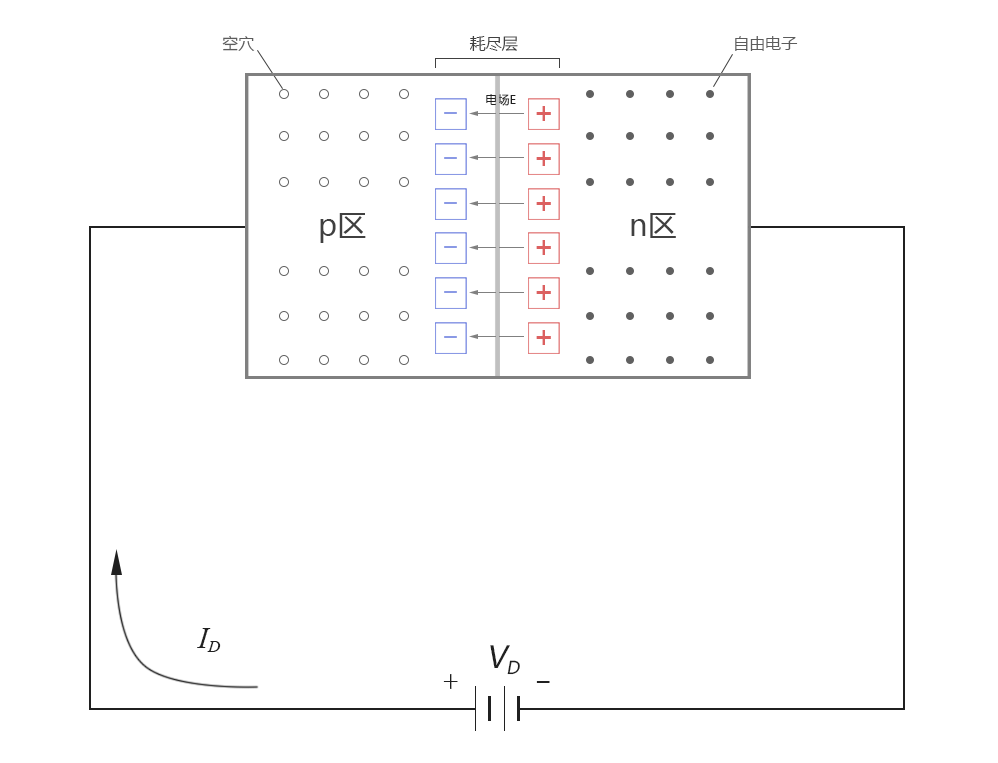

当把外电源的正极接到二极管的p型材料,电源负极接到n型材料,这种接法称为正向偏置(forward-bias),如下图所示:

图 1-2.08

在正偏情况下,p区的空穴被电源正极推向耗尽层,从而与p区耗尽层的一部分负离子复合;同样的,n区的自由电子被电源负极推向耗尽层,从而与n区耗尽层的一部分正离子复合,这样就等于是削弱了耗尽层的内建电场和势垒电压。如下图所示:

图 1-2.09

随着外部电源正偏电压的增大,内建电场不断被削弱,直到外部电压可以克服内部势垒电场时,n区的电子和p区的空穴可有足够的能量进入对方区域,再而流到电源,这将导致电流极快增长,此时称二极管为导通状态,在图中表示为ID。这里有一个比较有趣的问题:自由电子进入p区后如何运动?回答是,自由电子进入p区后,会与价带的空穴复合,然后在价带中沿着空穴一路运动到电源负极。也就是说,在p区运动的多数载流子仍然是空穴。

至于正偏情况下的少子电流,在正偏电压很小时,会有非常微弱的少子电流。但由于少子的总数相当小,与多子电流相比,一般可忽略不记。

(4) 反向击穿

再回来讲反偏。虽然在反偏条件下,反向饱和电流不随反偏电压的增大而增大,但反偏电压也不能太大,当反偏电压过大时,会引起二极管的反向击穿(reverse breakdown)。有2种机制会引起反向击穿,分别是雪崩击穿(avalanche breakdown)和齐纳击穿(Zenor breakdown)。

先讲雪崩击穿。前面在讲反偏的时候讲过,少数载流子在经过耗尽层时,会被内建电场加速一下。当反偏电压越大时,内建电场的势垒电压也越大,给少子的加速也越大,当少子的动能足够大时,它会撞击破坏其他原子的共价键,进而撞击出一个新的“自由电子-空穴”对。这个新的“自由电子-空穴”对,同样会被内建电场加速,再去撞击其他的共价键,最后引起雪崩效应,导致反向电流急剧增大。雪崩击穿会造成二极管的永久损坏,这是必须避免的。生产商通过调节掺杂浓度来控制雪崩电压值,常用二极管的雪崩击穿电压一般在几十伏到几百伏不等。

另一种击穿机制是齐纳击穿。同样是在反偏条件下,在耗尽层的内建强电场会破坏其中原子的结合力,从而强行电离出“电子-空穴”对。一般齐纳电压值比雪崩电压值会低一些,但也不是一定的。对于普通二极管,无论是雪崩击穿还是齐纳击穿,都会造成二极管的永久损坏。所以一般二极管的规格书上不区分两者,统一称为峰值反向电压,简称PIV(peak inverse voltage),也有的厂商把它简写为PRV(peak reverse voltage),或BV(breakdown voltage),在一些教材上也把它写成VBV,都是一个意思。

另外有一种特殊二极管称为齐纳二极管(Zener diode),也叫稳压二极管,它专门可以工作于齐纳击穿电压而不损坏。齐纳二极管是在电子电路中比较常用的一种元器件,通常用于保护线路不被意外的高电压击坏,这个后面我们会单独介绍。

好了,关于半导体与PN结内部的工作原理就解释到这里,以上的内容都只是为了帮助学习者快速理解的一种简化模型,其实半导体材料真正的内部工作机理非常复杂,如果你真的还想刨根问底,可以去看《固体物理》、《半导体器件基础》之类的书,说实话,再深了我也不懂 :)

( end of 1-2 )

浙公网安备 33010602011771号

浙公网安备 33010602011771号