quartus ii综合ram及相关知识备忘

当用verilog写一个memory时,如下:

reg[15:0] datamem[7:0];

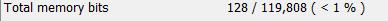

直接综合,并不会用fpga中的memory资源

.png)

需要加上(* ramstyle = "M-RAM" *)才会让quartus将其综合使用ram资源

(*ramstyle = "M-RAM"*)reg[15:0] datamem[7:0];

还可以将M-RAM换成其他字样,使系统使用M4K块之类的,详见

http://quartushelp.altera.com/13.1/mergedProjects/hdl/vlog/vlog_file_dir_ram.htm

///////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

这里的内存模型指的是内存的行为模型。Verilog中提供了两维数组来帮助我们建立内存的行为模型。具体来说,就是可以将内存宣称为一个reg类型的数组,这个数组中的任何一个单元都可以通过一个下标去访问。这样的数组的定义方式如下:

reg [wordsize : 0] array_name [0 : arraysize];

例如:

reg [7:0] my_memory [0:255];

其中 [7:0] 是内存的宽度,而[0:255]则是内存的深度(也就是有多少存储单元),其中宽度为8位,深度为256。地址0对应着数组中的0存储单元。

如果要存储一个值到某个单元中去,可以这样做:

my_memory [address] = data_in;

而如果要从某个单元读出值,可以这么做:

data_out = my_memory [address];

但要是只需要读一位或者多个位,就要麻烦一点,因为Verilog不允许读/写一个位。这时,就需要使用一个变量转换一下:

例如:

data_out = my_memory[address];

data_out_it_0 = data_out[0];

这里首先从一个单元里面读出数据,然后再取出读出的数据的某一位的值。

浙公网安备 33010602011771号

浙公网安备 33010602011771号