[原创]iFPGA-USB2.0 FT2232H USB & UART开发板使用说明

iFPGA-USB2.0 FT2232H USB & UART 开发板使用说明

基本特性:

- 沉金工艺;

- 速度达到30MB/S以上;

- FT2232H USB2.0免固件开发;

- FPGA-USB2.0源码,即拿即用,简化用户设计;

- 框架开发、方便用户扩展;

- 128K Byte SRAM;

- 有源晶振50MHz;

- 40组 User IO扩展;

- 16Mbit Flash;

框图:

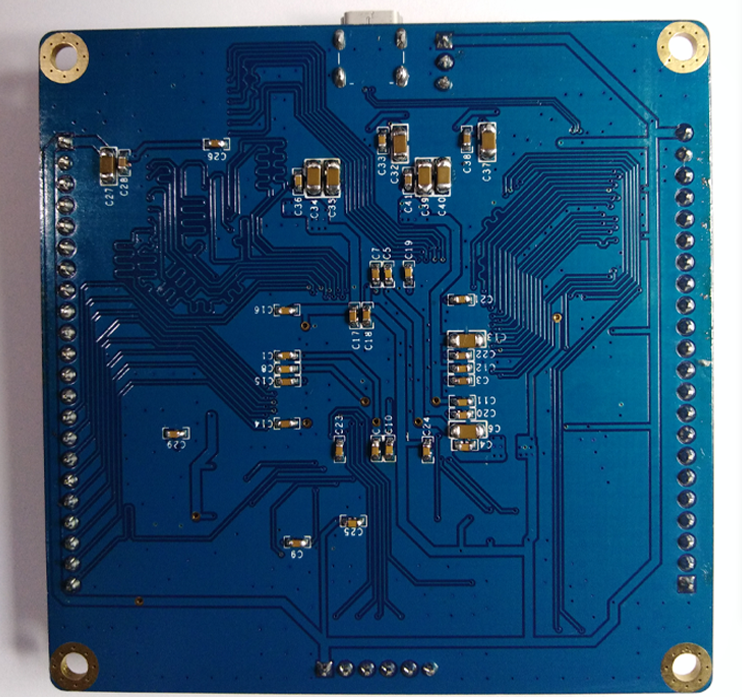

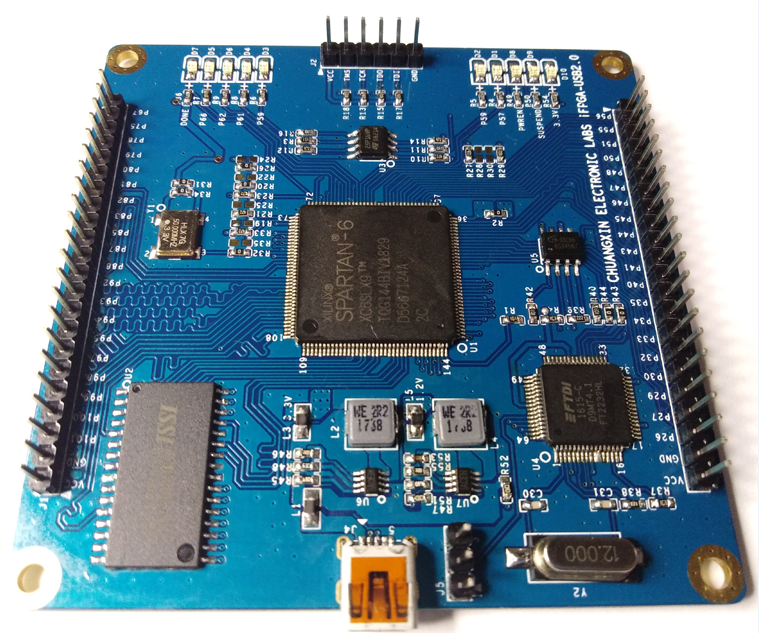

实物图:

管脚约束:

1 NET "FPGA-IO14" LOC = "P82"; 2 NET "FPGA-IO15" LOC = "P81"; 3 NET "FPGA-IO16" LOC = "P80"; 4 NET "FPGA-IO17" LOC = "P79"; 5 NET "FPGA-IO18" LOC = "P78"; 6 NET "FPGA-IO19" LOC = "P75"; 7 NET "SRAM-WE" LOC = "P104"; 8 NET "SRAM-CE" LOC = "P105"; 9 NET "SRAM-OE" LOC = "P102"; 10 NET "FPGA-IO1" LOC = "P101"; 11 NET "FPGA-IO2" LOC = "P100"; 12 NET "FPGA-IO3" LOC = "P99"; 13 NET "FPGA-IO4" LOC = "P98"; 14 NET "FPGA-IO5" LOC = "P97"; 15 NET "FPGA-IO6" LOC = "P95"; 16 NET "SYS-CLK" LOC = "P84"; 17 NET "FPGA-IO7" LOC = "P94"; 18 NET "FPGA-IO8" LOC = "P93"; 19 NET "FPGA-IO9" LOC = "P92"; 20 NET "FPGA-IO10" LOC = "P88"; 21 NET "FPGA-IO11" LOC = "P87"; 22 NET "FPGA-IO12" LOC = "P85"; 23 NET "FPGA-IO13" LOC = "P83"; 24 NET "FPGA_DOUT" LOC = "P74"; 25 NET "FPGA_SUSPEND" LOC = "P73"; 26 NET "JTAG_TDO" LOC = "P106"; 27 NET "JTAG_TMS" LOC = "P107"; 28 NET "JTAG_TCK" LOC = "P109"; 29 NET "JTAG_TDI" LOC = "P110"; 30 NET "FPGA_CMPCS_B" LOC = "P72"; 31 NET "FPGA_DONE" LOC = "P71"; 32 NET "SPI_CLK" LOC = "P70"; 33 NET "FPGA_M0" LOC = "P69"; 34 NET "FPGA-IO20" LOC = "P67"; 35 NET "FPGA-LED1" LOC = "P58"; 36 NET "SPI_MISO" LOC = "P65"; 37 NET "SPI_MOSI" LOC = "P64"; 38 NET "FPGA-LED0" LOC = "P57"; 39 NET "FPGA-LED3" LOC = "P61"; 40 NET "FPGA_M1" LOC = "P60"; 41 NET "FPGA-LED4" LOC = "P62"; 42 NET "FPGA-LED5" LOC = "P66"; 43 NET "FPGA-LED2" LOC = "P59"; 44 NET "FPGA-IO21" LOC = "P56"; 45 NET "FPGA-IO22" LOC = "P55"; 46 NET "FPGA-IO23" LOC = "P51"; 47 NET "FPGA-IO24" LOC = "P50"; 48 NET "FPGA-IO25" LOC = "P48"; 49 NET "FPGA-IO26" LOC = "P47"; 50 NET "FPGA-IO27" LOC = "P46"; 51 NET "FPGA-IO28" LOC = "P45"; 52 NET "FPGA-IO29" LOC = "P44"; 53 NET "FPGA-IO30" LOC = "P43"; 54 NET "FPGA-IO31" LOC = "P41"; 55 NET "FPGA-IO32" LOC = "P40"; 56 NET "FPGA_INIT_B" LOC = "P39"; 57 NET "SPI_CS" LOC = "P38"; 58 NET "FPGA_PROGRAM_B" LOC = "P37"; 59 NET "SRAM-A0" LOC = "P111"; 60 NET "SRAM-A1" LOC = "P112"; 61 NET "SRAM-A2" LOC = "P114"; 62 NET "SRAM-A3" LOC = "P115"; 63 NET "SRAM-A4" LOC = "P124"; 64 NET "SRAM-A5" LOC = "P126"; 65 NET "SRAM-A6" LOC = "P127"; 66 NET "SRAM-A7" LOC = "P131"; 67 NET "SRAM-A8" LOC = "P143"; 68 NET "SRAM-A9" LOC = "P142"; 69 NET "SRAM-A10" LOC = "P141"; 70 NET "SRAM-A11" LOC = "P140"; 71 NET "SRAM-A12" LOC = "P139"; 72 NET "SRAM-A13" LOC = "P132"; 73 NET "SRAM-A14" LOC = "P120"; 74 NET "SRAM-A15" LOC = "P119"; 75 NET "SRAM-A16" LOC = "P118"; 76 NET "SRAM-IO0" LOC = "P116"; 77 NET "SRAM-IO1" LOC = "P117"; 78 NET "SRAM-IO2" LOC = "P121"; 79 NET "SRAM-IO3" LOC = "P123"; 80 NET "SRAM-IO4" LOC = "P138"; 81 NET "SRAM-IO5" LOC = "P137"; 82 NET "SRAM-IO6" LOC = "P134"; 83 NET "SRAM-IO7" LOC = "P133"; 84 NET "FT2232HL-D0" LOC = "P1"; 85 NET "FT2232HL-D1" LOC = "P2"; 86 NET "FT2232HL-D2" LOC = "P5"; 87 NET "FT2232HL-D3" LOC = "P6"; 88 NET "FT2232HL-D4" LOC = "P7"; 89 NET "FT2232HL-D5" LOC = "P8"; 90 NET "FT2232HL-D6" LOC = "P9"; 91 NET "FT2232HL-D7" LOC = "P10"; 92 NET "FT2232HL-RXF" LOC = "P11"; 93 NET "FT2232HL-TXE" LOC = "P12"; 94 NET "FT2232HL-RD" LOC = "P14"; 95 NET "FT2232HL-WR" LOC = "P15"; 96 NET "FT2232HL-SIWUA" LOC = "P16"; 97 NET "FPGA_TXD" LOC = "P24"; 98 NET "FT2232HL-CLKOUT" LOC = "P17"; 99 NET "FT2232HL-OE" LOC = "P22"; 100 NET "FT2232HL-H7" LOC = "P21"; 101 NET "FPGA-IO33" LOC = "P35"; 102 NET "FPGA-IO34" LOC = "P34"; 103 NET "FPGA-IO35" LOC = "P33"; 104 NET "FPGA-IO36" LOC = "P32"; 105 NET "FPGA-IO37" LOC = "P30"; 106 NET "FPGA-IO38" LOC = "P29"; 107 NET "FPGA-IO39" LOC = "P27"; 108 NET "FPGA-IO40" LOC = "P26"; 109 NET "FPGA_RXD" LOC = "P23";

FT2232H配置

1 <?xml version="1.0" encoding="utf-16"?> 2 <FT_EEPROM> 3 <Chip_Details> 4 <Type>FT2232H</Type> 5 </Chip_Details> 6 <USB_Device_Descriptor> 7 <VID_PID>0</VID_PID> 8 <idVendor>0403</idVendor> 9 <idProduct>6010</idProduct> 10 <bcdUSB>USB 2.0</bcdUSB> 11 </USB_Device_Descriptor> 12 <USB_Config_Descriptor> 13 <bmAttributes> 14 <RemoteWakeupEnabled>false</RemoteWakeupEnabled> 15 <SelfPowered>false</SelfPowered> 16 <BusPowered>true</BusPowered> 17 </bmAttributes> 18 <IOpullDown>false</IOpullDown> 19 <MaxPower>500</MaxPower> 20 </USB_Config_Descriptor> 21 <USB_String_Descriptors> 22 <Manufacturer>iFPGA Labs</Manufacturer> 23 <Product_Description>iFPGA USB 2.0</Product_Description> 24 <SerialNumber_Enabled>true</SerialNumber_Enabled> 25 <SerialNumber /> 26 <SerialNumberPrefix>21</SerialNumberPrefix> 27 <SerialNumber_AutoGenerate>true</SerialNumber_AutoGenerate> 28 </USB_String_Descriptors> 29 <Hardware_Specific> 30 <Suspend_DBUS7>false</Suspend_DBUS7> 31 <TPRDRV>0</TPRDRV> 32 <Port_A> 33 <Hardware> 34 <UART>false</UART> 35 <_245FIFO>true</_245FIFO> 36 <CPUFIFO>false</CPUFIFO> 37 <OPTO>false</OPTO> 38 </Hardware> 39 <Driver> 40 <VCP>false</VCP> 41 <D2XX>true</D2XX> 42 </Driver> 43 </Port_A> 44 <Port_B> 45 <Hardware> 46 <UART>true</UART> 47 <_245FIFO>false</_245FIFO> 48 <CPUFIFO>false</CPUFIFO> 49 <OPTO>false</OPTO> 50 </Hardware> 51 <Driver> 52 <VCP>true</VCP> 53 <D2XX>false</D2XX> 54 </Driver> 55 </Port_B> 56 <IO_Pins> 57 <Group_AL> 58 <SlowSlew>false</SlowSlew> 59 <Schmitt>false</Schmitt> 60 <Drive>4mA</Drive> 61 </Group_AL> 62 <Group_AH> 63 <SlowSlew>false</SlowSlew> 64 <Schmitt>false</Schmitt> 65 <Drive>4mA</Drive> 66 </Group_AH> 67 <Group_BL> 68 <SlowSlew>false</SlowSlew> 69 <Schmitt>false</Schmitt> 70 <Drive>4mA</Drive> 71 </Group_BL> 72 <Group_BH> 73 <SlowSlew>false</SlowSlew> 74 <Schmitt>false</Schmitt> 75 <Drive>4mA</Drive> 76 </Group_BH> 77 </IO_Pins> 78 </Hardware_Specific> 79 </FT_EEPROM>

基于FTDI USB2.0测试情况如下

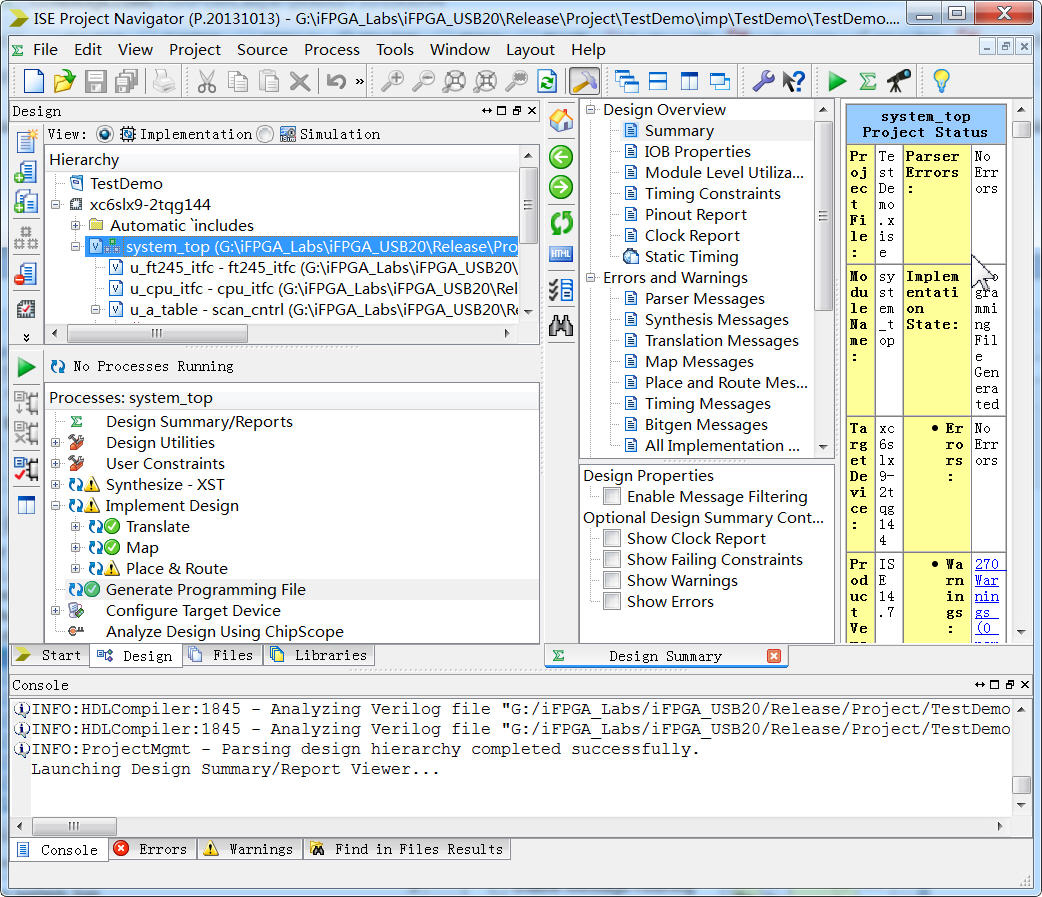

FPGA工程

生成的版本烧写到flash里面

上位机测试界面如下:

原创文章 版权©2021 FPGATopic

欢迎转载 注明出处

交流邮箱:cx_info@163.com

欢迎转载 注明出处

交流邮箱:cx_info@163.com

基本特性:

Channel A: USB2.0接口,速率大30MB/S,免固件开发;

Channel B为UART,或者MPSSE,可以当做串口,或者SPI升级,烧写Flash使用;

基本特性:

Channel A: USB2.0接口,速率大30MB/S,免固件开发;

Channel B为UART,或者MPSSE,可以当做串口,或者SPI升级,烧写Flash使用;

浙公网安备 33010602011771号

浙公网安备 33010602011771号