关键路径与时序优化

关键路径

关键路径通常是指同步逻辑电路中,组合逻辑时延最大的路径(这里我认为还需要加上布线的延迟),也就是说关键路径是对设计性能起决定性影响的时序路径。对关键路径进行时序优化,可以直接提高设计性能。对同步逻辑来说,常用的时序优化方法包括 Pipeline、Retiming、逻辑复制、加法/乘法树、关键信号后移、消除优先级等解决。静态时序分析能够找出逻辑电路的关键路径。通过查看静态时序分析报告,可以确定关键路径。

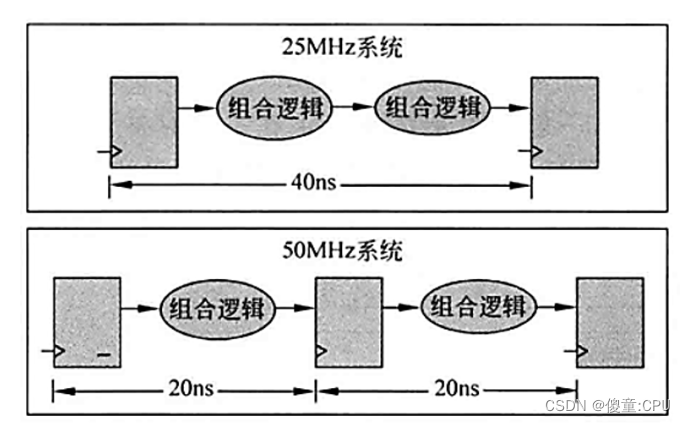

1. 组合逻辑中插入寄存器(插入流水线)

组合逻辑的延时过长,就会成为关键路径,这时可以考虑在该路径上插入额外的寄存器,这种方法也称为插入流水线,多用于高度流水的设计中,因为这种设计中额外插入寄存器增加的时钟周期延时并不会违反整个设计的规范要求,从而不会影响设计的总体功能性实现,也即额外插入的寄存器在保持吞吐量不变的情况下改善了设计的时序性能。当然,其不可避免地会带来部分面积的增加。

2. 寄存器平衡(重定时 Retiming)

在不增加寄存器个数的前提下,通过改变寄存器的位置来优化关键路径,可以对比和流水线插入寄存器的不同。

3. 操作符平衡(加法树、乘法树)

平衡前,a 和 b 均经过 3 个乘法器带来的延时,c 经历 2 个,d 经历 1 个,最长延时为 3 个乘法器延时。平衡后,树形结构,a、b、c、d 均经历 2 个乘法器延时,最长延时为 2 个乘法器延时。

4. 消除代码优先级(case 代替 if…else)

本身确实不需要优先级的地方,可以使用 case 代替 if…else,使得顺序执行的语句编程并行执行。如果确实有优先级兵,则不能这样做。这种消除代码中的优先级的策略也称为代码结构平坦化技术,主要针对那些带优先级的编码结构。

5. 逻辑复制

当某个信号的扇出 fanout 比较大时,会造成该信号到各个目的逻辑节点的路径变得过长,从而成为设计中的关键路径,此时可以通过对该信号进行复制来降低扇出。高扇出的危害是大大增加了布局布线的难度,这样其扇出的节点也就无法被布局得彼此靠近,所以就导致了布线长度过大的问题。

6. 关键信号后移

关键输入应该在逻辑最后一级提供,其中关键输入为芯片、Slice、或者 LUT 提供的时延最大的输入,比如在 if…else if…链中,将关键信号放在第一级

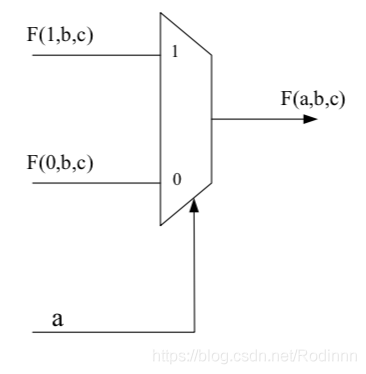

香农扩展运算

香农扩展也是一种复制逻辑,以面积换取性能的时序优化手段,其扩展运算公式为:Fa,b,c=aF1,b,c+aF(0,b,c)

香农扩展通过逻辑复制、增加MUX(多路选择器)来缩短某个优先级高但组合路径长的信号的路径延时(信号a),从而提高该关键路径的工作频率,以增加面积换取电路时序性能的优化。

在实际的电路设计中,流水站内的功能都是组合逻辑完成的:有些信号的路径比较长(信号本身来得比较晚),从而造成时序电路的建立时间不够,直接降低了电路的工作频率,这种信号路径被称为关键路径。

关键路径信号一般要提取出来,以构造优化的描述,降低其延时;设计时如果知道存在的关键路径信号,则使该信号离输出更近一些,可以降低基于该信号的关键路径延时。

浙公网安备 33010602011771号

浙公网安备 33010602011771号