低功耗设计基础

- 功耗和能耗基础

一个具有最小延迟的电路通常消耗过高的能量;

一个具有最小能量的电路通常难以接受的延迟;

通常给能量和延迟相同的权重,使用能量-延迟积作为设计的评价指标,同时也可对其赋予不同的权重。

2. 功耗来源

在 CMOS 电路中,动态功耗和静态功耗是电路总功耗的两大主要来源。 其中,动态功耗是指器件工作时,也就是信号发生变化时产生的功耗,由负载电容充放 电和短路电流功耗构成;静态功耗则是在器件并未断电但没有信号值发生变化的情况下 产生的功耗,静态功耗则主要由漏电流引起。

Ptotal = 𝑃dynamic + Pleak

其中Ptotal 表示总功耗,𝑃dynamic 表示动态功耗,Pleak 表示静态功耗。

2.1 动态功耗

动态功耗是由于输入信号的变化所引起的,这些变化包括了电容充电过程及放电过 程中产生的翻转功耗和由于产生了短路电流而引起的短路功耗。

(1)翻转功耗

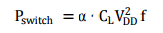

翻转功耗又称为开关功耗,为器件外部结点的电容负载进行充放电时,从电源 VDD 上消耗的功耗。这一部分的功耗在电路中占据重要地位。翻转功耗可由下面式子来表示:

其中α为跳变因子,即整个电路的平均翻转比例;CL 为负载电容值;VDD 是电源电 压;f表示的是工作频率。

(2)短路功耗

短路功耗又称为内部功耗,是因为在输入信号发生跃变时,信号的翻转不可能瞬时完成,即上升时间和下降时间不为0,造成CMOS 中的NMOS 和PMOS不可能总是一个截止另外一个导通,总有那么一段时间是PMOS和NMOS同时导通,电源VDD到地VSS的通路上出现了直流短路电流而引起功耗。一般对大多数集成电路来说,短路功耗约占动态功耗的5%~10%。公式如下:

其中K是与管子大小和工艺有关的常数;τ表示电平信号从开始上升或开始下降,直到稳定所需时间;VDD是工作电压;f为工作频率;Vth是器件阈值电压。

如果电源电压低于两种晶体管的开启电压之和,即VDD < VTN + VTP ,则可 以消除短路电流,但低电源电压是以降低芯片速度为代价的 。

2.2 静态功耗

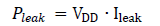

在理想情况下,晶体管关闭后是没有电流的,因此当电路的输入静止时,其功耗在此情况下应该为零。但在实际情况中,亚阈值导通、隧穿效应和栅极泄漏等效应会导致少量的静态电流流过关闭的晶体管(漏电流),由此消耗的功耗就是静态功耗。 静态功耗的计算公式如下:

式子中VDD为供电电压,Ileak为漏电流。 一般情况下,漏电流主要是指亚阈值漏电流。 亚阈值漏电流:使栅极电压低于导通阈值,仍会产生从漏极到源极的泄漏电流。此电流称为亚阈值泄漏电流。在较狭窄的晶体管中,漏极和源极距离较近的情况下会产生亚阈值泄漏电流

随着CMOS集成电路工艺的不断进步,晶体管的尺寸将变得越来越小,同时带来更低的工作电压和更大的漏电流。工作电压的降低可以减小晶体管的动态功耗,但相应的阈值电压也要降低,二阶效应越来越明显,漏电流成指数级增加,静态功耗的比重也就越来越大。

3. 低功耗设计基本途径

3.1降低动态功耗

动态功耗主要决定于工作电压、负载电容和开关活动性, 因此要进行功耗优化可以从这三方面入手。

(1)降低工作电压

动态功耗与工作电压的平方成正比

工作电压的降低必然会带来电路延迟的增大,进而影响电路的工作速度。因此在通过 降低电压来进行低功耗设计时要权衡速度与功耗的关系。

Vdd>>Vt 时,降低电压会使得延时呈线性增加,此时可 以采用改变电路结构等措施来弥补电压降低带来的延时增加。但 CMOS 电源电压有一 个下限:VDDmin ≥ VTN + VTP,电源电压低于这个下限值,电路将不能进行开关转换。 为了避免这种情况,电压最多只能降低到 2Vt 左右。

为解决功耗与速度之间的冲突,对于一个 VLSI 芯片,可以在芯片内采用多种电压, 对速度有较大影响的关键电路采用较高的电压,对非关键电路则使用相对较低的电压。

(2)降低负载电容

动态功耗与负载电容成正比

为了减小电容,在工艺上选择功耗小的器件,在物理版图上,优化布局布线减小连 线长度,缩短连线路径减小连线的寄生电容。同时通过改进电路结构,减少所需的 MOS 管数目,可以减小总的负载电容。如 CPL 电路只使用 NMOS 管构成,省去了 PMOS 逻 辑功能块,使总 MOS 管数极大地减少,负载电容就会减小。另外,SOICMOS 采用增 加埋氧化层将有源区和硅衬底隔离开,极大地减小了器件和互连线之间的寄生电容,不 仅能够有益于提高电路的速度,也极大地降低了电路的动态功耗。

(3)减小开关活动性

要减小开关活动性,一是在保证性能的前提下尽量使用低频 信号作为时钟;二是在信号不需要翻转或是信号保持不变时关闭到达电路的时钟,使得 电路不翻转,信号活动性为 0,电路则节省了这段时间所要消耗的能量。

3.2 降低静态功耗

减小亚阈值电流是降低功耗的一个重要设计考虑。对深亚微米 CMOS 电路必须综 合考虑速度和功耗的因素,合理设计器件的阈值电压。可以采用给 NMOS 管加一个小 的负栅-源电压,使亚阈值电流减小。用一个开关控制的源极串联电阻就可以是实现负 的栅偏压。对 PMOS 管则采用加一个正的栅-源电压来达到减小截止态亚阈值电流的目的。

采用多阈值(MTMOS)和动态阈值(DTMOS)技术是减小静态功耗的有效措施。 电路设计时,影响速度的关键路径采用低阈值电压的 MOS 管,而非关键路径采用较高 阈值电压的 MOS 管,从而减小亚阈值电流。另外,通过改变 MOS 晶体管的衬底偏压 可以实现动态阈值。当 MOS 管工作时使其具有较低的阈值电压,而当电路处于空闲状 态时 MOS 管的高阈值电压可以降低电路的静态功耗。

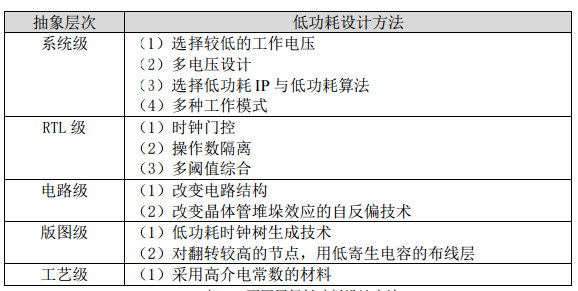

4 不同设计层次采用的低功耗设计方法

在能耗受限的情况下,设计是一个折中的过程:在给定性能需要下最小化能量,在给定能量预算后最大化性能

浙公网安备 33010602011771号

浙公网安备 33010602011771号