组合逻辑设计问题

2、组合逻辑设计回顾

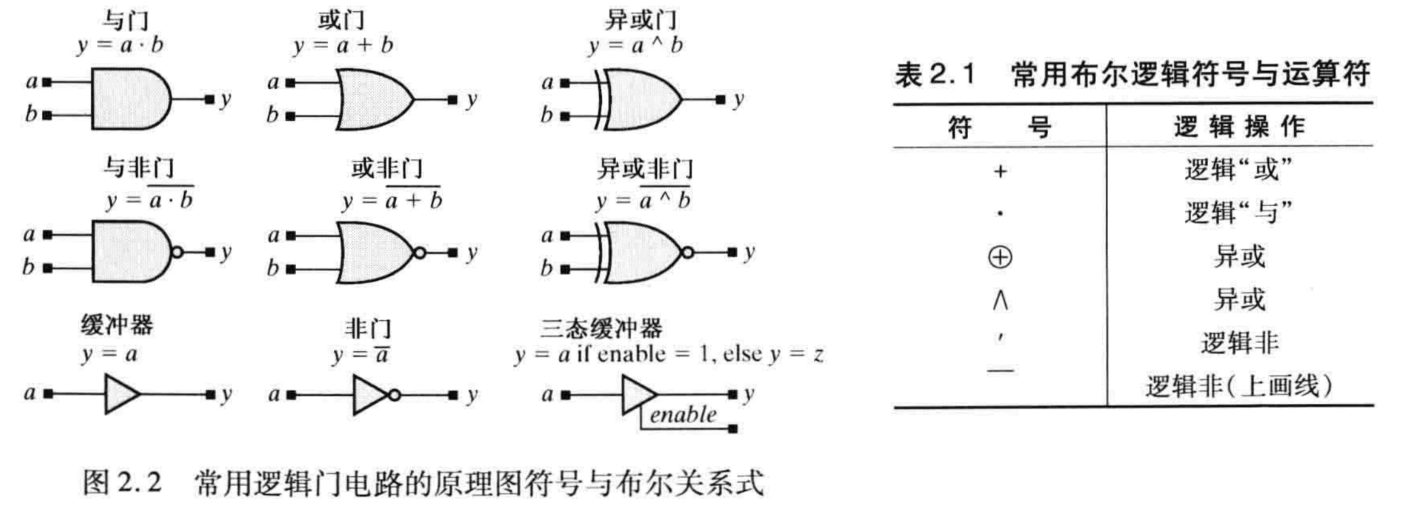

2.1组合逻辑与布尔代数

组合逻辑电路任意时刻的输出仅与该时刻的输入有关。

综合工具通过将逻辑综合的最终结果映射为单元库中的不同部件,来构造具有特定功能且满足性能要求的复杂集成电路。

中间掠过

离散数学基础知识

2.5毛刺与冒险

毛刺:在输入逻辑没有发生变化的情况下,组合逻辑电路的输出发生非预期的变化。

冒险:静态冒险、动态冒险

静态冒险

电路的输出在某种输入情况下,不该发生跳变却发生了跳变。

静态冒险由不同扇出路径上的不同传播时延造成。

通过在输出表达式的覆盖中引入冗余项来消除静态冒险,仅适用于输出毛刺由单个输入信号发生变化造成。

动态冒险

在一个电路中,原本期望一个输入变化仅会造成输出的一次变化,实际上却导致输出在到达期望值之前发生两次或多次变化。

动态冒险由多条重新汇聚路径所导致的多个静态冒险叠加产生

通过消除静态冒险,即可消除动态冒险。

2.6逻辑设计模块

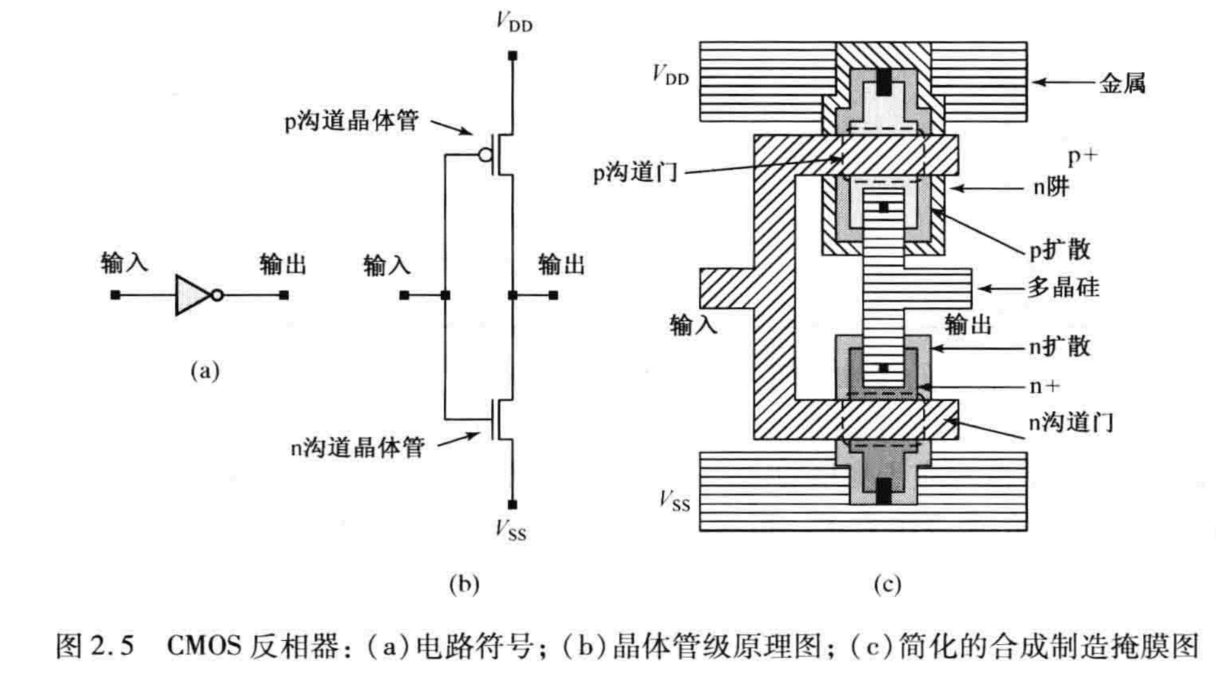

对于CMOS工艺,与非门和或非门更容易实现。而由于任何布尔函数都可以采用积之和和和之积来表示,因此仅采用与非门和或非门即可实现任何布尔函数。

浙公网安备 33010602011771号

浙公网安备 33010602011771号