Cache

Cache

2.1 Cache的一般设计

cache的产生原因:大容量存储器的访问速度和处理器的运行速度不匹配

并且数据之间存在时间相关性和空间相关性,即一个数据现在被访问以后可能还会被访问,它周围的数据也可能会被访问。

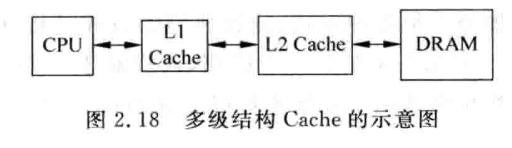

L1cache速度最快,紧密耦合在处理器流水线中。

L1 cache一般包含指令Cache(I-Cache)和数据Cache(D-Cache),一般使用SRAM实现,主要体现“快”。

L2 Cache体现“全”,一般指令和数据共享,要尽量保存更多的内容。

多核情况下,L1 Cache属于私有,L2与L3可以多核共享。

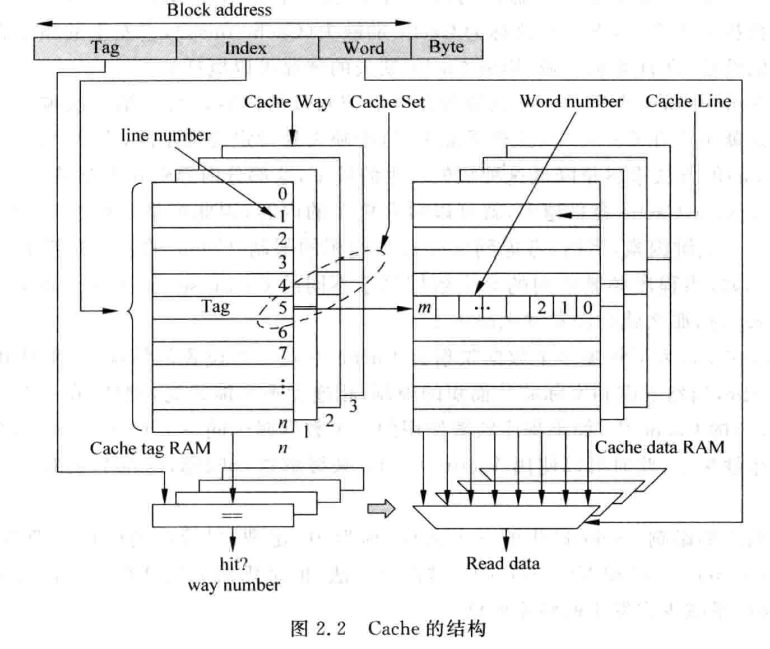

Cache由Tag和data转成,data从来保存一片连续地址的数据,tag保存这片连续数据的公共地址。一个Tag和它对应的所有数据组成的一行称为一个Cache line。

Cache的缺失:cache只能保存最近被处理器使用过的内容,但由于容量有限,很多情况下要找的指令或数据并不在cache中。

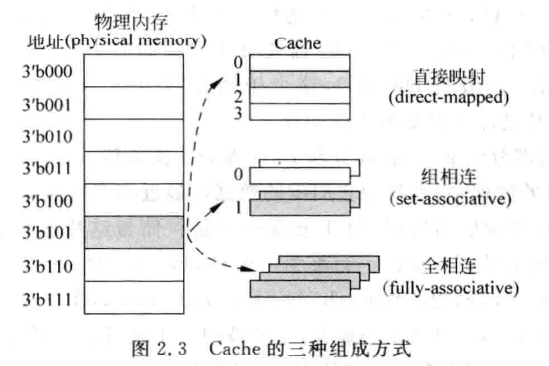

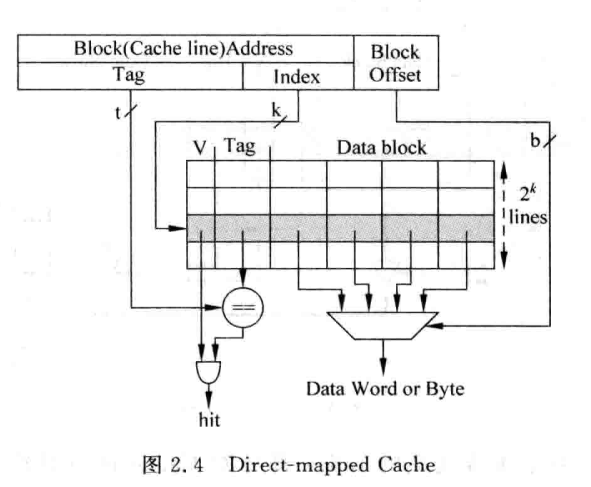

直接相连

查找数据时先对比index,再对比tag,最后通过block offset获得数据实际位置。但index部分相同时,cache对应位置就会被交互访问,一直缺失。

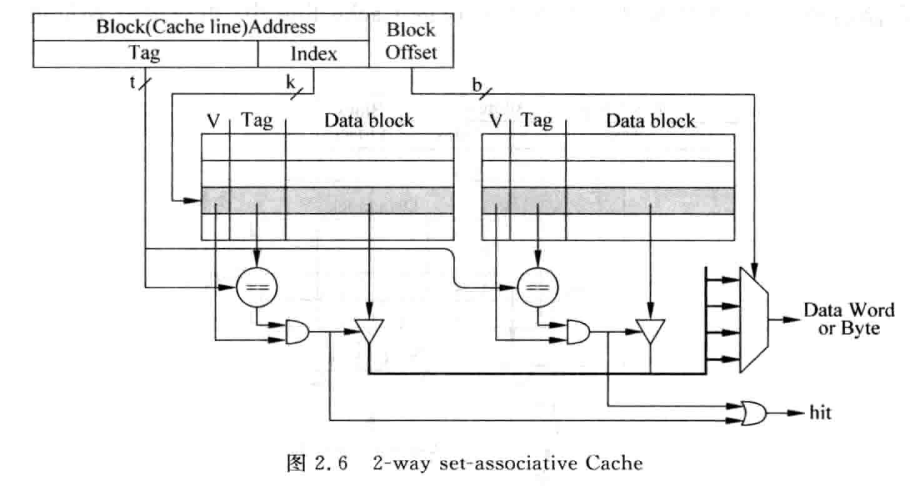

组相连

思想是一个数据不单单只放在一个cache line中,对index寻址后通过对比tag确定最终哪个cache line才是需要的。如果tag全都比对错误,那么说明发生了cache缺失。此种方法因为需要比对tag所以延迟会比较大,但能显著减少cache缺失发生的频率。

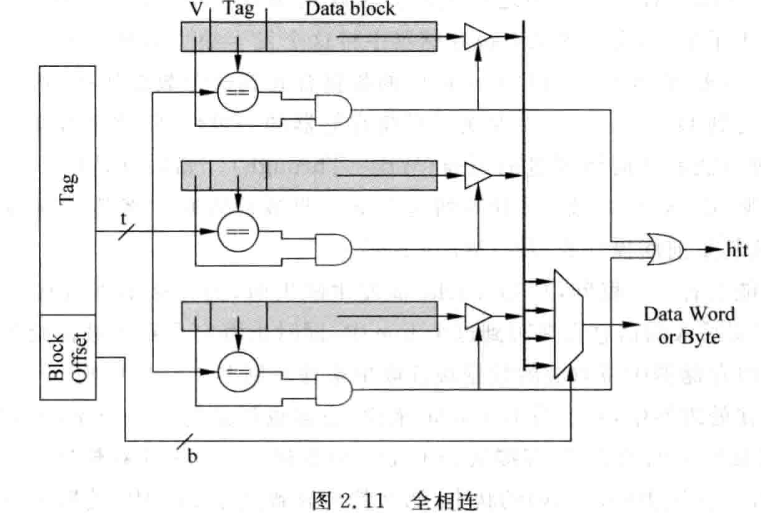

全相联

不再需要index,通过tag在整个cache中进行比较。

全相联cache缺失率最低,延迟也最大。一般使用CAM(Content Address Memory)存储tag,使用普通SRAM存储数据。

2.2提高cache的性能

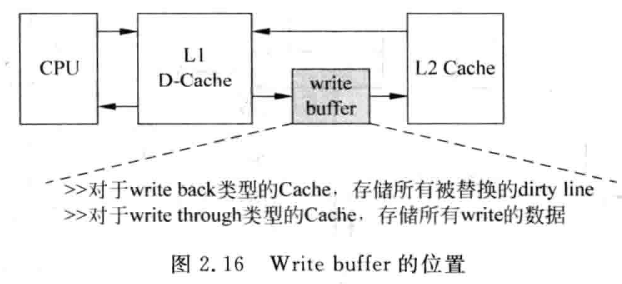

写缓存

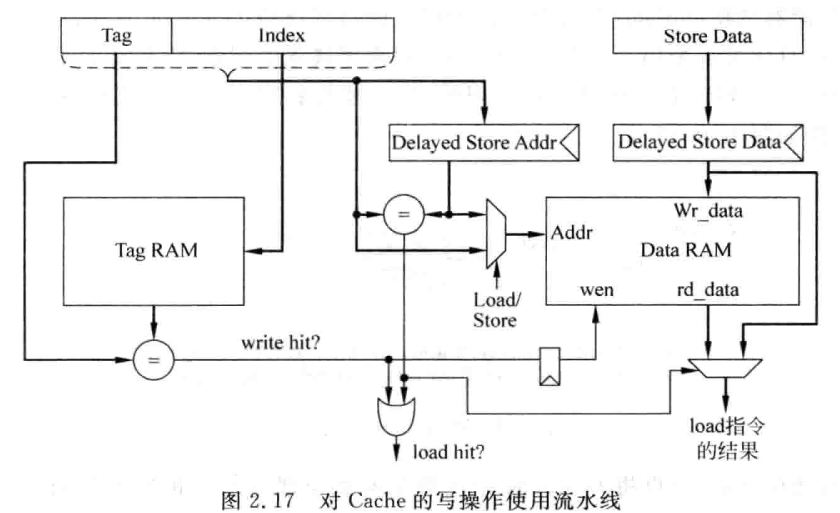

流水线

多级结构

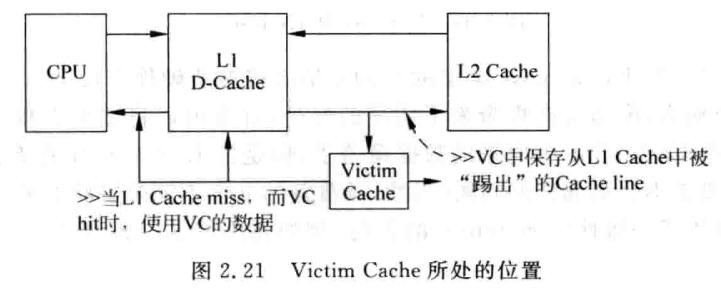

victim cache

本质相当于增加了 way的个数,能够避免多个数据竞争cache中有限的位置。

2.3 多端口Cache

最原始的多端口Cache将所有Cache中的控制通路和数据通路都进行复制,但这种方法会增大很多面积,并且需要驱动多个端口会增加访问时间和功耗。

常用方法

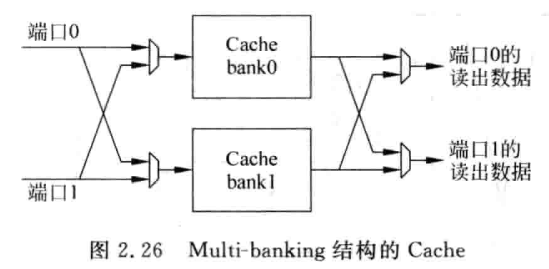

multi-banking

将cache分为很多小的banck,每个bank只有一个端口。

2.4 超标量处理器的取指令

n-way的超标量处理器的I-Cache应该支持每周期能至少取出n条指令,这样才能不浪费流水线。

对于cache来说,一个周期只能访问一个cache line,除非n条指令在同一个cache line中才可以一次性取出,不然无法取足就会造成流水线性能浪费。

浙公网安备 33010602011771号

浙公网安备 33010602011771号