时钟和复位

时钟和复位

2.1 概述

2.2 同步设计

经验表明,对ASIC的时域控制最安全的方法就是同步设计。

行波计数器

避免使用上一级触发器数据输出作为下一级触发器时钟输入,会导致延迟累计增加。

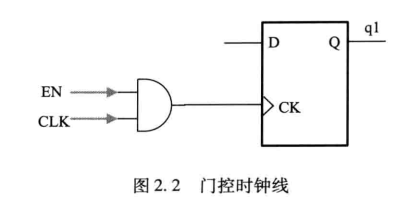

门控时钟

时钟线上的门控单元会导致时钟偏移,并会引入尖峰脉冲作用于触发器。

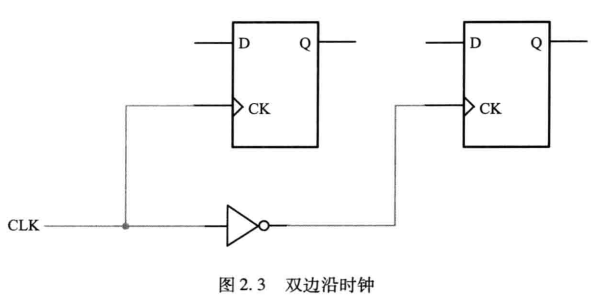

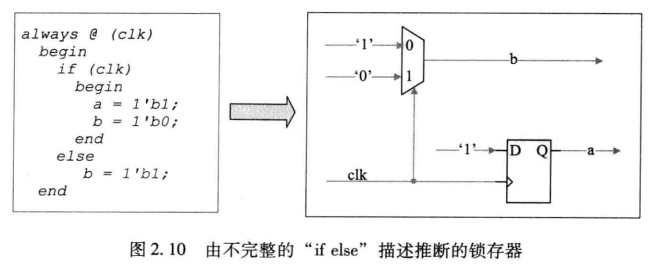

双边沿或混合边沿时钟

会为使用同步复位和插入扫描链等测试方法带来麻烦,并且增加确定关键信号路径的难度。

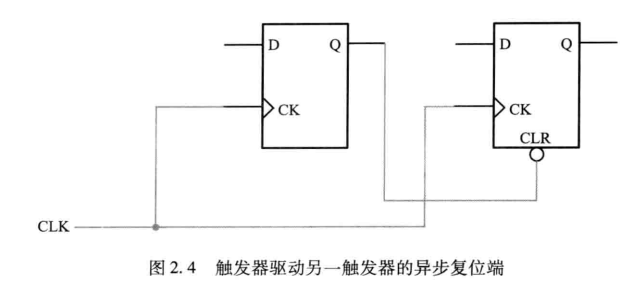

用触发器驱动另一个触发器的异步复位端

2.3 推荐的设计技术

避免出现组合环路

在同步设计中,所有的反馈回路都应包含寄存器。

组合环路会导致无休止的循环运算。

避免数字设计中的延迟链

用两个或多个带有单扇入和单扇出的连续节点产生延迟时,就会形成延迟链。

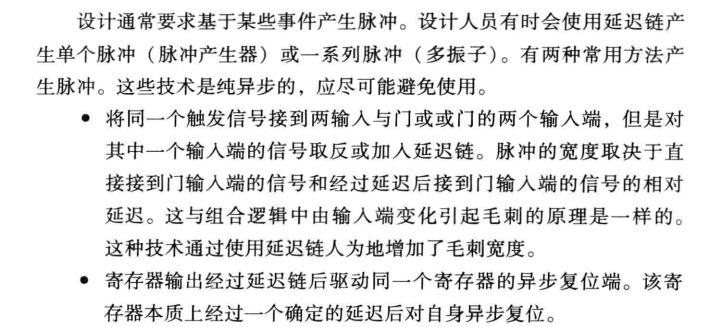

避免使用异步脉冲产生器

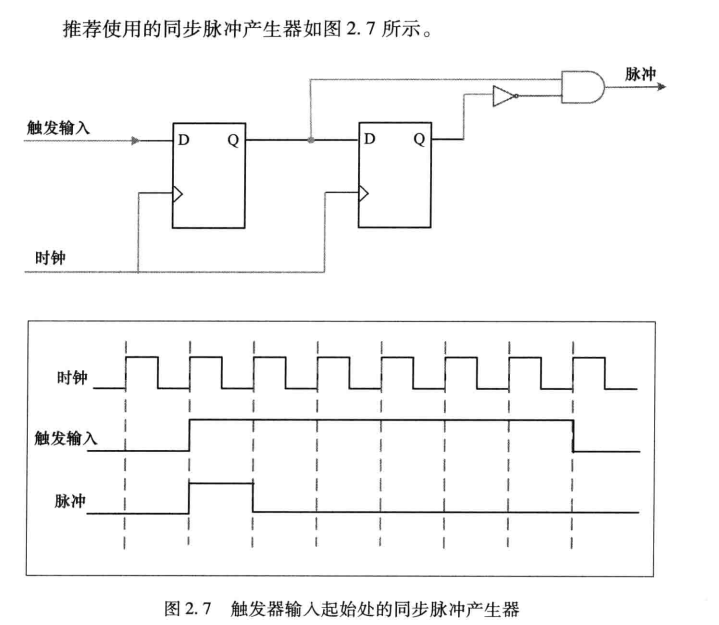

避免使用锁存器

数字设计中,锁存器用来在新的值到来之前保持原来信号的值。

锁存器是连通模式的,在数据输入和输出之间存在直接通路,输入端的毛刺能直接传递到输出端。

避免使用双边沿时钟

使用双边沿时钟有其他好处

- 过高的时钟频率会给接口带来问题,比如接口本身的电气特性会随着时钟频率和时序的增加干扰变得越来越敏感,对接口电路要求更高,增加成本。

- 双边沿时钟频率减半,系统功耗也会减半。

除非等效同步电路无法满足所期望的性能时,系统设计人员才会考虑双沿时钟。

2.4 时钟方案

设计者要尽可能避免在内部产生时钟。

组合逻辑搭建的时钟产生器会引入毛刺,使功能出现问题,还会引入延迟。

在设计中要保证大多数时钟来自PLL。

日常设计避免使用行波计数器进行时钟分频,但在功耗较高的系统中比较适合,可以降低由逻辑或SOC引起的峰值功耗。

门控时钟是减少功耗的有力手段,但会增加时钟偏移并对毛刺敏感。

2.5 门控时钟方法学

传统同步设计中的功耗

- 在每个时钟沿变化的组合逻辑所产生的功耗(由触发器驱动)

- 由触发器产生的功耗(即使触发器输入和状态未改变,此功耗也存在)

- 设计中时钟树产生的功耗

对时钟路径进行门控可大幅降低触发器的功耗,门控时钟可存在于时钟树任何位置,但最好在根部,可以关闭整个时钟。

2.6 复位信号的设计策略

某些情况下,流水线的寄存器在告诉应用中使用时,应该去掉某些寄存器的复位信号以使设计达到更高性能。

使用同步复位出现的一个问题是综合工具无法分辨复位信号和其他数据信号。

同步复位优点

同步复位缺点

- 综合工具无法识别同步复位信号,容易把复位逻辑综合到触发器自身之外。

- 同步复位可能需要脉冲展宽器保证复位信号出现在时钟有效沿处。

- 时钟被关闭时,同步复位可能失效。

异步复位优点

异步复位缺点

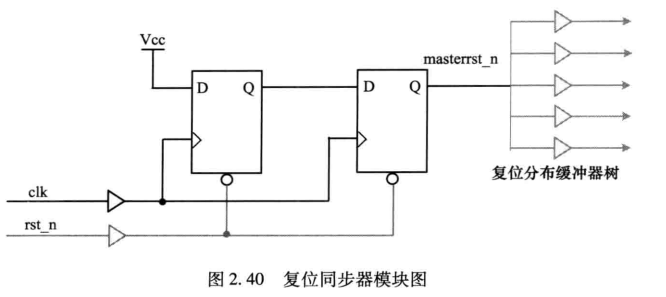

异步复位需要同步释放

2.7 控制时钟偏移

相邻触发器之间的数据路径传播延迟比两者之间的时钟偏移小时,会出现时钟偏移和短路径问题。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 地球OL攻略 —— 某应届生求职总结

· 周边上新:园子的第一款马克杯温暖上架

· Open-Sora 2.0 重磅开源!

· 提示词工程——AI应用必不可少的技术

· .NET周刊【3月第1期 2025-03-02】