第三章

3、数字逻辑电路设计基础

3.1 数字逻辑电路设计与verilog代码开发

3.1.1 面向硬件电路的设计思维方式

硬件设计思维核心:数据通路+控制逻辑

设计电路先想清楚数据通路

3.1.2 行为描述的verilog编程风格

verilog描述分为行为描述和电路描述

3.1.3 自顶向下的设计划分过程

设计CPU→考虑输入、输出→时钟、复位→内存访问接口、IO访问接口→CPU内部模块划分:取指、译码、执行、方寸、写回

3.1.4 常用数字逻辑电路的verilog描述

一些硬性规定

模块声明和实例化

基础逻辑门

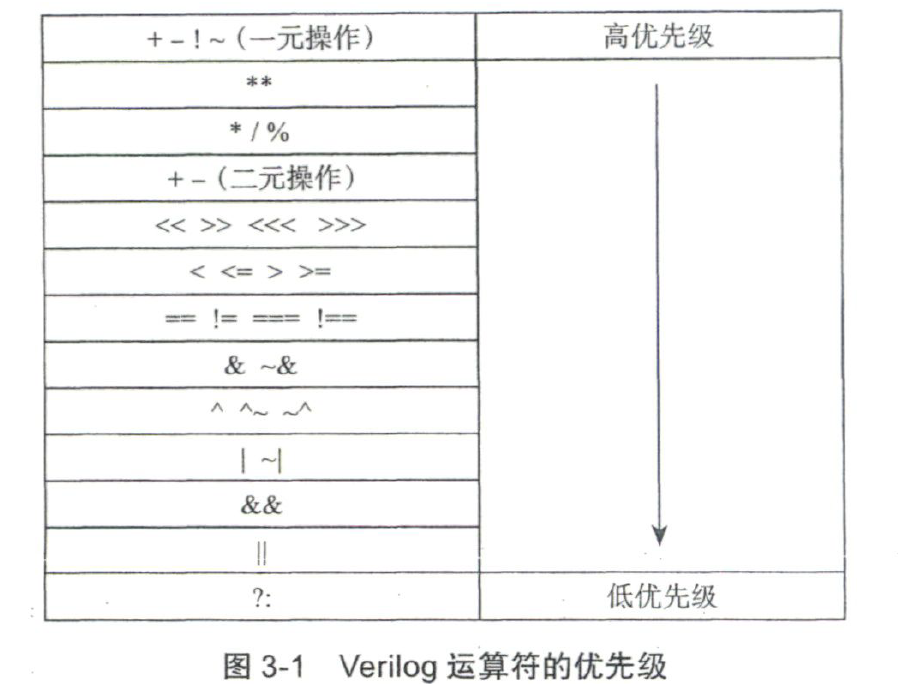

运算符的优先级

译码器

通过指令确定指令类型

编码器

根据移码结果生成运算单元操作码

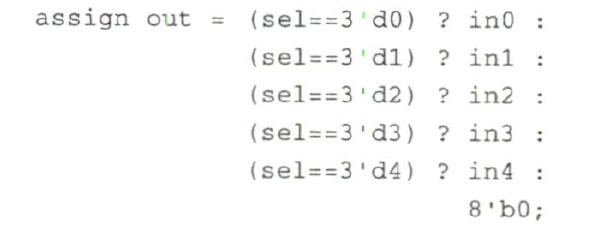

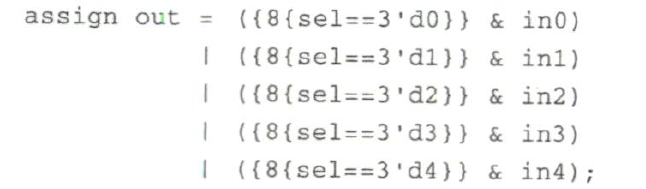

多路选择器

此写法会引入优先级,可改成如下写法

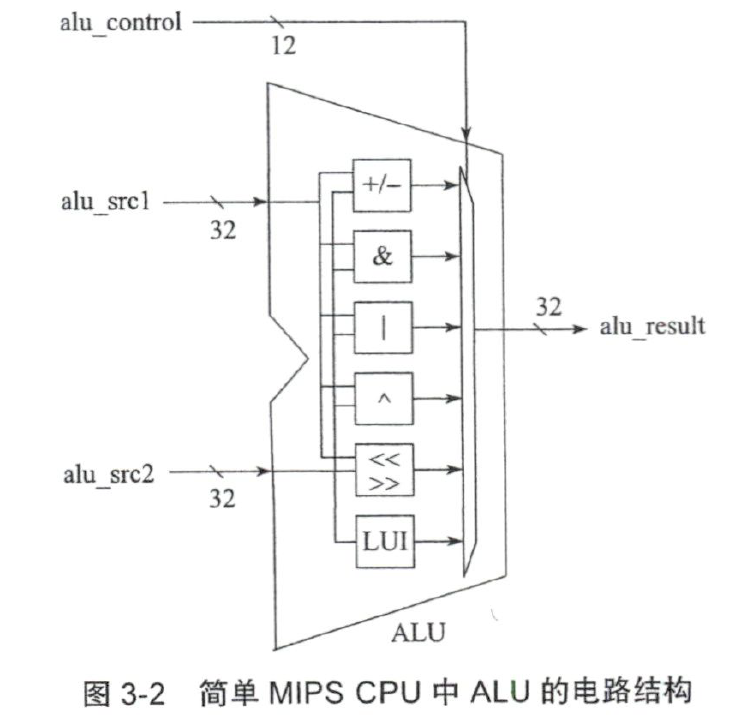

简单MIPS CPU中的ALU

- 加减运算

- 比较运算

- 移位运算

- 逻辑运算

触发器

MIPS CPU中的寄存器堆

为支持流水,寄存器堆要支持每周期读出两个32位数、写入一个32位数。

写为时序逻辑,发生在时钟上升沿。读为组合逻辑,随时读取。

写操作作为时许逻辑可以避免毛刺,防止出现错误。

当写有效(we=1)且2写地址和读地址相同时,读出的结果是寄存器中的旧值还是新写入的值?

我认为是旧值

RAM

SRAM逻辑行为和寄存器堆相似,但是底层实现完全不同。一般RAM要采用实例化RAM IP的方式。

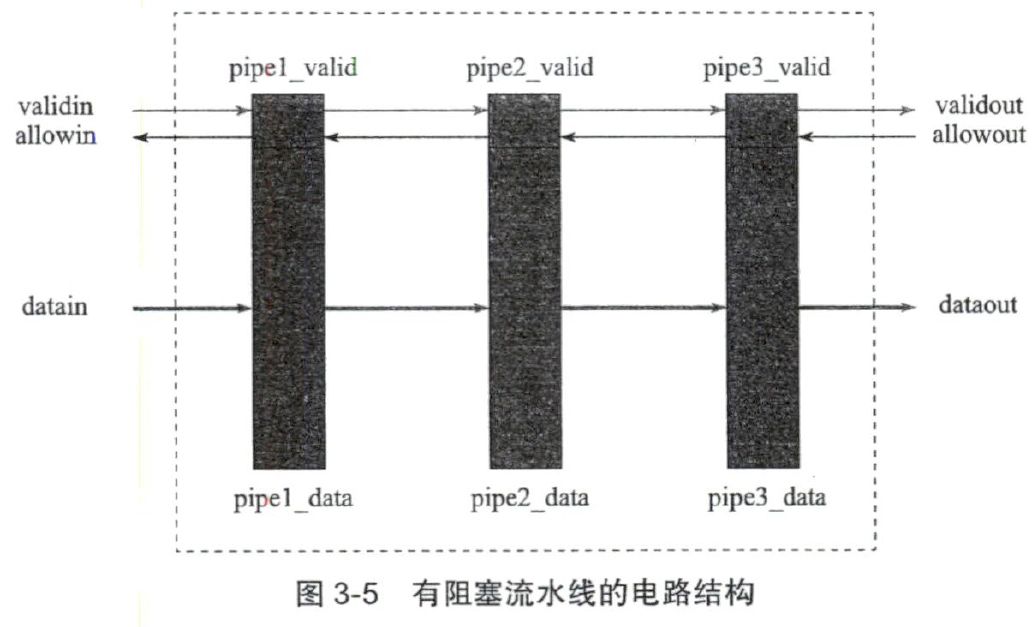

流水线

无阻塞流水线其实就是依次串接起来的多组触发器。

但如果流水线被阻塞,就要求前面的流水线要支持把原有数据保持在本流水线,避免数据丢失。

保持数据的关键在于使用带使能的触发器,并控制使能信号。

前级触发器和后级触发器交换信息,确定数据是否传递。当发生阻塞时,只需要valid置0,即可暂停流水线保持数据。

浙公网安备 33010602011771号

浙公网安备 33010602011771号