第五章、先见森林,后观数目—蜂鸟E200设计总览和顶层介绍

5.1 处理器硬件设计概述

5.1.1 架构和微架构

架构是指指令集架构,微架构是对其具体实现

5.1.2 CPU、处理器、Core、和处理器核

CPU和处理器是完整SOC,Core和处理器核是SOC核心的信号处理部分

5.1.3 处理器设计和验证的特点

5.2 蜂鸟E200处理器核设计哲学

- 模块化和可重用性

- 面积最小化

- 结构简单化

- 性能不追求极端

5.3 蜂鸟E200处理器核RTL代码风格介绍

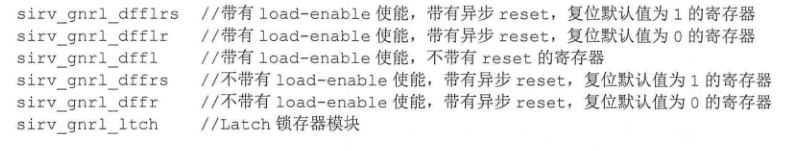

5.3.1 使用标准DFF模块例化生成寄存器

对于寄存器避免直接使用always块编写,而是应该采用模块化的标准DFF模块进行例化。

使用标准DFF模块例化得好处

- 便于全局替换寄存器类型

- 便于在寄存器中全局插入延迟

- 明确的load-enable使能信号方便综合工具自动插入寄存器级别得门控时钟以降低功耗

- 便于规避verilog语法if-else不能传播不定态的问题

标准DFF模块

标准DFF模块内部采用verilog语法的always块进行编写。由于if-else语法不能传播不定态,对处于if条件中的lden信号为不定态的非法情况使用断言进行捕捉(systemverilog)。

5.3.2 推荐使用assign语法代替if-else和case语法

if-else和case

- 不能传播不定态

- 会产生优先级选择电路而非并行选择电路,不利于时序和面积

当a=x时,if(a)会认为a=0,判为假,可能会在仿真阶段掩盖某些致命bug。

使用assign的不同写法可以明确控制生成并行选择电路和优先级选择电路。

5.3.3 其他若干注意事项

带有reset的寄存器面积和时序会稍差一点,因此可以在数据通路使用不带reset的寄存器,只在控制通路使用带reset的寄存器。

5.3.4 小结

使用assign语法和标准DFF例化方法能够在仿真阶段暴露任何不定态,综合出很高质量的电路,门控时钟频率也很高。

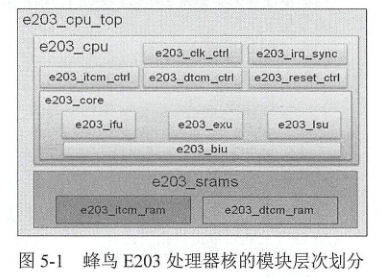

5.4 蜂鸟E200模块层次划分

- e203_clk_ctrl控制处理器各个主要组件 的自动时钟门控

- e203_irq_sync用于将外界的异步中断信号进行同步

- e203_reset_ctrl用于将外界的reset信号进行同步,实现异步置位同步释放

- e203_itcm_ctrl和e203_dtcm_ctrl控制ITCM和DTCM的访问

5.5 蜂鸟E200处理器核源代码

5.6 蜂鸟E200处理器核配置选项

修改config.v

5.7 蜂鸟E200处理器核支持的RISC-V指令子集

5.8 蜂鸟E200处理器流水线结构

第六章

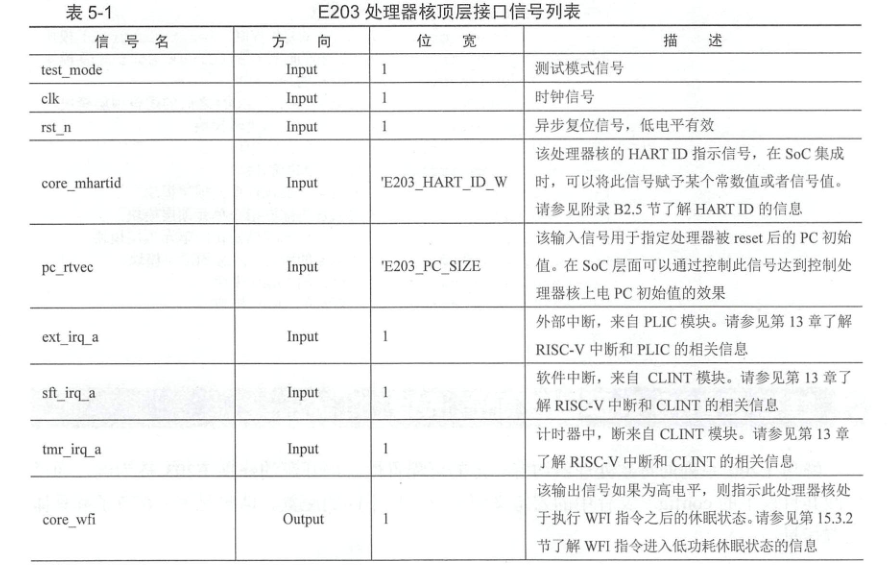

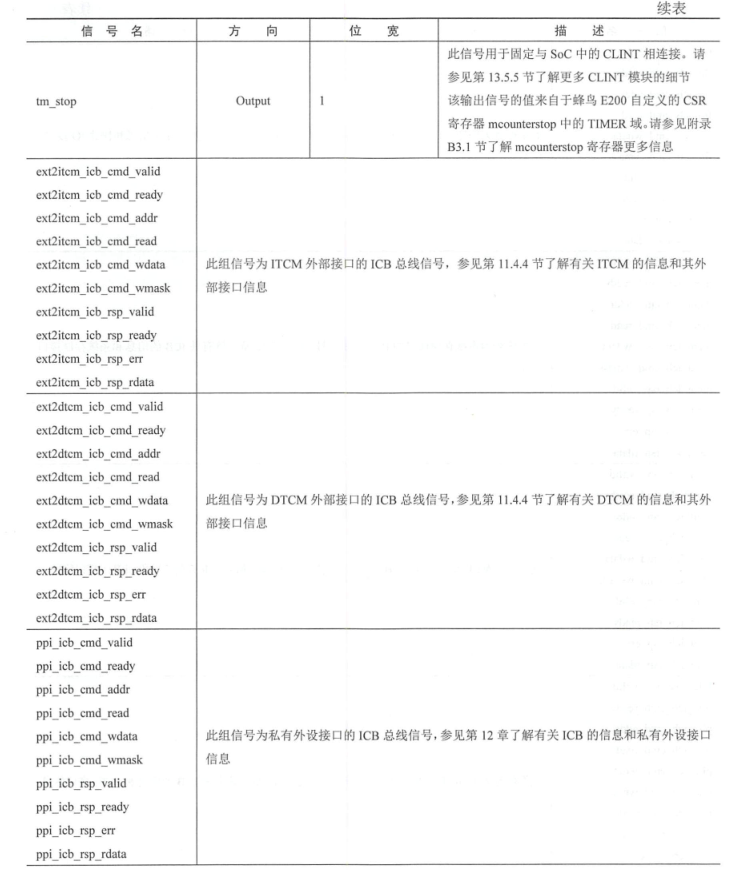

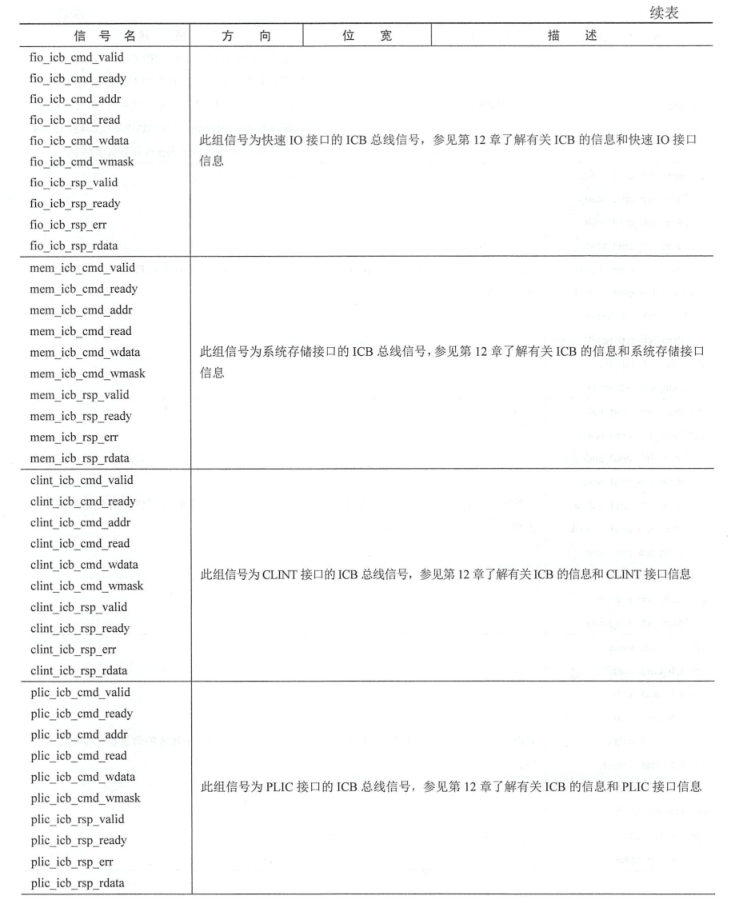

5.9 蜂鸟E200处理器核顶峰接口介绍

浙公网安备 33010602011771号

浙公网安备 33010602011771号