第二章、大道至简—RISC-V架构之魂

- RISC:表示精简指令集

- RISC-V:伯克利发明的指令集架构,属于RISC类型

2.1 简单就是美—RISC-V架构的设计哲学

设计哲学:大道至简,简单、直接、可靠

2.1.1 无病一身轻—架构的篇幅

RISC-V架构文档分为指令集文档与特权架构文档,各一百来页。

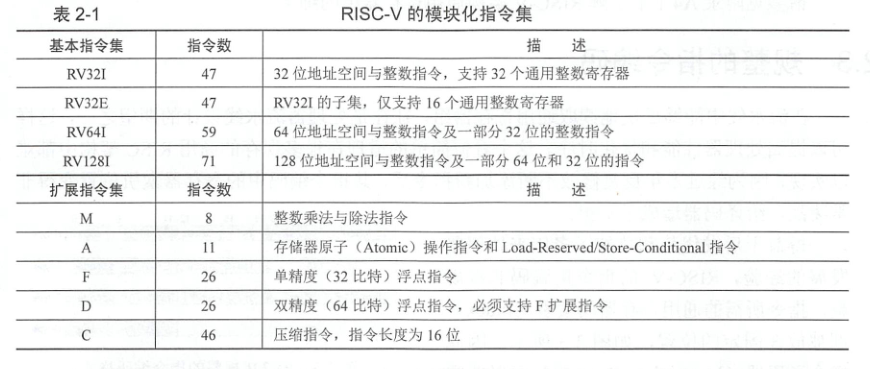

2.1.2 能屈能伸—模块化的指令集

RISC-V架构短小精悍,将不同部分模块化,可以通过一套统一的架构满足不同的应用。用户可以根据需求选择不同的模块进行组合。

2.1.3 浓缩的都是精华—指令的数量

基本指令数目仅有40多条

2.2 RISC-V 指令集架构简介

2.2.1 模块化的指令子集

RISC-V基本要求是I字母表示基本整数指令子集必须实现,其他指令子集为可选模块。

- “IMAFD”称为通用组合,用G表示。RV32G表示RV32IMAFD。

- 字母E表示“嵌入式”架构,可以进一步减小面积、降低功耗。

- 追求小面积、低功耗的嵌入式场景可以选择RV32EC架构,大型的64位架构可以选择RV64G。

2.2.2 可配置的通用寄存器组

- 整数通用寄存器组无论是RV32,REV64等,都包含32个寄存器,不同的是位宽。用于嵌入式的RV32E包含16个通用寄存器。

- 对于上述寄存器组,整数寄存器0被预留为常数0,其余寄存器为普通通用整数寄存器。

- 若添加F和D模块,则需增加一组浮点寄存器,一组32个。F模块为单精度浮点指令,寄存器位宽要求32,若进一步支持D模块,寄存器位宽需要64。

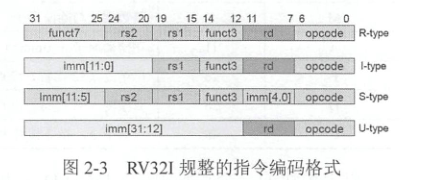

2.2.3 规整的指令编码

RISC-V的指令集中寄存器索引位置固定,对于译码器来说可以非常快速的获取寄存器索引从而读取相应数据进行运算

2.2.4 简洁的存储器访问指令

- RISC-V架构使用load/store指令访问存储器,其他普通指令无法访问存储器。

- RISC-V对于地址对齐访问和非对齐访问都支持,但支持小端模式。

- RISC-V架构的存储器读写指令不支持地址自增自减。

- RISC-V架构采用松散存储器模型(Relaxed Memory Model),对于访问不同地址的存储器读写指令的执行顺序不做要求,除非使用明确的存储器屏障指令(Fence)加以屏蔽。

2.2.5 高效的分支跳转指令

- 两条无条件跳转指令。jal用于子程序调用,jalr用于子程序返回指令。

- 六条条件跳转指令,RISC-V采用一条指令完成整数比较和跳转操作。

- 对于没有配备硬件分支预测的低端CPU,RISC-V明确要求采用默认的静态分支预测机制,并且编译器也按照这种机制来生成汇编代码,可以保证性能。

2.2.6 简介的子程序调用

程序调用子函数过程

- 进入子函数前需要保存现场,即用store指令将通用寄存器组内的值存到系统存储器的堆栈区。

- 退出子函数后需要恢复现场,将之前存的通用寄存器组内的值从堆栈区读出来。

RISC-V不采用“一次读多个寄存器指令”“一次写多个寄存器指令”。对于“保护现场”“恢复现场”指令数目有要求的场景,可以采用公用的程序库。

2.2.7 无条件码执行

早期的RISC架构发明了带条件码的指令,例如指令编码前几位为条件码,条件码对应为真指令才被执行。

RISC-V对于任何条件判断都采用普通电容待条件分支跳转,不采用条件码,条件码会使硬件设计变复杂。

2.2.8 无分支延迟槽

MIPS架构具有分支延迟槽,在分支跳转指令后紧跟若干指令,不受分支跳转指令影响一定执行。

RISC-V放弃分支延迟槽,现代高性能处理器的分支预测算法效果更好。

2.2.9 零开销硬件循环

一半for循环会由编译器翻译为若干条加法指令和分支跳转指令,而硬件循环是通过寄存器计数来进行循环。这种方式可以减少汇编指令条数,提高性能。

RISC-V架构为了化简硬件设计,不采用零开销硬件循环。

2.2.10 简洁的运算指令

RISC-V架构对于运算指令错误(如溢出、除零等)不产生异常,而是产生某个特殊的默认值,同时设置某些状态寄存器的状态位。

RISC-V推荐软件通过其他方法来找到这些错误。

2.2.11 优雅的压缩指令子集

16位压缩指令由32位指令中的信息压缩重排获得,每条16位指令都能找到其一一对应的原始32位指令。

2.2.12 特权模式

RISC-V定义三种工作模式,也称特权模式

- 机器模式:Machine Mode ,必选模式

- 监督模式:Supervisor Mode ,可选模式

- 用户模式:User Mode ,可选模式

2.2.13 CSR寄存器

Control and Status Register,用于配置和记录一些运行状态。CSR寄存器的访问采用专门指令。

2.2.14 中断和异常

2.2.15 矢量指令子集

2.2.16 自定制指令扩展

RISC-V预留了编码空间用于用户自定义扩展

2.2.17 总结与比较

RISC-V的特点在于极简、模块化以及可定制扩展,由于这些特性RISC-V可构建适用于任何领域的微处理器。

浙公网安备 33010602011771号

浙公网安备 33010602011771号