【VCS版】【mentor公司的例子】基于UVM的UART验证环境

之前偶然在群里看到有人分享了Mentor Graphics提供的一个UART的UVM验证环境代码,包含了UVM的基本使用以及进阶的UVM寄存器模型。这里也分享给大家。

文件说明

agents/apb_agent - APB agent used in the UVM testbench

agents/uart_agent - UART agent user in the UVM testbench

agents/modem_agent - UART Modem interface agent, used in the UVM testbench

docs

protocol_monitor - contains an example APB protocol monitor

rtl - Contains the UART RTL source code***

sim - Simulation directory for the example, contains the Makefile

uvm_tb/tb - Top level testbench

uvm_tb/tests

uvm_tb/virtual_sequences

uvm_tb/sequences

uvm_tb/register_model

uvm_tb/env - contains the functional coverage monitors described in the cookbook

DUT是16550A UART模块,接口主要包含apb、uart以及一些状态信号,agents下是不同接口的agent。16550A UART推荐大家自己搜索下载详细的spec。

docs是uart模块的简单说明,包含了一些寄存器的说明

protocol_monitor是一个协议检查模块,通过断言对apb协议进行检查

环境集成以及sequence等编写在uvm_tb下。

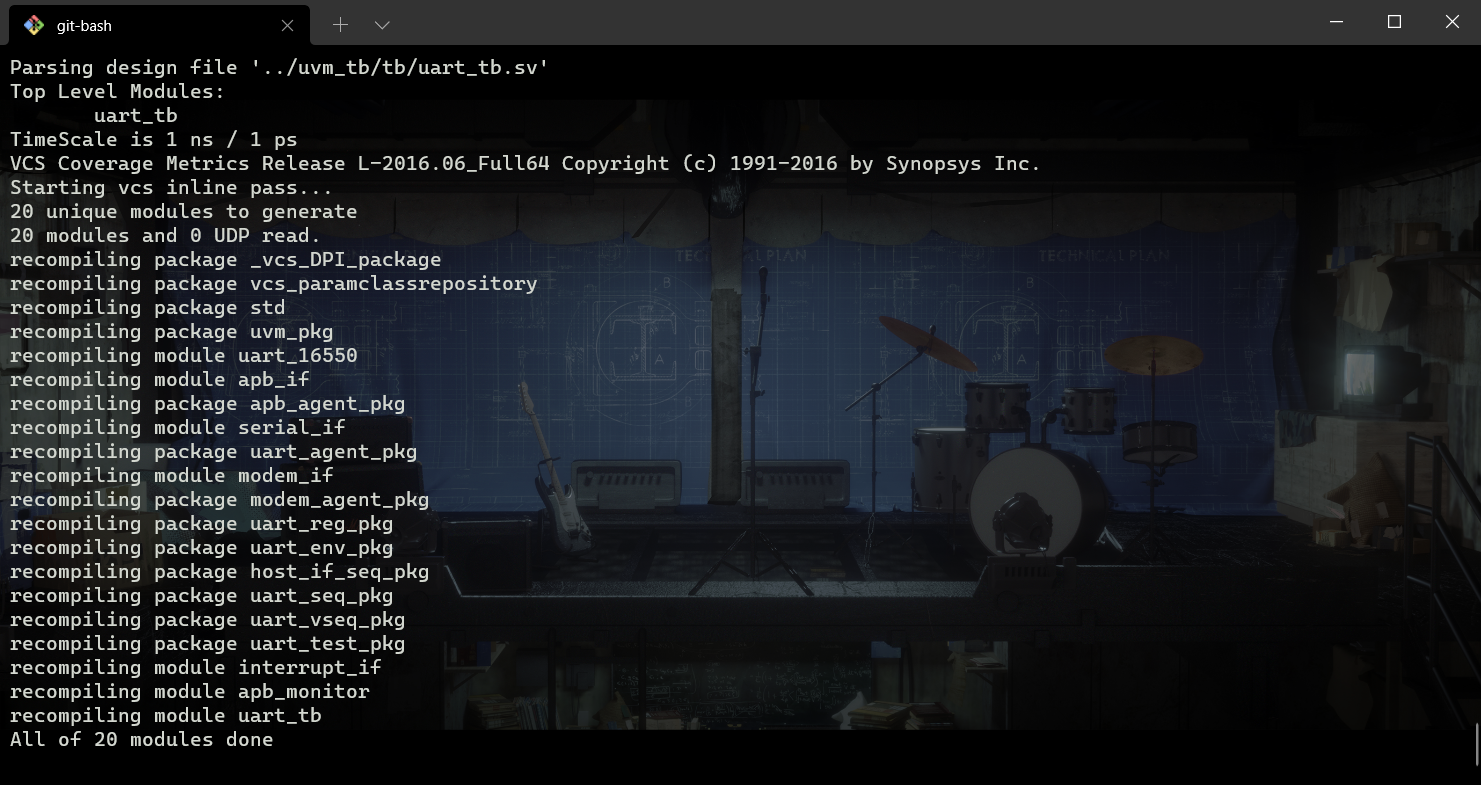

运行仿真

由于是mentor公司提供的例子,所以原来的makefile调用的是Questa,本次改了一下makefile,用vcs运行,然后生成覆盖率之后可以导出网页报告,或者用verdi查看覆盖率。

make all运行

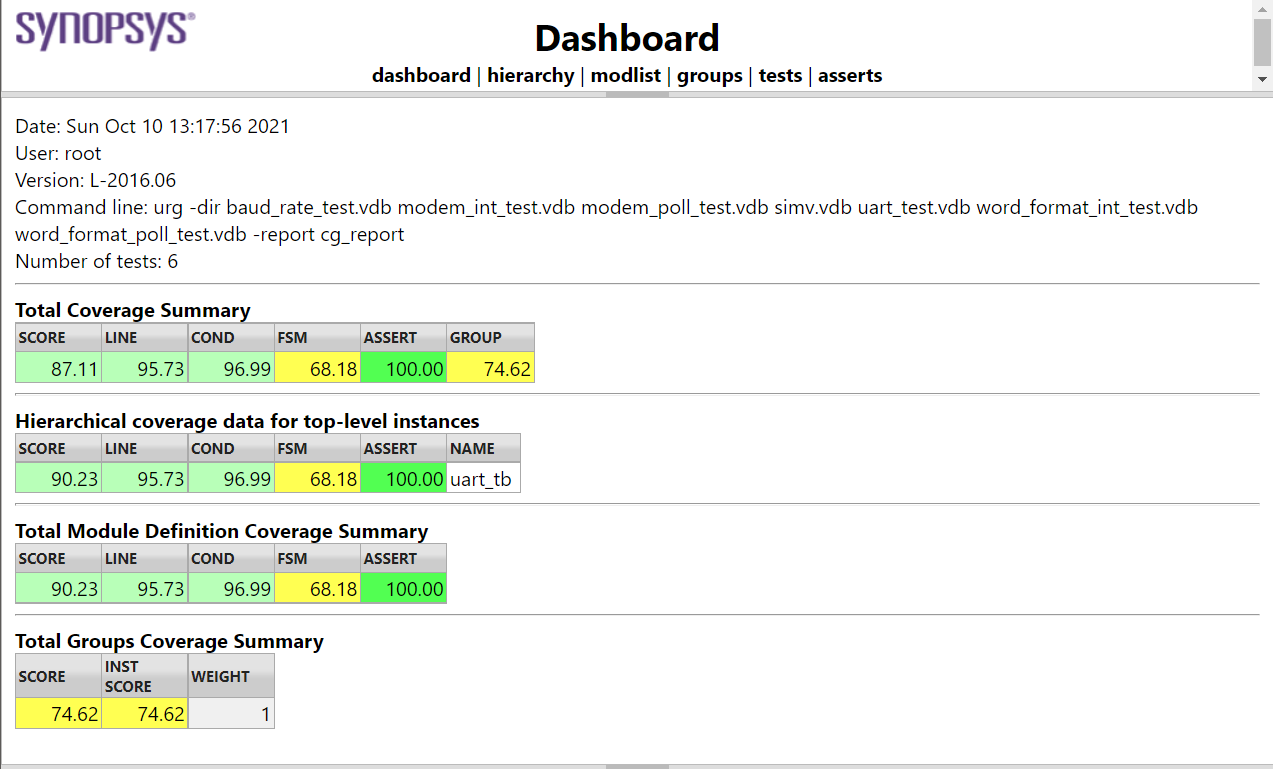

覆盖率报告生成在cg_report目录下

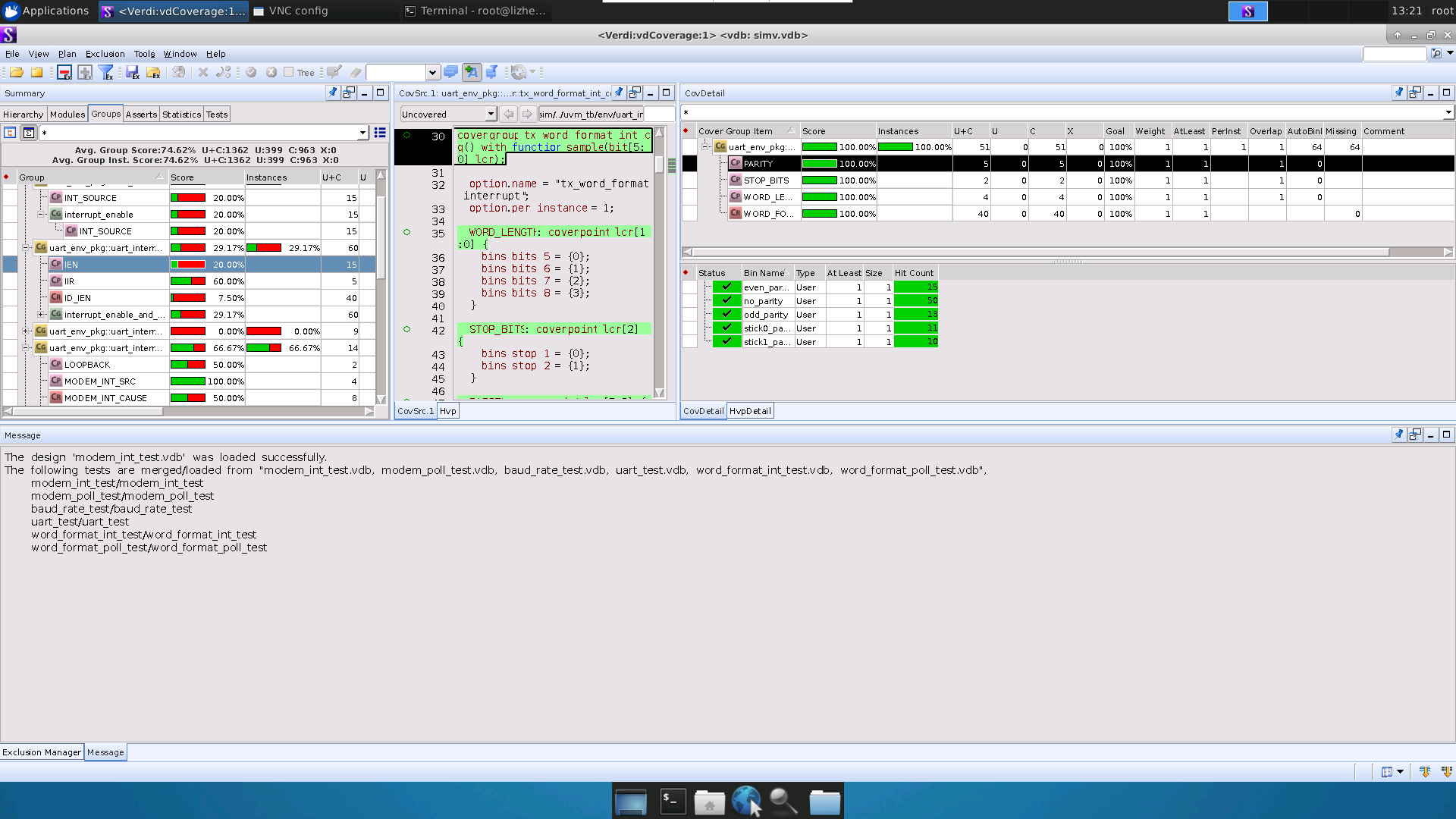

make verdi_cg使用verdi查看覆盖率

例子中的编写的testcase并不能达到100%覆盖率,有兴趣可以自己试着写新的case,去提高覆盖率

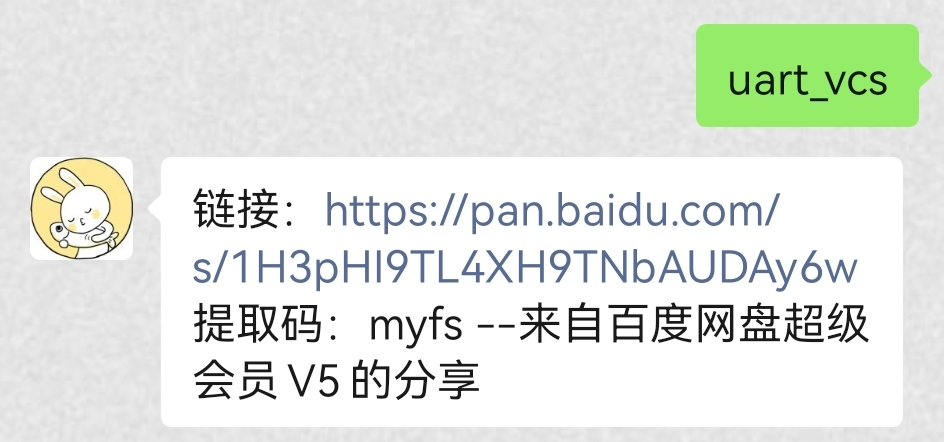

后台回复

uart_vcs获得验证环境

另外,仿真的EDA工具也可以看下面的文章

浙公网安备 33010602011771号

浙公网安备 33010602011771号