【第九章 接口分析 下】静态时序分析圣经翻译计划

本文由知乎

赵俊军授权转载,知乎主页为https://www.zhihu.com/people/zhao-jun-jun-19

9.3 DDR SDRAM接口

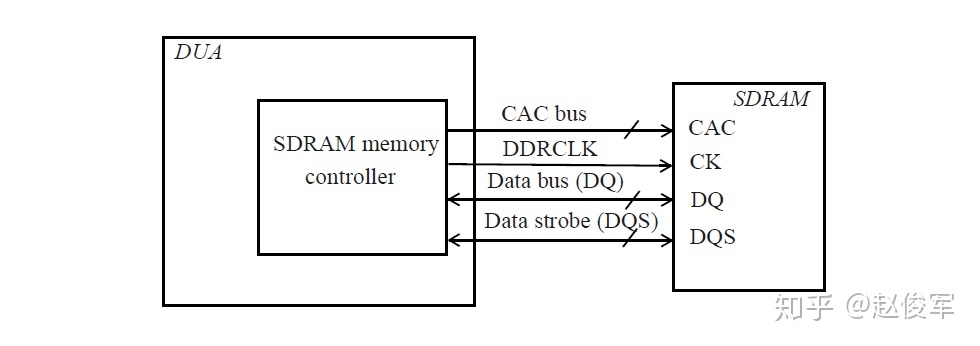

DDR SDRAM接口可以看作是上一节中所介绍的SRAM接口的一种扩展。就像SRAM接口一样,有两条主要的总线,图9-9说明了DUA和SDRAM之间的总线及其方向。由命令、地址和控制引脚(通常称为CAC)组成的第一条总线将使用以下标准方案:在存储器时钟的一个时钟沿(或每个时钟周期一次)处发送信息。双向总线由DQ(数据总线)和DQS(数据选通脉冲)组成,DDR接口的不同之处就在于双向数据选通DQS。DQS选通脉冲可用于一组数据信号,这使得数据信号(每字节一个或每半字节一个)与选通脉冲的时序紧密匹配。如果时钟是整个数据总线共用的时钟,那么使用时钟信号进行这种紧密匹配可能不可行。双向选通信号DQS可用于读操作和写操作,并且在选通脉冲的两个边沿(下降沿和上升沿,或称双倍数据速率)上都可捕获数据。在SDRAM的读模式期间,DQ总线与数据选通引脚DQS(而不是存储器的时钟引脚)同步,即DQ和DQS从SDRAM中被输出时彼此是对齐的。而对于另一个方向,即当DUA发送数据时,DQS将相移90度。请注意,数据DQ和选通DQS的沿均来自DUA内部的存储器时钟。

如上所述,对于一组DQ信号(4个或8个bit)存在一个数据选通DQS。这样做是为了使DQS和DQ的所有bit之间的偏斜平衡(skew balancing)要求更容易满足。例如,如果对于一个字节使用一个DQS,则一组中只需平衡9个信号(8个DQ和1个DQS),这比平衡72位的数据总线和时钟要容易得多。

上面的描述并不是对DDR SDRAM接口的完整说明,但足以说明这种接口的时序要求。

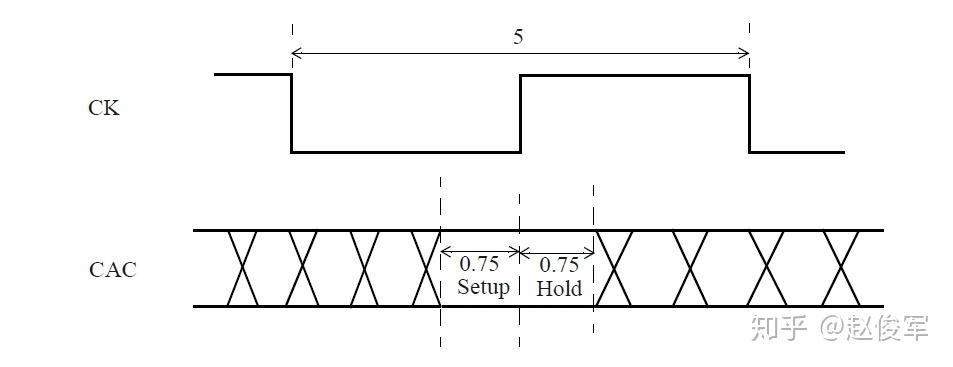

图9-10显示了典型DDR SDRAM接口中CAC总线(在DUA处)的AC特性。

上述建立时间和保持时间的要求对应到CAC总线上的接口约束如下所示:

-

create_generated_clock -name DDRCLK -source [get_pins UPLL0/CLKOUT] -divide_by 1 [get_ports DDRCLK]

-

set_output_delay -max 0.75 -clock DDRCLK [get_ports CAC]

-

set_output_delay -min -0.75 -clock DDRCLK [get_ports CAC]

在某些情况下,尤其是与无缓冲(unbuffered)存储器模块接口时,地址总线可能会比时钟驱动更大的负载。在这种情况下,地址信号对存储器的延迟要比时钟信号大,并且这种延迟差异可能会导致AC特性不同于图9-10中所示。

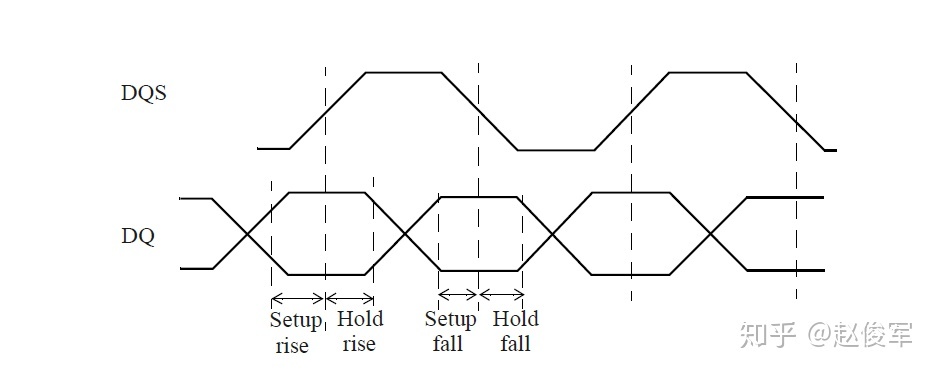

DQS和DQ的对齐方式在读周期和写周期中有所不同,以下小节将对此进行进一步探讨。

9.3.1 读周期

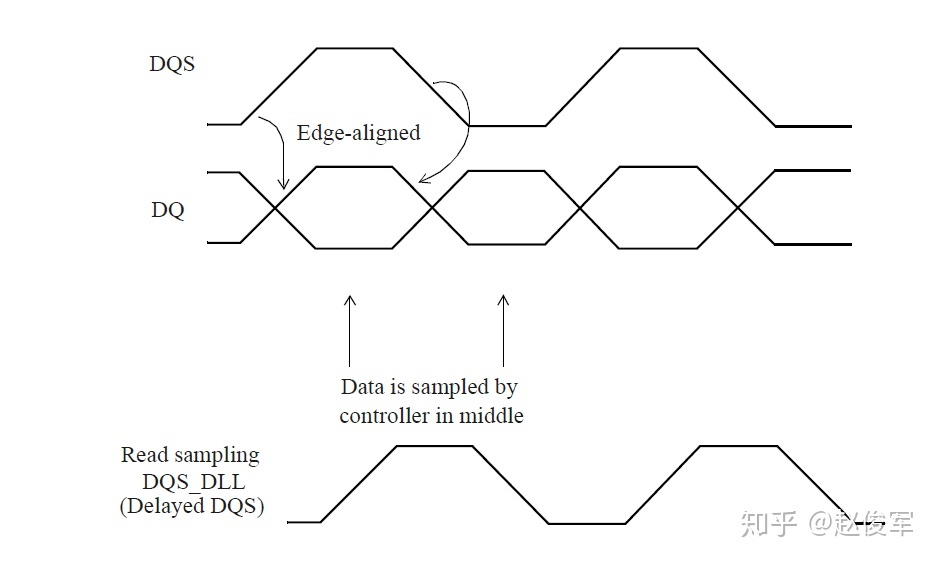

在读周期中,存储器输出的数据与DQS是边沿对齐(edge-aligned)的,如图9-11中波形所示。图中的DQ和DQS代表存储器引脚上的信号。数据(DQ)由存储器在DQS的每个沿上发出,并且DQ改变数据的时刻也与DQS的下降沿和上升沿对齐。

由于DQS选通信号和DQ数据信号彼此对齐,因此DUA内部的存储控制器(memory controller)通常使用DLL(或其它替代方法来实现四分之一周期延迟)来延迟DQS,从而使DQS的边沿对齐于数据有效窗口的中心。

即使DQ和DQS在存储器中彼此对齐,但DQ和DQS选通信号也可能无法再在DUA内部的存储控制器上对齐,这可能是由于IO缓冲器之间的延迟差以及PCB互连走线等因素所导致的。

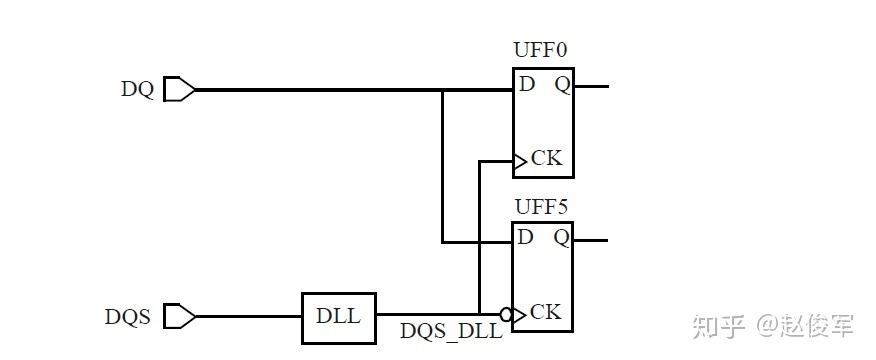

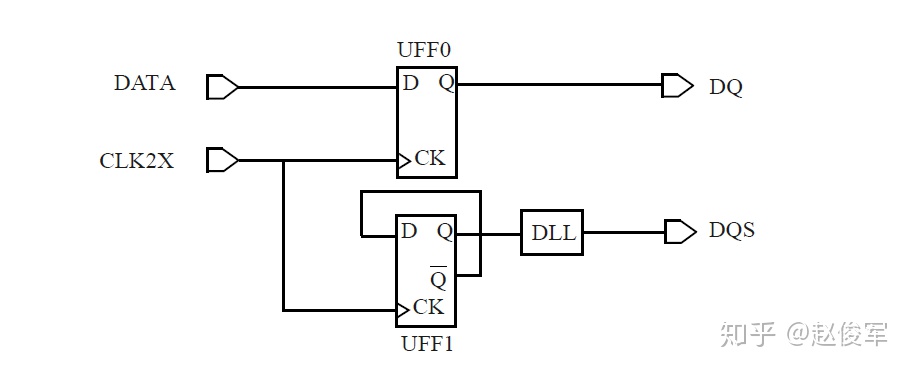

图9-12中为基本的数据读取原理图。上升沿触发的触发器在DQS_DLL的上升沿捕获数据DQ,而下降沿触发的触发器在DQS_DLL的下降沿捕获数据DQ。虽然图中的DQ路径上没有DLL,但某些设计可能在数据路径上也会放置一个DLL。这样可以用来延迟信号(以解决由于PVT或互连走线长度或其它差异引起的变化),以便可以在数据有效窗口的中间准确地采样数据。

为了对存储控制器上的读接口进行约束,我们在DQS上定义了一个时钟,并相对于该时钟在数据上指定了输入延迟。

- create_clock -period 5 -name DQS [get_ports DQS]

假定存储器读接口以200MHz(当在两个时钟沿上都传输数据时相当于400Mbps)的频率进行工作,这对应于每2.5ns采样一次DQ数据信号。由于数据是在两个边沿上捕获的,因此需要为每个边沿分别指定输入约束。

-

set_input_delay 0.4 -max -clock DQS [get_ports DQ]

-

set_input_delay -0.4 -min -clock DQS [get_ports DQ]

-

set_input_delay 0.35 -max -clock DQS -clock_fall [get_ports DQ]

-

set_input_delay -0.35 -min -clock DQS -clock_fall [get_ports DQ]

-

set_multicycle_path 0 -setup -to UFF0/D

-

set_multicycle_path 0 -setup -to UFF5/D

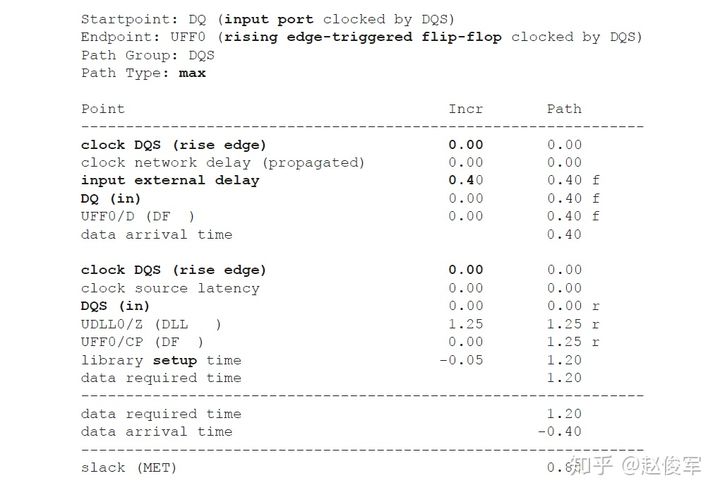

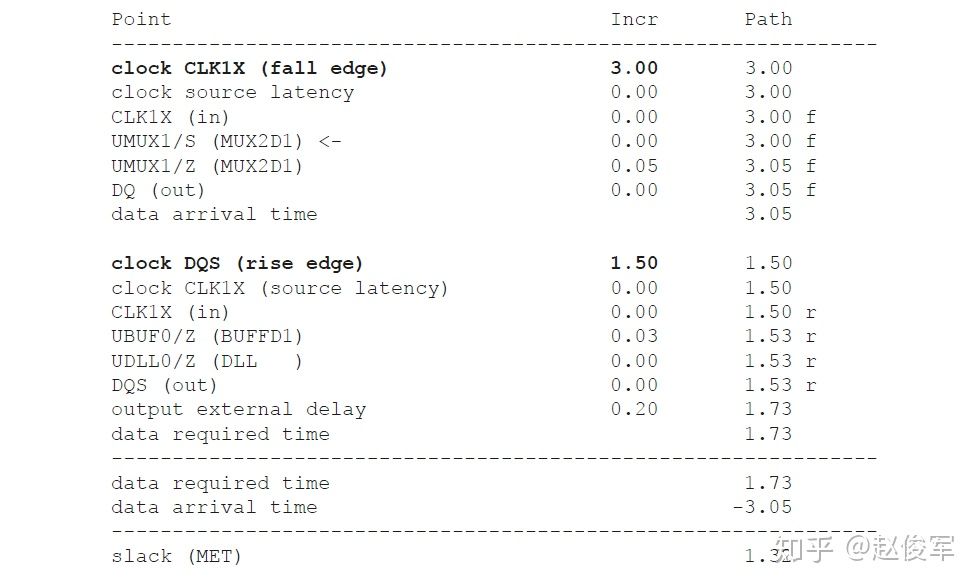

输入延迟命令指定了DUA引脚上DQ和DQS沿之间的延迟差,即使这两个信号通常是从存储器中同时输出的,但由于不同存储器的规格,在时序上仍会存在偏差。因此,DUA内的控制器设计应考虑到两个信号之间可能存在偏斜(skew)。以下是两个触发器建立时间检查的路径报告。假设捕获触发器的建立时间要求为0.05ns、保持时间要求为0.03ns,且DLL延迟设置为1.25ns,即四分之一周期。

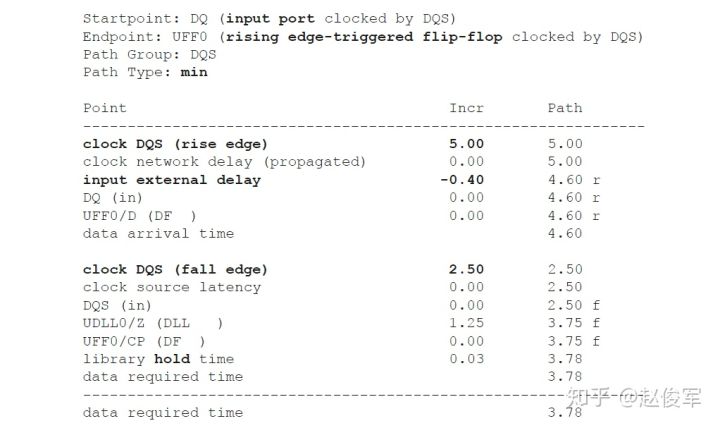

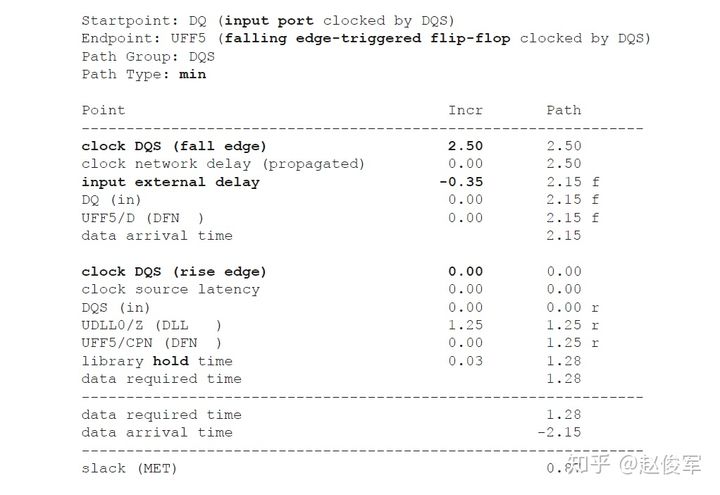

以下是保持时间检查的路径报告:

9.3.2 写周期

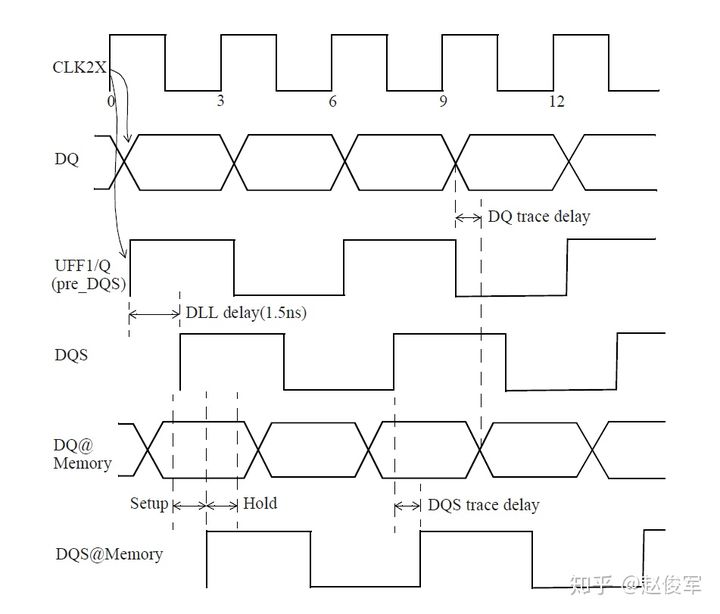

在写周期中,DQS沿会与从DUA内存储控制器输出的DQ信号相差四分之一周期,因此存储器可以直接使用DQS选通脉冲去捕获数据。

图9-13显示了存储器引脚上所需的波形,在存储器引脚处,DQS信号必须与DQ数据窗口的中心对齐。请注意,仍然是由于IO缓冲器延迟不匹配或者PCB互连走线的变化,仅在存储控制器(DUA内部)中对齐DQ和DQS还不足以使这些信号在SDRAM存储器引脚处真正的对齐。因此,DUA通常在写周期中使用额外的DLL去进行控制,以实现DQS和DQ信号之间所需的四分之一周期偏移(offset)。

如何约束此模式的输出取决于控制器中时钟的生成方式,接下去我们考虑两种不同情况。

情况1:内部二倍频时钟

如果内部时钟是DDR时钟频率的两倍,则输出逻辑可以类似于图9-14中所示。DLL提供了一种必要时使DQS时钟偏斜的机制,从而满足存储器引脚上的建立时间和保持时间要求。在某些情况下,可以不使用DLL,而是使用负沿触发的触发器来获得90度的偏移。

对于图9-14中所示情况,可以进行如下输出延迟约束:

-

create_clock -period 3 [get_ports CLK2X]

-

create_generated_clock -name pre_DQS -source CLK2X -divide_by 2 [get_pins UFF1/Q]

-

create_generated_clock -name DQS -source UFF1/Q -edges {1 2 3} -edge_shift {1.5 1.5 1.5} [get_ports DQS]

DQ输出引脚上的时序必须相对于衍生时钟DQS进行约束。

假设DDR SDRAM的DQ和DQS引脚之间建立时间要求分别为DQ上升沿的0.25ns和下降沿的0.4ns。类似地,假设DQ引脚上升沿和下降沿的保持时间要求分别为0.15ns和0.2ns。DQS输出上的DLL延迟已设置为四分之一周期,即1.5ns,所有波形如下图9-15所示:

-

set_output_delay -clock DQS -max 0.25 -rise [get_ports DQ]

-

set_output_delay -clock DQS -max 0.4 -fall [get_ports DQ]

-

set_output_delay -clock DQS -min -0.15 -rise [get_ports DQ]

-

set_output_delay -clock DQS -min -0.2 -fall [get_ports DQ]

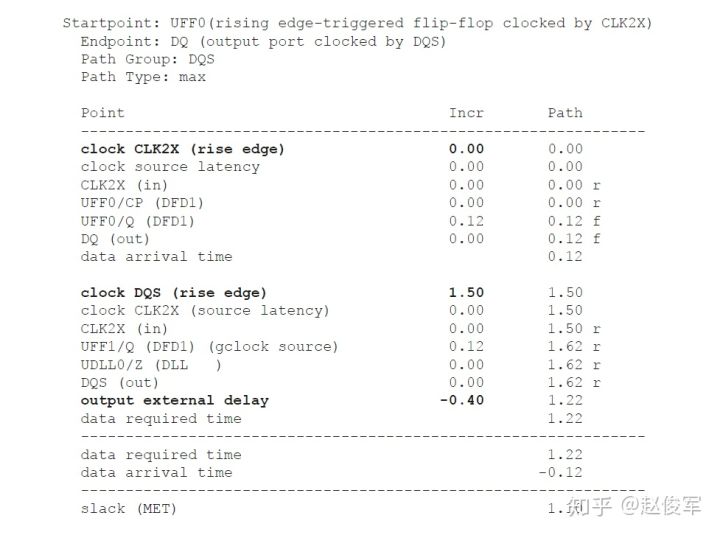

以下是通过输出DQ路径的建立时间检查报告。建立时间检查从0ns处发起DQ的CLK2X上升沿到1.5ns处的DQS上升沿进行。

请注意,上述报告中的四分之一周期延迟出现在了时钟DQS上升沿的第一行中,而不是在DLL实例UDLL0的那行中。这是因为DLL延迟已被建模为了衍生时钟DQS定义的一部分,而不是DLL时序弧中的一部分。

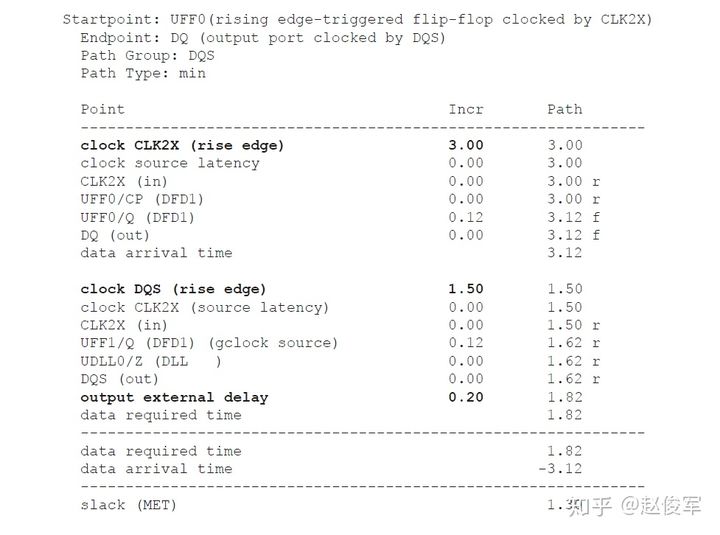

以下是通过输出DQ路径的保持时间检查报告。保持时间检查从3ns处发起DQ的时钟CLK2X上升沿到1.5ns处的DQS前一个上升沿。

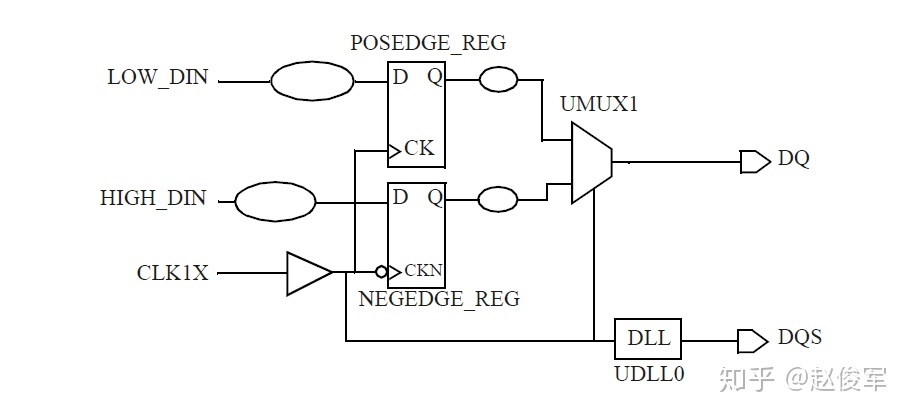

情况2:内部一倍频时钟

当内部只有一倍频时钟可用时,输出电路通常可能类似于图9-16所示的电路。

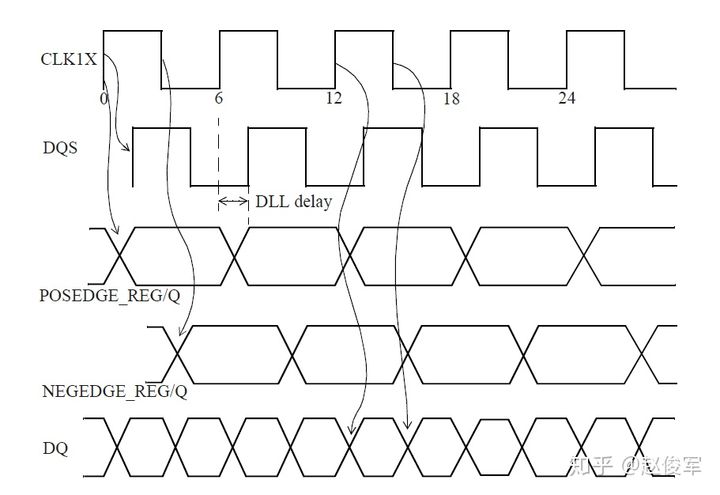

有两个触发器用于生成DQ数据:第一个触发器NEGEDGE_REG由时钟CLK1X的负沿触发,而第二个触发器POSEDGE_REG由时钟CLK1X的正沿触发。每个触发器会锁存适当的边沿数据,然后使用CLK1X作为多路复用器的选择信号来多路复用该数据:CLK1X为高电平时,触发器NEGEDGE_REG的输出发送到DQ;而当CLK1X为低电平时,触发器POSEDGE_REG的输出发送到DQ。因此,数据会在时钟CLK1X的两个边沿都到达输出DQ。请注意,每个触发器都有半个周期将数据传播到多路复用器的输入端,以确保在由CLK1X边沿选择输入数据之前,已在多路复用器的输入端口上准备好了输入数据。相关波形如图9-17所示。

这种情况的输出延迟约束如下:

-

create_clock -name CLK1X -period 6 [get_ports CLK1X]

-

create_generated_clock -name DQS -source CLK1X -edges {1 2 3} -edge_shift {1.5 1.5 1.5} [get_ports DQS]

-

set_output_delay -max 0.25 -clock DQS [get_ports DQ]

-

set_output_delay -max 0.3 -clock DQS -clock_fall [get_ports DQ]

-

set_output_delay -min -0.2 -clock DQS [get_ports DQ]

-

set_output_delay -min -0.27 -clock DQS -clock_fall [get_ports DQ]

建立时间和保持时间检查可验证从多路复用器到输出的时序。建立时间检查之一是从多路复用器输入处的CLK1X上升沿(发起NEGEDGE_REG数据)到DQS的上升沿。另一个建立时间检查是从多路复用器输入处的CLK1X下降沿(发起POSEDGE_REG数据)到DQS的下降沿。同样,保持时间检查是从(与建立时间检查)相同的CLK1X边沿到DQS的前一个下降沿或上升沿。

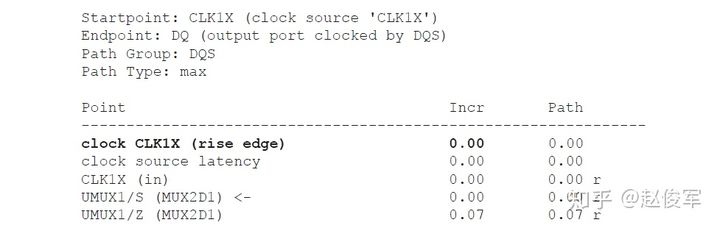

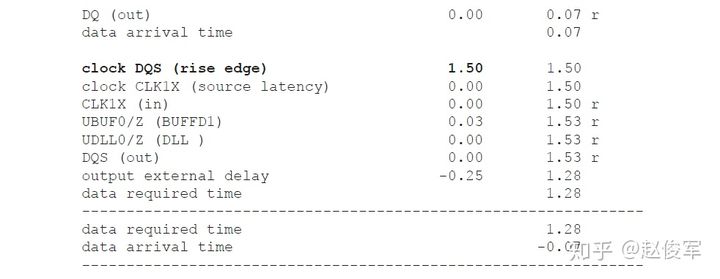

以下是通过DQ端口的建立时间检查报告,该检查在(选择输出NEGEDGE_REG的)CLK1X的上升沿和DQS的上升沿之间进行。

这是通过DQ端口的另一个建立时间检查报告,该检查在(选择输出POSEDGE_REG的)CLK1X的下降沿和DQS的下降沿之间进行。

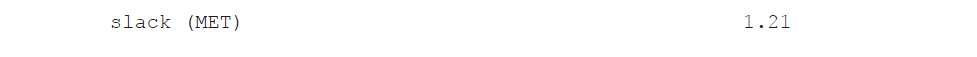

这是通过DQ端口的保持时间检查报告,该检查在CLK1X的上升沿和DQS的前一个下降沿之间进行。

这是另一个通过DQ端口的保持时间检查报告,该检查在CLK1X的下降沿和DQS的前一个上升沿之间进行。

尽管以上接口时序分析已忽略了任何负载对输出的影响,但我们也可以指定额外的负载(使用set_load命令)来提高准确性。STA同样可以通过电路仿真来补充,以实现可靠的DRAM时序。

DDR接口的DQ和DQS信号通常在读模式和写模式下使用终端电阻ODT(On-Die Termination),以减少由于DRAM和DUA处的阻抗不匹配而引起的任何反射(reflection)。在使用ODT的情况下,用于STA的时序模型将无法提供足够的精度。设计人员可以使用另一种机制,例如详尽的电路级仿真,来验证信号完整性和DRAM接口的时序。

9.4 DAC接口

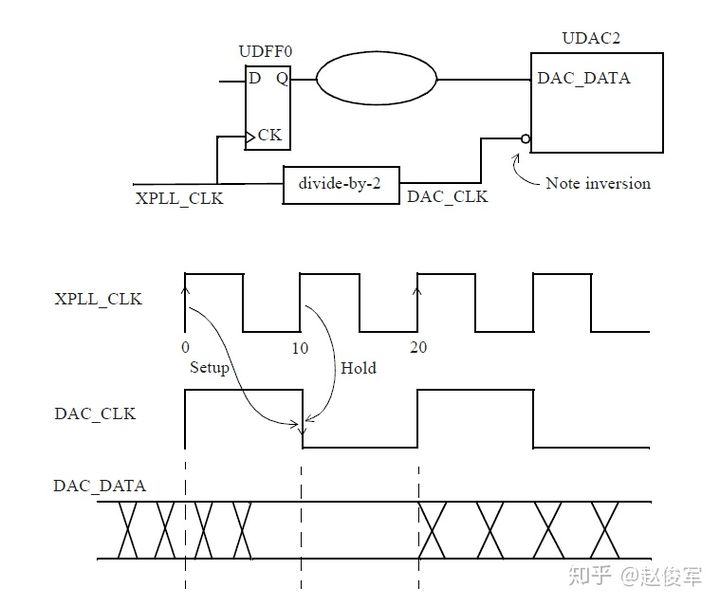

考虑下图9-18的一个典型DAC接口,其中高速时钟将数据传输到DAC的低速时钟接口。

时钟DAC_CLK是时钟XPLL_CLK的2分频,DAC建立时间和保持时间检查针对的是DAC_CLK的下降沿。

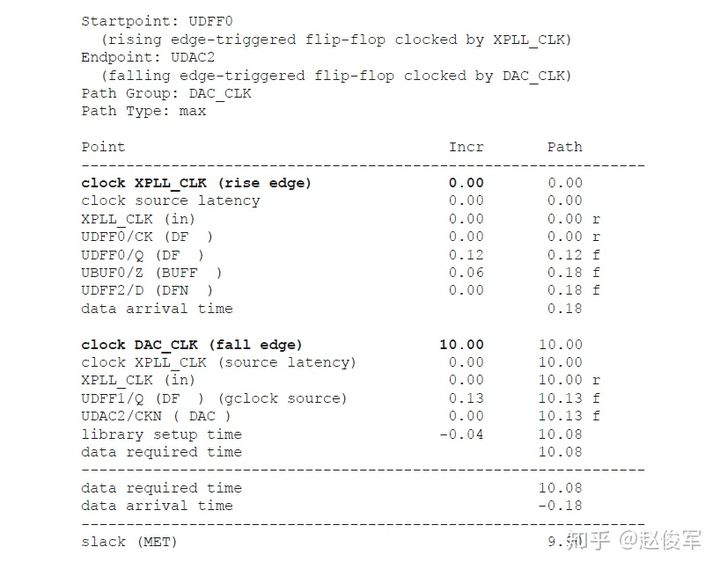

在这种情况下,即使可以根据需要将从快时钟域到慢时钟域的接口指定为多周期路径,但也可以将建立时间视作单周期(XPLL_CLK)路径。如图9-18所示,XPLL_CLK的上升沿发起数据,而DAC_CLK的下降沿捕获数据。以下是建立时间检查的路径报告:

请注意,该接口是从较快的时钟域到较慢的时钟域,因此如有必要,完全可以将其设置为两周期路径。

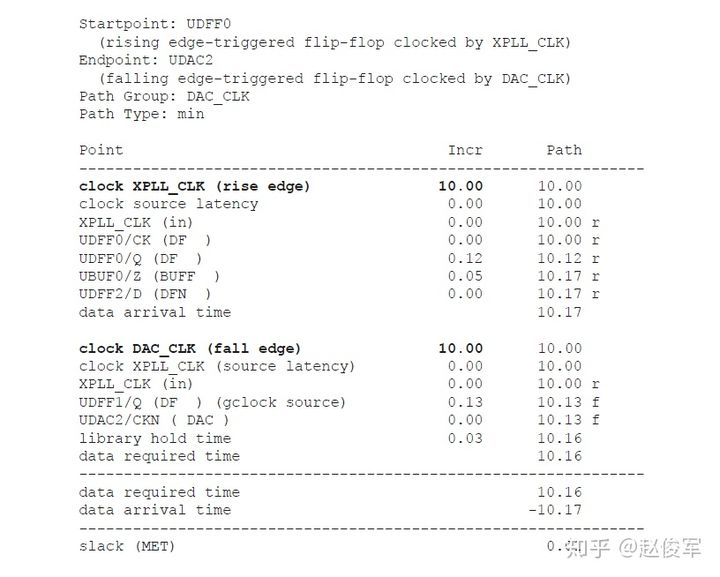

以下是保持时间检查的路径报告:

保持时间检查是在建立时间捕获沿之前一个周期完成的。在这种接口情况下,最关键的保持时间检查是在发起沿和捕获沿重合处执行的,这在以上保持时间检查的报告中可以看出。

浙公网安备 33010602011771号

浙公网安备 33010602011771号