【第六章:串扰噪声 上】静态时序分析圣经翻译计划

本文由知乎

赵俊军授权转载,知乎主页为https://www.zhihu.com/people/zhao-jun-jun-19

本章节介绍了纳米技术中ASIC的信号完整性(signal integrity)。

- 在深亚微米(submicron)技术中,串扰(crosstalk)在设计的信号完整性中起着重要作用,串扰噪声是指两个或多个信号之间无意间的耦合。相关的噪声和串扰分析技术,即毛刺分析和串扰分析,可用于静态时序分析中,这将在本章中进行介绍。这些技术可用于使ASIC稳定运行。

6.1 概述

噪声是指影响芯片正常运行的不良或无意的现象。在纳米技术中,噪声会影响功能或器件的时序。

为什么会有噪声和信号完整性?

噪声在深亚微米技术中起重要作用的原因有以下几个:

- 金属层数量的增加:例如,一个0.25um或0.3um的工艺具有四个或五个金属层,而在65nm和45nm工艺中增加到了十个或更多的金属层。章节四中的图4-1已描绘过了金属互连线的多层结构。

- 垂直占主导地位的金属长宽比:这意味着走线既细又高,与早期工艺几何形状中比较宽不同。因此,较大比例的电容是由侧壁耦合电容组成的,该侧壁耦合电容即为相邻信号线之间的走线间电容。

- 更高的布线密度:由于具有更精细的几何形状,更多的金属线可以在物理上紧密相邻。

- 大量的交互设备和互连线:在同一硅片面积中封装了更多的标准单元和信号走线,从而导致更多的交互。

- 由于频率变高而导致波形切换加快:快速的边沿速率会导致更多的电流尖峰以及对相邻走线和单元的更大耦合效应。

- 较低的电源电压:电源电压的降低使得噪声裕量较小。

在本章中,我们特别研究串扰噪声的影响。串扰噪声是指两个或多个信号之间无意识的耦合。串扰噪声是由芯片上相邻信号之间的电容耦合引起的,这会导致一个网络的高低电平切换,从而对耦合信号产生意外影响。受影响的信号称为受害者(victim),而产生影响的信号称为攻击者(aggressor)。请注意,两个耦合的网络可能会相互影响,并且通常一个网络可能既是受害者又是攻击者。

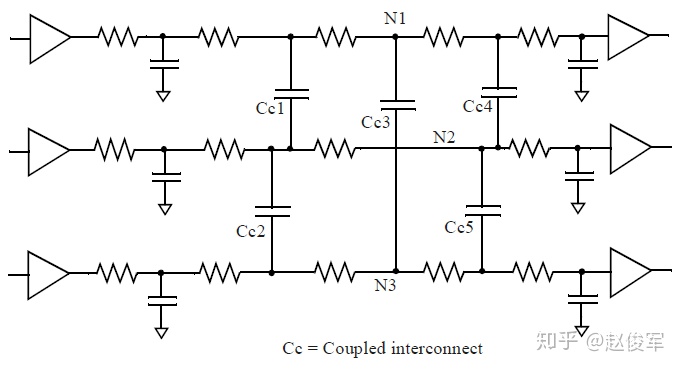

图6-1给出了几个信号走线耦合在一起的示例,图中描绘了提取得到的耦合互连的分布式RC以及几个驱动单元和扇出单元。在此示例中,网络N1和N2之间的耦合电容为Cc1 + Cc4,而Cc2 + Cc5是网络N2和N3之间的耦合电容。

广泛地讲,串扰会带来两种类型的噪声效应:毛刺(glitch)是指由于相邻攻击者电平切换的耦合而在稳定受害者信号上产生的噪声;以及由于受害者电平切换与攻击者电平切换的耦合而导致的时序变化(串扰增量延迟)。接下去的两小节将介绍这两种类型的串扰噪声。

6.2 串扰毛刺分析

6.2.1 基础

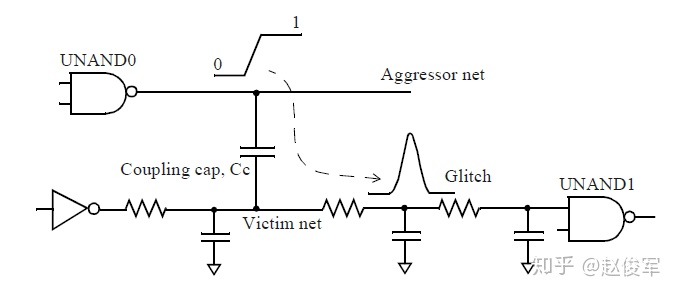

一个稳定的信号网络可能会由于攻击者电平切换时通过耦合电容转移的电荷而产生毛刺(正或负)。图6-2所示为攻击者网络上升沿电平切换的串扰引起的正毛刺。将两个网络之间的耦合电容描绘为一个集总(lumped)电容Cc而不是分布式(distributed)耦合电容,这是为了简化下面的说明,而又不失一般性。在提取所得网表的典型表示中,耦合电容可以分布在多个段中,如之前6.1节中所示。

在此示例中,与非门单元UNAND0电平切换并为其输出网络充电(标记为“攻击者”)。一些电荷也通过耦合电容Cc转移到“受害”网络上,并导致正毛刺。转移的电荷量与攻击者和受害者之间的耦合电容Cc直接相关。向受害网络的接地电容上转移的电荷会导致该网络上的毛刺。由于通过驱动单元INV2的下拉(pull-down)结构转移了电荷,因此可以恢复受害网络上的稳定值(在这种情况下为低电平)。

毛刺的幅度取决于多种因素,其中一些因素是:

- 攻击者与受害者之间的耦合电容:耦合电容越大,毛刺的幅度越大。

- 攻击者网络的压摆(slew):攻击者网络上的压摆越快,毛刺的幅度越大。通常,较快的压摆是因为驱动攻击者网络的单元具有较高的输出驱动强度。

- 受害者网络接地电容:受害者网络上的接地电容越小,毛刺的幅度越大。

- 受害者网络驱动强度:驱动受害者网络的单元输出驱动强度越小,毛刺的幅度越大。

总体而言,虽然受害者网络上的稳定值得以恢复,但由于以下原因,毛刺依然可能会影响电路的功能。

毛刺幅度可能足够大,以至于扇出单元可以将其视为不同的逻辑值(例如,受害者网络上的逻辑0可能在扇出单元处被视为逻辑1)。 这对于时序逻辑单元(触发器或锁存器)或存储器而言尤其重要,在这些单元中,时钟或异步置位/复位引脚上的毛刺会严重影响设计功能。类似地,锁存器输入端的数据信号出现毛刺会导致锁存不正确的数据,如果在输入数据时发生毛刺也可能造成灾难性的后果。

即使受害者网络不驱动时序逻辑单元,但也可能通过受害者网络的扇出传播较大的毛刺,并到达时序逻辑单元的输入,这将对设计造成灾难性的后果。

6.2.2 毛刺种类

毛刺具有许多不同种类:

上升和下降毛刺

前面小节中的讨论说明了受害者网络上的上升毛刺(Rise Glitch),该受害者网络一直稳定在低电平。类似的情况是在稳定的高电平信号上出现负毛刺,电平下降切换的攻击者网络会在稳定的高电平信号上引起下降毛刺(Fall Glitch)。

过冲和下冲毛刺

当上升的攻击者网络与稳定高电平的受害者网络耦合时会发生什么呢?仍会有一个毛刺使受害者网络的电压值超过其稳定的高电平,这种毛刺称为过冲毛刺(Overshoot Glitch)。类似地,下降的攻击者网络与稳定低电平的受害者网络耦合时,会在受害者网络上引起下冲毛刺(Undershoot Glitch)。

由串扰引起的所有四种毛刺情况如图6-3所示:

如前面小节所述,毛刺由耦合电容、攻击者的压摆和受害者网络的驱动强度决定。计算毛刺基于的是攻击者网络转移的电流量、受害者网络的RC互连 、以及驱动受害者网络的单元的输出阻抗。详细的毛刺计算是基于库模型的:相关的噪声模型是第3章中描述的标准单元库模型的一部分,3.7节中的输出dc_current模型与单元的输出阻抗有关。

6.2.3 毛刺阈值和传播

如何确定网络上的一个毛刺是否可以通过扇出单元传播?如前面的小节所述,由攻击者网络耦合引起的毛刺是否可以通过扇出单元传播,具体取决于扇出单元和毛刺属性(例如毛刺高度和毛刺宽度)。该分析可以基于直流(DC)或交流(AC)噪声阈值。直流噪声分析仅检查毛刺幅度并且比较保守,而交流噪声分析则检查其他属性,例如毛刺宽度和扇出单元输出负载。下面介绍了毛刺的直流和交流分析中使用的各种阈值标准。

直流阈值

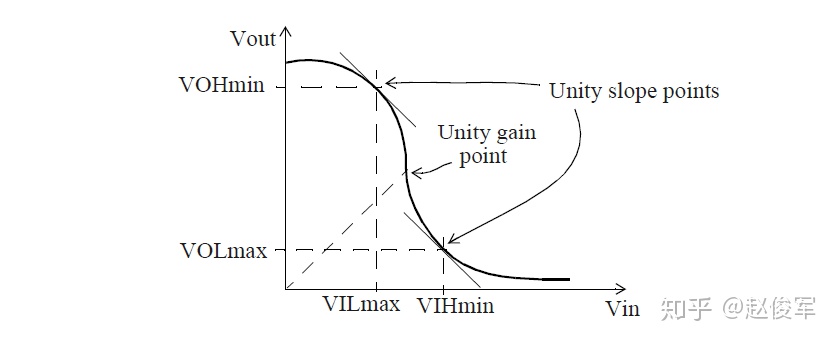

直流噪声裕度(DC noise margin)是对毛刺幅度的一种检查,是指在确保正确逻辑功能的同时输入单元的直流噪声限制。例如,只要反相器单元的输入保持在VIL最大值以下,则输出就可以保持为高电平(高于VOH最小值)。类似地,只要输入保持在VIH最小值以上,反相器单元的输出就可以保持为低电平(低于VOL最大值)。这些限制是基于单元的DC传输特性获得的,并且可以记录在单元库中。

VOH是被视为逻辑1或高电平的输出电压范围,VIL是被视为逻辑0或低电平的输入电压范围,VIH是被视为逻辑1的输入电压范围,VOL是被视为逻辑0的输出电压范围。图6-4给出了一个反相器单元的输入-输出DC传输特性图:

VILmax和VIHmin也称为DC裕度极限,基于VIH和VIL的DC裕度是稳态噪声极限,因此可以用作确定毛刺是否会通过扇出单元传播的判断依据。直流噪声裕量限制适用于单元的每个输入引脚。通常,DC裕度限制对于上升毛刺(输入低电平)和下降毛刺(输入高电平)是分开独立的。直流裕度的模型可以指定为单元库描述的一部分。低于直流裕度极限的毛刺(例如,低于扇出引脚的VILmax的上升毛刺)不能通过扇出传播,无论毛刺的宽度如何。因此,保守的毛刺分析会检查(所有毛刺)峰值电压电平是否满足扇出单元的VIL和VIH电平。即使有任何毛刺产生,只要所有网络都能满足扇出单元的VIL和VIH电平,就可以得出结论:毛刺对设计的功能没有任何影响(因为毛刺不会导致输出发生任何变化)。

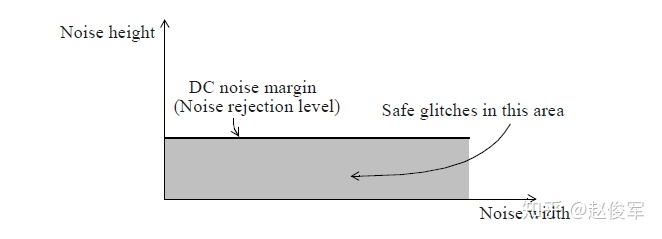

图6-5给出了DC裕量极限的示例。对于设计中的所有网络,DC噪声裕量可以固定为相同的极限值。可以设置最大可容忍的噪声(或毛刺)幅值,在此幅值之上,噪声可以通过单元传播到输出引脚。通常,此检查可保证毛刺电平小于VILmax或大于VIHmin。毛刺高度(height)通常表示为电源的百分比。 因此,如果将DC噪声裕量设置为30%,则表明任何高度大于电压摆幅30%的毛刺都将被标识为可能通过单元传播并影响设计功能的潜在毛刺。

并非所有幅度大于DC噪声裕量的毛刺都能改变单元的输出。毛刺的宽度也是确定毛刺是否会传播到输出的重要考虑因素。单元输入端的窄毛刺通常不会对单元输出产生任何影响。但是,DC噪声裕量仅使用恒定的最差高度值(worst-case value),而与信号噪声宽度无关。如图6-6中的示例提供了噪声抑制水平,该噪声抑制水平是单元噪声容限的非常保守的估计。

交流阈值

如以上小节所述,毛刺分析的DC裕度极限是保守的,因为是在最坏情况下分析设计的。DC裕量极限不检查毛刺宽度,也不会影响设计的正常运行。

在大多数情况下,设计可能无法通过保守的DC噪声分析。因此,必须针对毛刺宽度和单元的输出负载来验证毛刺的影响。通常,如果毛刺很窄或扇出单元的输出电容较大,则毛刺不会影响正常的功能运行。毛刺宽度和输出电容的影响都可以用扇出单元的惯性(inertia)来解释。通常,单级(single stage)的单元将阻止任何比通过该单元的延迟还要窄得多的输入毛刺。这是因为在毛刺较窄的情况下,毛刺会在扇出单元可以响应之前就结束了,因此,非常窄的毛刺对单元没有任何影响。由于输出负载会增加通过单元的延迟,因此增加输出负载的作用是使输入端的毛刺影响最小化,尽管这会增加单元延迟。

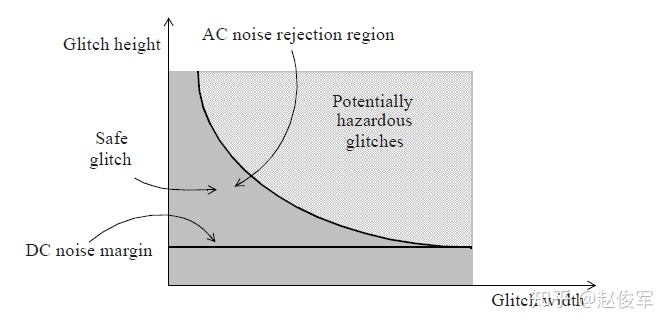

交流噪声抑制如图6-7所示(对于固定的输出电容)。黑色阴影区域表示良好或可接受的毛刺,因为这些毛刺太窄或太矮,或既窄又矮,因此对单元的功能行为没有影响。浅阴影区域表示不良或不可接受的毛刺,因为这些毛刺太宽或太高,或既宽又高,因此在单元输入端的这种毛刺会影响单元的输出。在毛刺较宽的极限情况下,毛刺阈值对应于DC噪声裕量,如图6-7所示。

对于给定的单元,增加输出负载会增加噪声容限,因为这会增加惯性延迟和可以通过单元的毛刺宽度,下面的示例说明了这种现象。图6-8(a)所示为一个未加负载的反相器单元,其输入端具有正毛刺。输入毛刺高于单元的直流裕量,因此会在其输出端引起毛刺。图6-8(b)中为相同的反相器单元,其输出端有一定负载。此时输入端相同的输入毛刺会导致输出端的毛刺小很多。如果反相器单元的输出负载更高,如图6-8(c)所示,则反相器单元的输出将没有任何毛刺。因此,增加输出端的负载可使单元更加能够抵抗从输入端传播到输出端的噪声。

如上所述,可以忽略低于AC阈值的毛刺(图6-7中的AC噪声抑制区域),或者可以认为扇出单元不受这种毛刺的影响。AC阈值区域是取决于输出负载和毛刺宽度的。如第3章中所述,抗扰度模型(noise immunity model)包括上述AC噪声抑制的影响,3.7节中介绍的propagated_noise模型除了对通过单元的传播进行建模外,还包括了AC噪声阈值的影响。

如果毛刺大于AC阈值会怎么样?在毛刺幅度超过AC阈值的情况下,单元输入处的毛刺会在单元输出处产生另一种毛刺。输出毛刺的高度和宽度是输入毛刺的宽度、高度以及输出负载的函数。该信息在单元库中进行了表征,该单元库中包含了有关输出毛刺幅度和宽度的详细表格或函数,并且这些函数是输入引脚的毛刺幅度、毛刺宽度和输出引脚负载的函数。毛刺传播会在库中的propagated_noise模型进行描述,第3章中已详细介绍了propagated_noise模型。

我们在上述内容中,对扇出单元输出处的毛刺(以及毛刺的传播)进行了计算,并在扇出网络上进行了相同的检查,依此类推。

尽管我们在上面的讨论中使用了通用术语“毛刺”,但应注意,这分别适用于前一小节中提到的所有类型的毛刺:上升毛刺(由早期模型中的propagated_noise_high或noise_immunity_high建模),下降毛刺(由早期模型中的propagated_noise_low或noise_immunity_low建模),过冲毛刺(由noise_immunity_above_high建模)和下冲毛刺(由noise_immunity_below_low建模)。

总而言之,单元的不同输入对毛刺阈值有不同的限制,这是毛刺宽度和输出电容的函数,对于输入高电平(向低电平过渡的毛刺)和输入低电平(向高电平过渡的毛刺),这些限制是独立的。噪声分析检查毛刺峰值以及宽度,并分析是否可以忽略或是否可以传播到扇出。

6.2.4 多攻击者的噪声累积

图6-9介绍了由于单个攻击者网络电平切换而在受害者网络上引入串扰毛刺的耦合。通常,受害者网络可以电容耦合到许多网络。当多个网络同时电平切换时,由于有多个攻击者,对受害者网络的串扰耦合噪声影响会更加严重。

大多数由多个攻击者网络引起的耦合分析都考虑了每个攻击者网络引起的毛刺效应,并计算了对受害者网络的累积效应,这看起来很保守,但这确实表明了受害者网络的最坏情况。另一种方法是使用RMS(均方根)方法,使用RMS方法时,是通过单个攻击者网络引起的毛刺的均方根来计算受害者网络的毛刺幅度的。

6.2.5 多攻击者的时序相关性

对于由多个攻击者引起的串扰,分析时必须考虑攻击者网络的时序相关性,并确定多个攻击者是否可以同时电平切换。STA会从攻击者网络的时序窗口获取此信息。在时序分析过程中,将获得网络的最早(earliest)和最迟(latest)电平切换时间,这些时间表示网络可以在一个时钟周期内切换的时序窗口。电平切换窗口(上升和下降)提供了有关攻击者网络是否可以一起切换的必要信息。

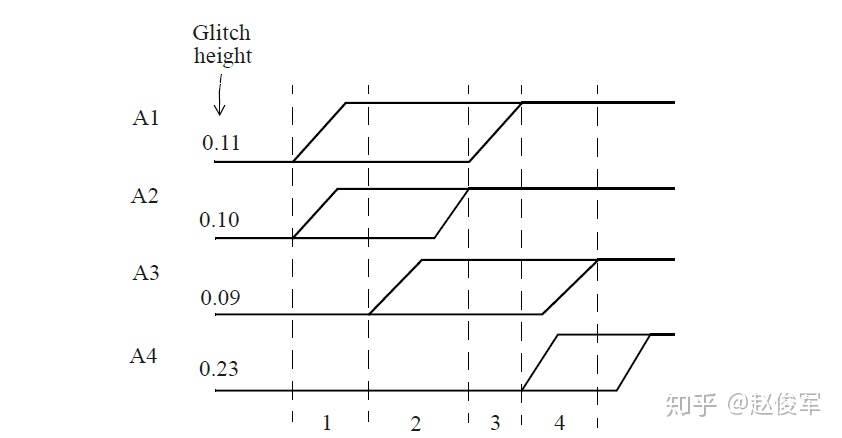

根据多个攻击者是否可以同时电平切换,将决定是否要合并单个攻击者对受害者网络带来的毛刺。第一步,毛刺分析为每个潜在的攻击者分别计算四种毛刺(上升、下降、下冲和过冲)。下一步将来自各个单独攻击者的毛刺带来的影响合并在一起,多个攻击者可以针对每种不同类型的毛刺分别进行组合。例如,考虑与攻击者网络A1、A2、A3和A4耦合的受害者网络V。在分析过程中,可能A1、A2和A4会引起上升和过冲毛刺,而只有A2和A3会造成下冲和下降毛刺。

考虑另一个示例,当四个攻击者网络中任何一个电平切换时,都会引起上升毛刺。如图6-10所示为时序窗口和每个攻击者网络引起的毛刺幅度。基于时序窗口,毛刺分析确定了可能导致最大毛刺的最坏情况的攻击者组合。在此示例中,电平切换窗口可分为四个区域,其中每个区域都显示了可能进行电平切换的攻击者网络,每个攻击者所引起的毛刺幅度也如图6-10所示。区域1中攻击者网络A1和A2会进行电平切换,这可能导致毛刺幅度为0.21(= 0.11 + 0.10)。区域2中攻击者网络A1、A2和A3会进行电平切换,这可能导致毛刺幅度为0.30(= 0.11 + 0.10 + 0.09)。区域3中攻击者网络A1和A3会进行电平切换,这可能导致毛刺幅度为0.20(= 0.11 + 0.09)。区域4中攻击者网络A3和A4会进行电平切换,可导致0.32(= 0.09 + 0.23)的毛刺幅度。

因此,区域4具有0.32这个情况最差的毛刺幅度。请注意,不使用时序窗口进行的分析将预测总毛刺幅度为0.53(= 0.11 + 0.10 + 0.09 + 0.23),这可能过于悲观。

6.2.6 多攻击者的功能相关性

对于多个攻击者,时序窗口通过考虑不同网络可能进行电平切换的不同时间段来减少分析中的悲观度。另外,要考虑的另一个因素是各种信号之间的功能相关性。例如,扫描控制(scan control)信号仅在扫描模式(scan mode)下电平切换,并且在执行设计的正常功能或任务模式时保持稳定。因此,在功能模式期间,扫描控制信号不会在其它任何信号上引起毛刺,扫描控制信号只有在扫描模式期间才可能成为攻击者。在某些情况下,测试时钟和功能时钟是互斥的,因此只有在关闭功能时钟时,测试时钟才可以在测试期间处于有效状态。在这些设计中,由测试时钟控制的逻辑和由功能时钟控制的逻辑创建了两组独立且互不相干的攻击者。在这种情况下,测试时钟控制的攻击者无法与功能时钟控制的其它攻击者结合使用,以进行最坏情况的噪声计算。功能相关性的另一个示例是两个攻击者彼此互补(逻辑相反)。在这种情况下,信号及其互补信号不可能在同一方向上进行电平切换以进行串扰噪声计算。

图6-11中所示为网络N1与其它三个网络N2、N3和N4耦合的示例。在功能相关性分析中,需要考虑网络的功能。假设网络N4是一个常数(例如,一个模式设置网络),因此尽管其与网络N1耦合但不能成为网络N1的攻击者。假设网络N2是调试总线(debug bus)的一部分,其在功能模式时处于稳定状态。因此,网络N2也不可能成为网络N1的攻击者。假设网络N3传输功能数据,则只能将网络N3视为网络N1的潜在攻击者。

浙公网安备 33010602011771号

浙公网安备 33010602011771号