(今日迷惑)systemverilog定义数组时,定义方法不一致导致的错误

今日迷惑

我定义了一个类

class sdata;

bit [255:0] data [2048];

rand int data_t [2048][32];

rand bit mask [2048][32];

bit flag;

constraint c {

foreach (data_t[i,j]) data_t[i][j]< 5;

foreach (data_t[i,j]) data_t[i][j]>-5;

}

function void post_randomize();

if (flag) begin

for (int i = 0; i < 2048; i++) begin

for (int j = 0; j < 32; j++) begin

data[i][8*j+:8]=data_t[i][j]*mask[i][j];

end

end

end

endfunction

endclass : sdata

我想用它来初始化一个ram和一个数组,他们的定义分别是

bit [255:0] mem_fmap_in [2048];

reg [`FMAP_MEM_WD-1:0] ram [`FMAP_MEM_DEP-1:0];

初始化代码

sdata temp;

void'(temp.randomize());

mem_fmap_in=temp.data;

i_fmap_mem_in.ram=temp.data;

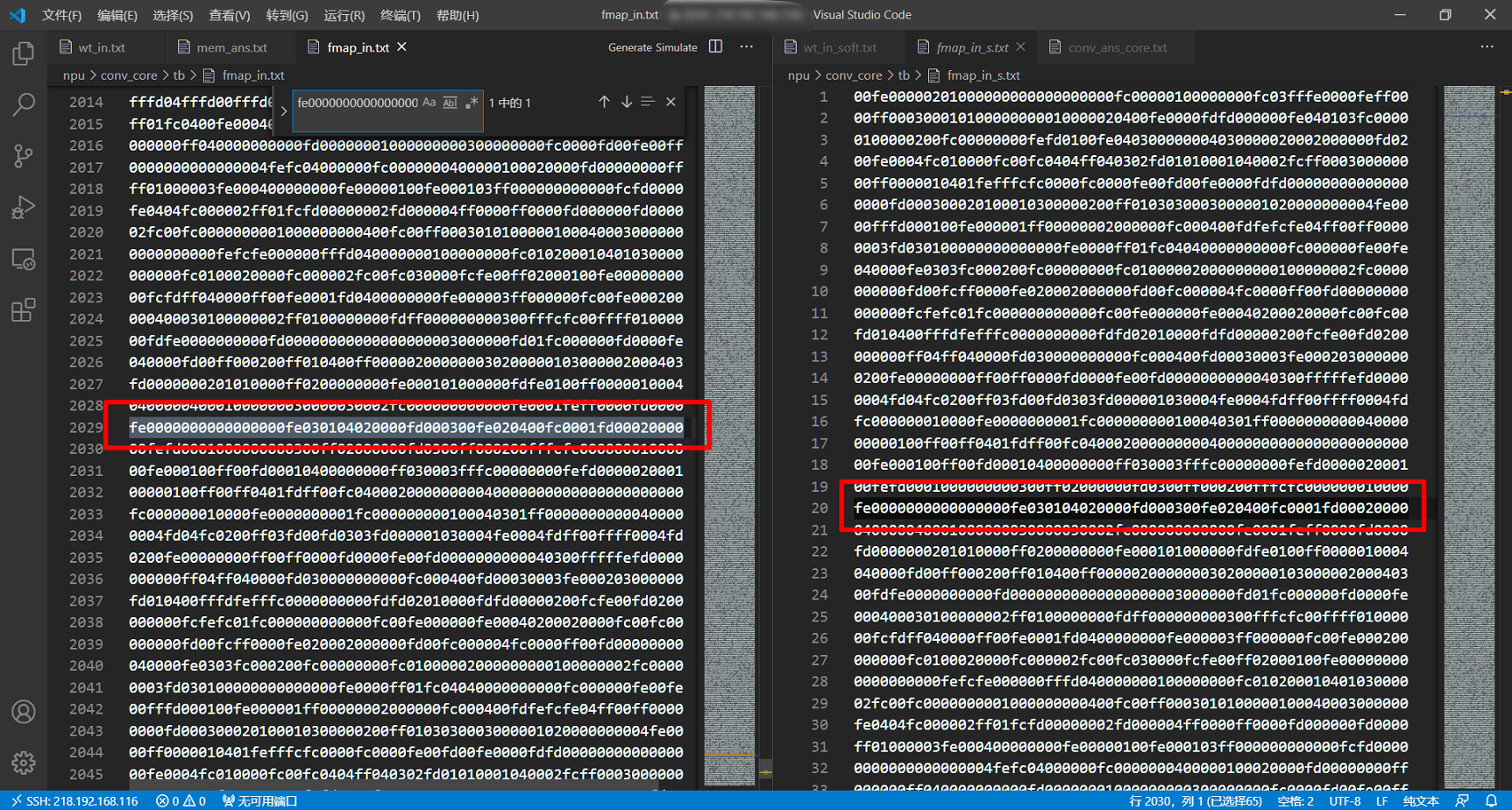

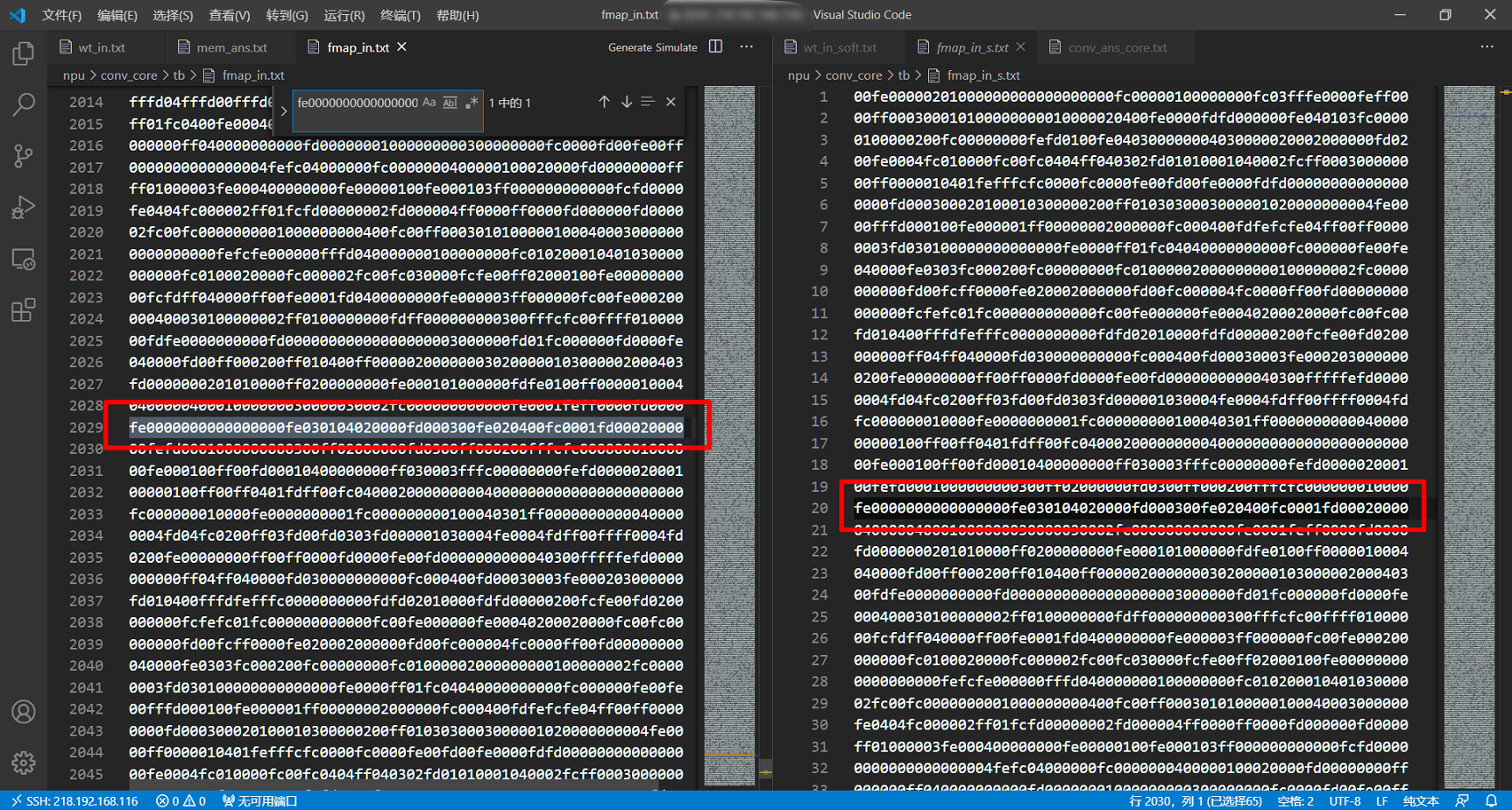

$writememh("fmap_in.txt",i_fmap_mem_in.ram);

$writememh("fmap_in_s.txt",mem_fmap_in);

结果导致,两者数据虽然都一样,但是数据顺序完全对不上

当我把初始化代码改成for循环以后,两者就一致了

for (int i = 0; i < 2048; i++) begin

mem_fmap_in[i]=temp.data[i];

i_fmap_mem_in.ram[i]=temp.data[i];

end

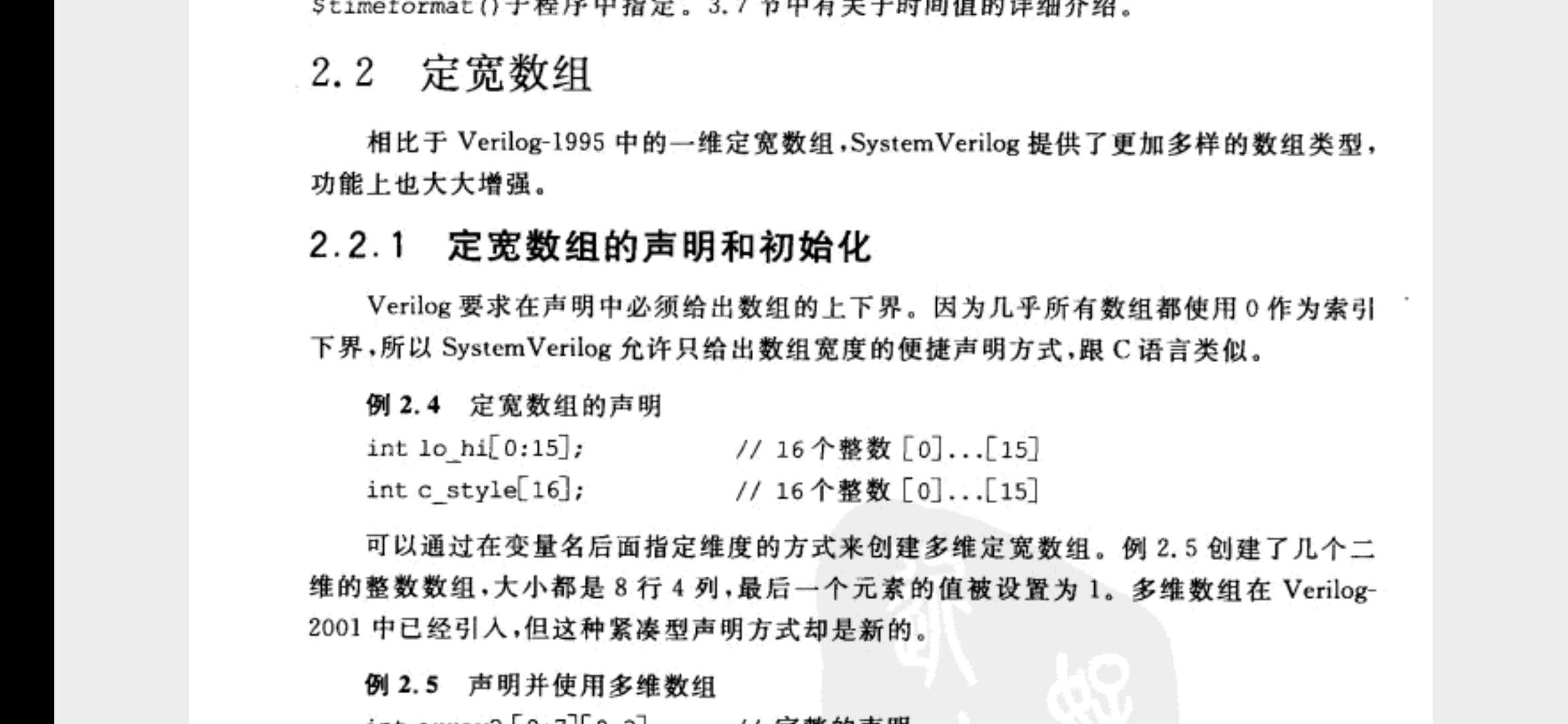

经过大佬指点,错误的原因在于,两者定义维度的时候不一致,bit [255:0] mem_fmap_in [2048];和bit [255:0] mem_fmap_in [2047:0];的索引顺序是不一致的,如果将我定义时的代码改成下面的一种,都能避免错误。

bit [255:0] mem_fmap_in [2047:0];

reg [`FMAP_MEM_WD-1:0] ram [`FMAP_MEM_DEP-1:0];

bit [255:0] mem_fmap_in [2048];

reg [`FMAP_MEM_WD-1:0] ram [`FMAP_MEM_DEP];

bit [255:0] mem_fmap_in [2048];

reg [`FMAP_MEM_WD-1:0] ram [0:`FMAP_MEM_DEP-1];

来自绿皮书的参考

做个实验

module tb ();

int a [3];

int b [2:0];

int c [0:2];

int d [3];

initial begin

for (int i = 0;i<3 ;i++ ) begin

a[i]=i;

end

b=a;

c=a;

d=a;

for (int i = 0;i<3 ;i++ ) begin

$display("a[%0d]:%0d b[%0d]:%0d c[%0d]:%0d d[%0d]:%0d",i,a[i],i,b[i],i,c[i],i,d[i]);

end

end

endmodule

输出是

a[0]:0 b[0]:2 c[0]:0 d[0]:0

a[1]:1 b[1]:1 c[1]:1 d[1]:1

a[2]:2 b[2]:0 c[2]:2 d[2]:2

保险起见,所有数组的维度定义要使用相同的方式,要么都是[3],要么都是[2:0],要么都是[0:2],不要混用

其实仔细观察数组的截图也会发现,整个顺序是完全颠倒过来的

这个坑害得我看了一个星期!!!!!!!

浙公网安备 33010602011771号

浙公网安备 33010602011771号