深入AXI4总线- [一]握手机制

知乎用户

ljgibbs授权转发

本系列我想深入探寻 AXI4 总线。不过事情总是这样,不能我说想深入就深入。当前我对 AXI总线的理解尚谈不上深入。但我希望通过一系列文章,让读者能和我一起深入探寻 AXI4。

声明1:部分时序图以及部分语句来自 ARM AMBA 官方手册

(有的时候感觉手册写得太好了,忍不住就直接翻译了。。)

声明2:AXI 总线是 ARM 公司的知识产权

备注:

-

下载手册可以到ARM官网搜AMBA ,需要注册 ARM 账号。官方手册developer.arm.com

-

百度文库应该有中文翻译版本。

VALID/READY 握手机制

AXI 总线共有 5 个独立的通道,分别为写地址、写数据、写回应、读地址、读数据通道。5 条通道相互独立,有一些细小的差别,但共同使用一套握手机制:VALID/READY 机制,来实现信息的传递。

VALID/READY 机制这个赛高啊,这个好啊,ARM 的手册上这么夸:

作为一种双向流控机制,VALID/READY 机制可以使发送接收双方都有能力控制传输速率。

在握手机制中,通信双方分别扮演发送方(Source)和接收方(Destination),两者的操作(技能)并不相同。

发送方置高 VALID 信号表示发送方已经将数据,地址或者控制信息已经就绪,并保持于消息总线上。

接收方置高 READY 信号表示接收方已经做好接收的准备。

当双方的 VALID/READY 信号同时为高,在时钟 ACLK 上升沿,完成一次数据传输。所有数据传输完毕后,双方同时置低自己的信号。

所谓的双向流控机制,指的是发送方通过置起 VALID 信号控制发送的时机与速度,接收方也可以通过 READY 信号的置起与否控制接收速度。

发送方拥有传输的主动权,但接收方在不具备接收能力时,也能够置低信号停止传输,反压发送方。

VALID/READY 的三种情况

VALID/READY 信号按照到达的先后顺序可以分为 3 种情况:

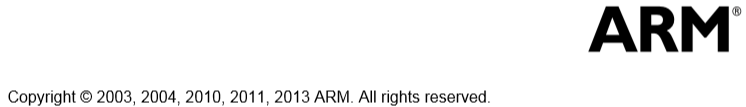

1.VALID 信号先到达

发送方 VALID 信号早早就到了,这时还不到 T2 时刻,并带来了新鲜的数据(数据通道),地址或者控制信息(地址通道),总之是信息(Information)。

但过了 T2 也没见到接收方的 READY 信号。原来是接收方还忙着,可能上一次的数据还没存完,还堵在数据通路上,忙过了 T2 才来。

好吧,那也行,T3 时刻传输完成。

在这种情况下,接收方通过 READY 信号控制了传输速度,反压了发送速度。

协议规定在这种情况下,VALID 信号一旦置起就不能置低,直到完成握手(handshake occurs),至少传输一周期数据。

在设计接收方逻辑时,检测到 VALID 信号置起,如果系统正忙,完全可以让发送方等待,发送方在完成传输之前都不会置低 VALID 信号,不需要考虑发送方撤销传输的可能。

协议另外规定:发送方不能通过等待接收方 READY 信号来确定置起 VALID 信号的时机

这句中文阅读理解有点难,原文为:

A source is not permitted to wait until READY is asserted before asserting VALID.

笔者个人理解,READY 信号可能先到达,如下图的情况。但是设计发送方逻辑时,不能将 READY 信号作为置高 VALID 逻辑的条件,比如将 READY 信号通过组合逻辑生成 VALID 信号。

换句话说,发送方准备发送,置起 VALID 信号是完全主动与独立的过程。接收方 READY 信号按照协议可以依赖发送方 VALID 信号,但如果此时发送方也依赖接收方信号,就会造成死锁的情况,所以协议在这里强调了 VALID 信号的主动性。

module axi_src

...

//assign VALID = SRC_CONDITION && READY;//NOT permitted and may cause deadlock

assign VALID = SRC_CONDITION;//permitted

...

endmodule

module axi_dst

...

assign READY = CONDITION && VALID;//permitted

...

endmodule

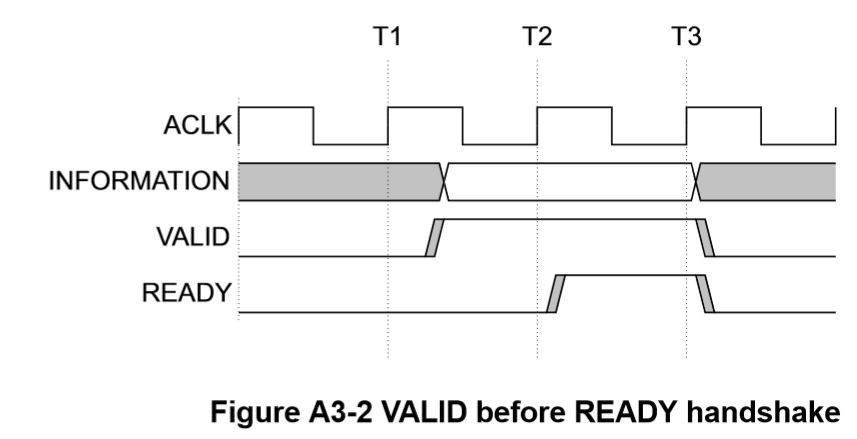

2.READY 信号先到达

READY 信号很自由,可以等待 VALID 信号到来再做响应,但也完全可以在 VALID 信号到来前就置高,表示接收端已经做好准备了。

而且,READY 信号与 VALID 不同,接收方可以置起 READY 之后发现:其实我好像还挺忙,然后置低 READY 信号。只要此时 VALID 信号没有置起,这种操作是完全可以。

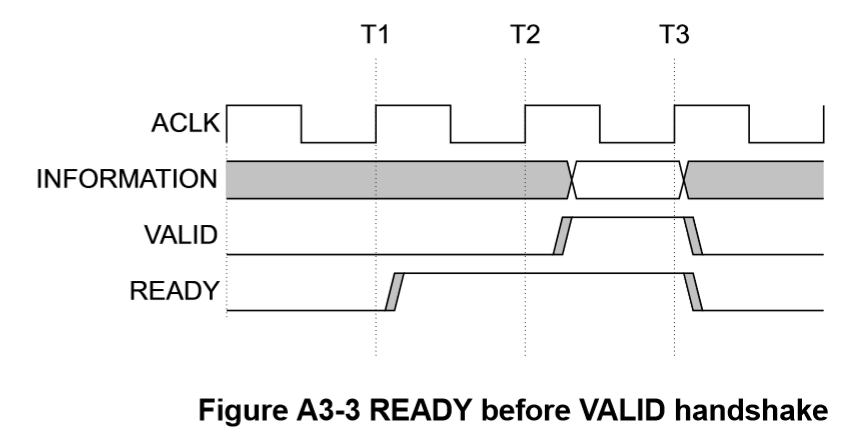

3.同时到达

同时到达就很简单,等到下一个时钟上升沿 T2,传输就这么轻松愉快地在一个时钟周期里完成了。

实现细节

本文的最后讨论一个协议的实现细节。如果读者仅仅想了解 AXI 协议的使用,那么每篇文章的实现细节章节可以跳过。这个章节面向有实现 AXI 协议需求的读者。

前文我们讨论过, READY 信号原则上由接收方自身的接收状况以及 VALID 信号控制。(或者仅由接收方自身的接收状况决定)协议中没有规定 READY 信号的默认状态,即未进行传输时的电平状态(default value)。

协议建议 AW/AR READY 信号(这里 AW/AR 指的是读写地址通道的 READY 信号,将在第二章中正式引入)的默认电平为高电平。若默认电平为低,则每次传输至少需要 2 个周期才能完成,第一个周期置高 VALID 信号,第二个周期从机才会置高 READY 信号。相当于每次传输增加 1 个周期时间开销,这在某些情况下会对传输效率有较大的影响。

浙公网安备 33010602011771号

浙公网安备 33010602011771号