《数字集成电路静态时序分析基础》笔记⑨

欢迎关注个人公众号摸鱼范式

网络课程《数字集成电路静态时序分析基础》的笔记

特殊时序检查-多时钟

所有讨论都是同步时钟,具有固定相位关系,异步时钟是没有时序检查的意义的

跨时钟域

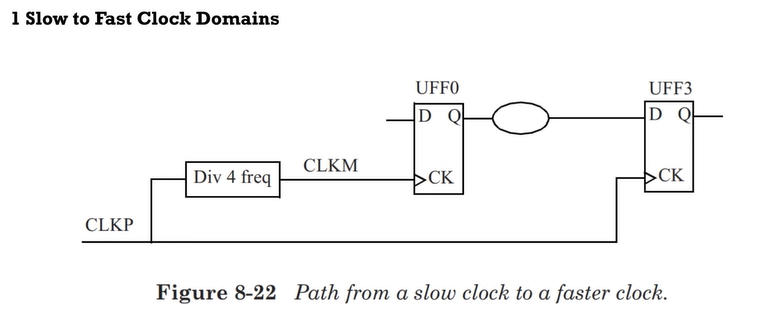

慢时钟域到快时钟域

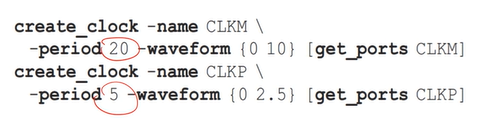

时钟约束,也可以使用generate

最严格的时序检查如下

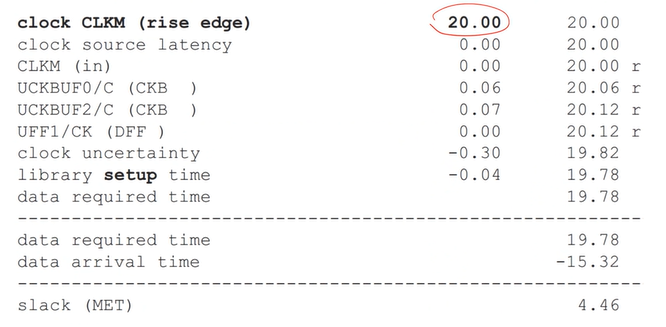

setup检查,发射路径

捕获路径

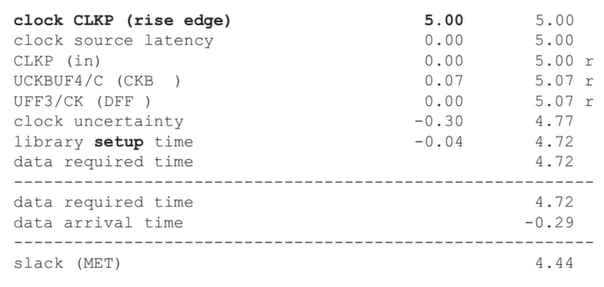

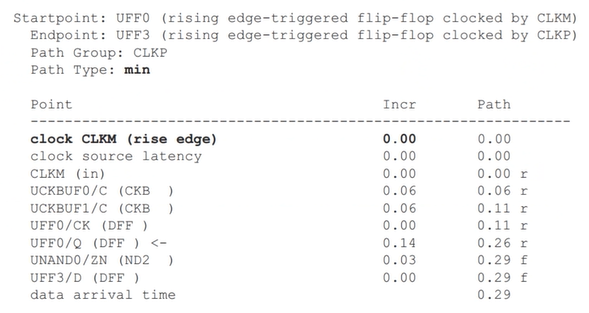

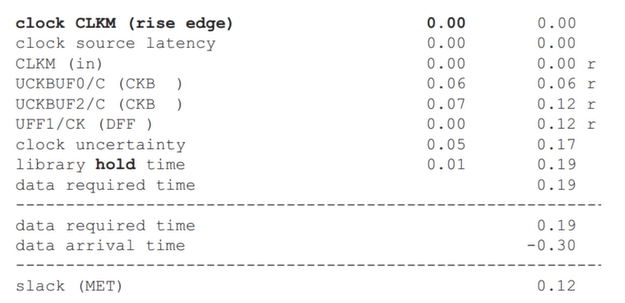

hold时序检查

慢时钟域的数据计算比较慢,用快时钟域来要求慢时钟域是不合理的,所以可以在第四个周期进行检查,这样可以放宽对慢时钟域的检查。注意要加上-end选项,因为这是对

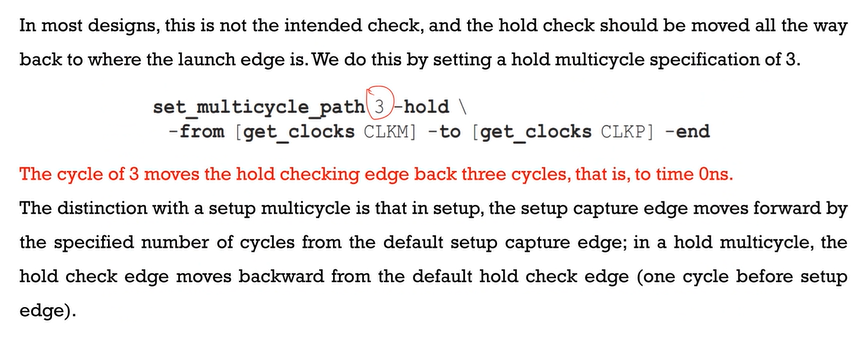

注意到默认hold检查边沿是setup的前一个

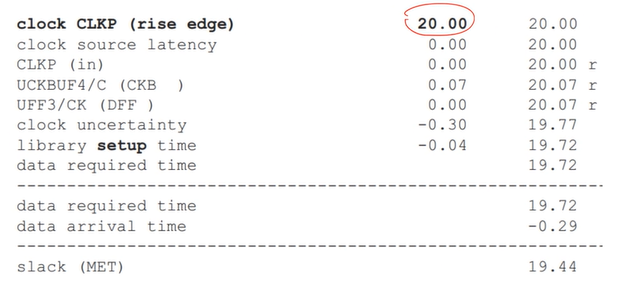

约束后的建立时间检查,捕获路径中的CLKP增加到20,也就是4倍

和多周期约束一样,对hold的默认检查也是不合理的

因此对hold也施加多周期约束

约束以后的检查边沿

总的来说,对于慢到快的检查,要对setup施加N的multicycle,对hold施加N-1的multicycle

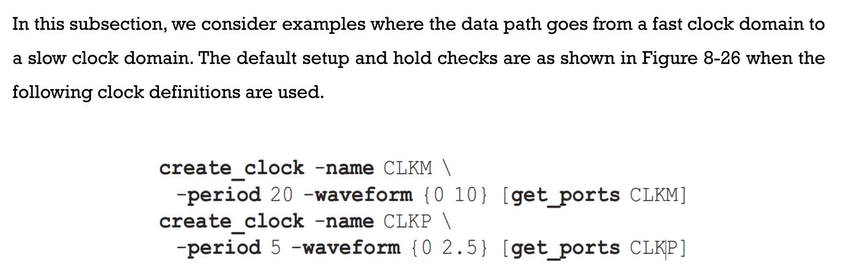

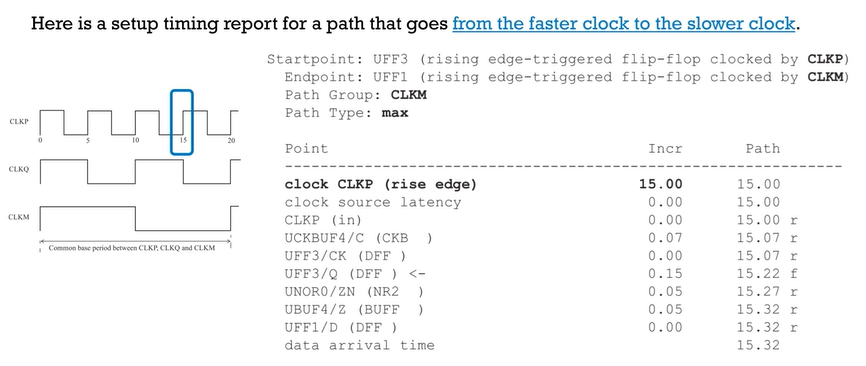

从快时钟域到慢时钟域

时钟定义如下

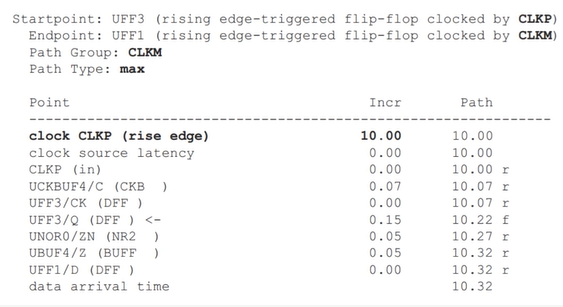

最严格的时序检查

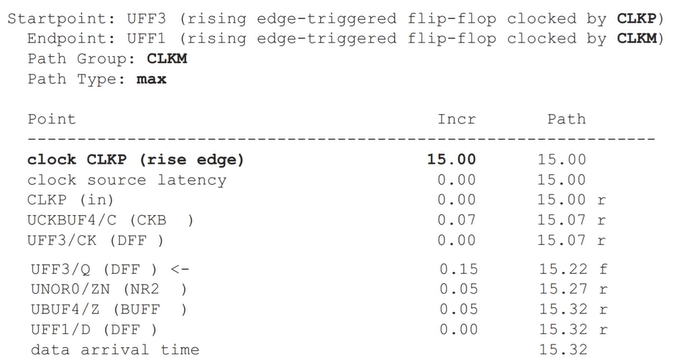

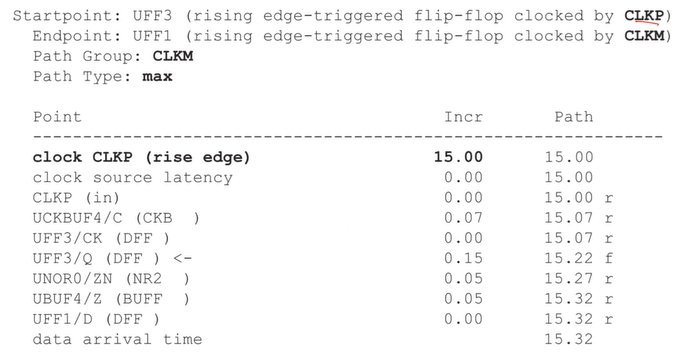

15时刻的时序检查,发射路径

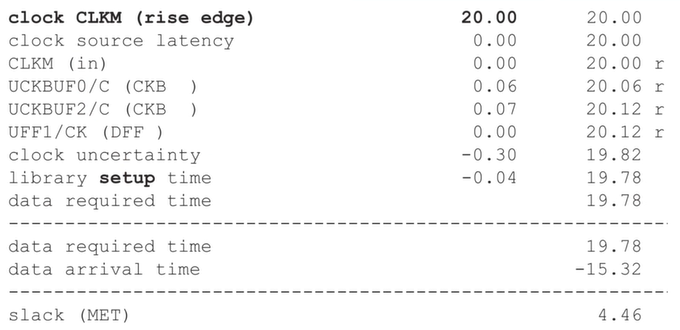

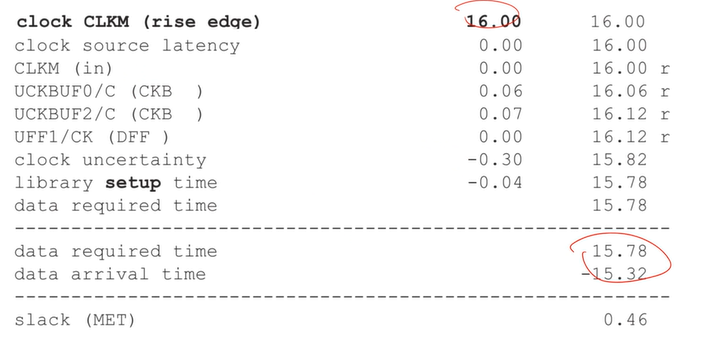

捕获路径

这对于慢时钟来说要求会比较高,裕度比较小

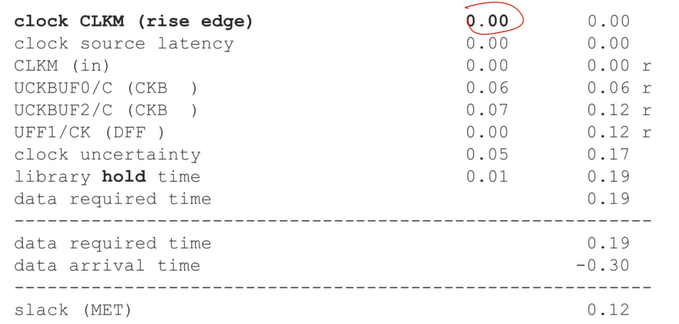

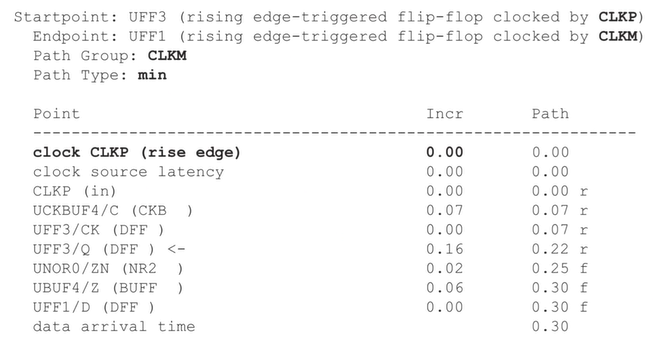

下面是0时刻边沿的hold检查,发射路径

捕获路径

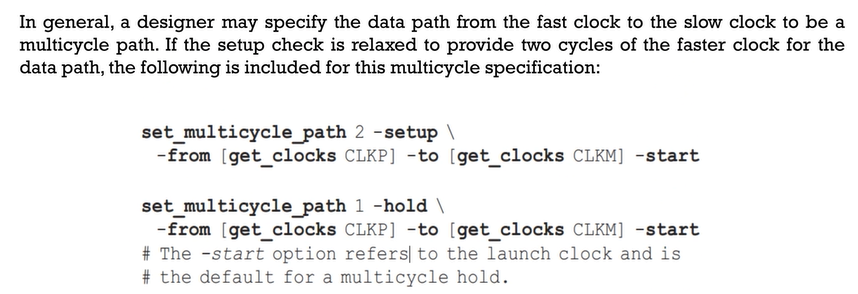

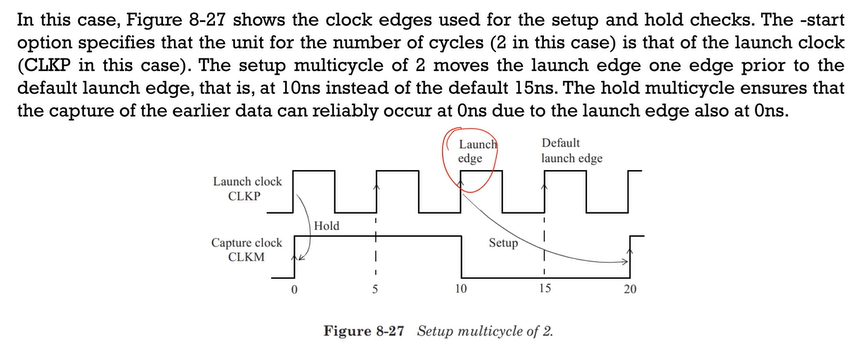

同样使用多周期路径约束放宽setup和hold检查

约束以后的时序检查

约束以后建立时间的发射路径

捕获路径

保持时间的发射路径

捕获路径

多时钟

整数倍关系

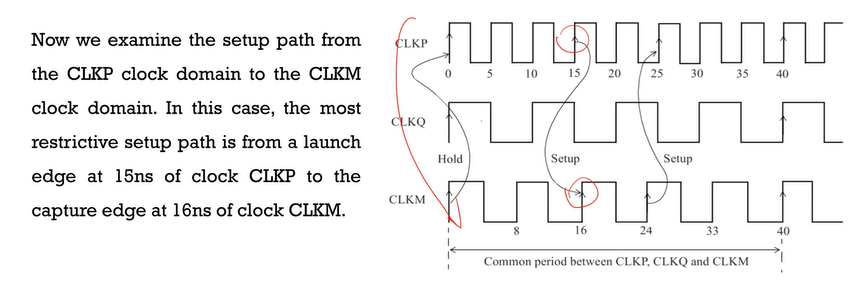

现在有三个时钟

对最快到最慢的路径检查,最严格的检查边沿就是15

捕获路径

保持时间

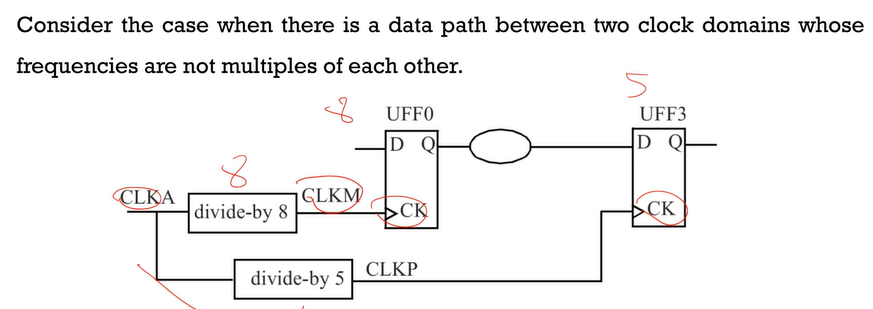

非整数倍

下面是一个例子,一个五分一个八分

这种情况下取最小公倍数进行处理

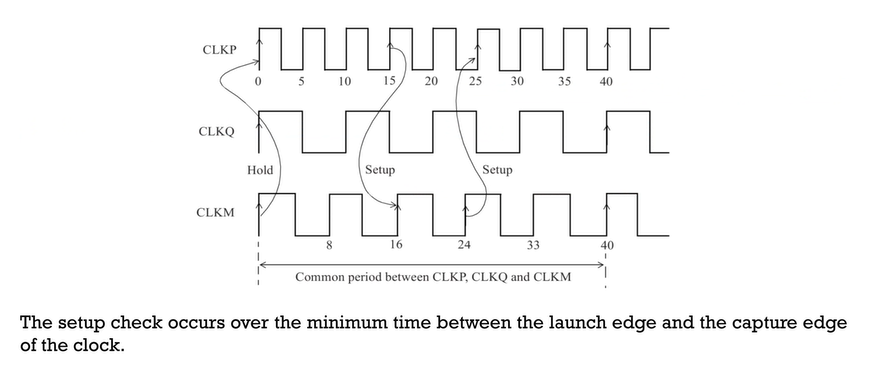

因此检查边沿如下

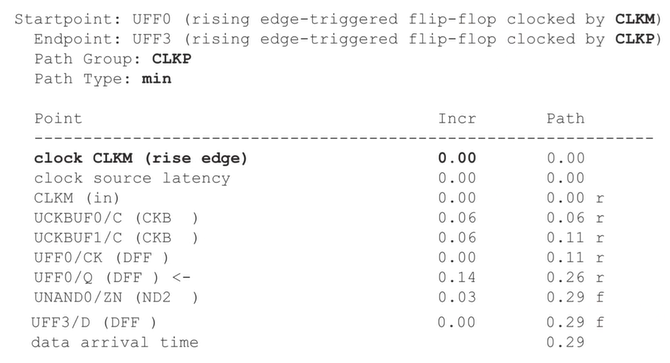

先考虑从慢到快时钟,最严格的建立时间边沿就是24

最严格的情况下都能够meet timing,那么其他地方都没有问题

保持时间最严格的检查边沿在0时刻

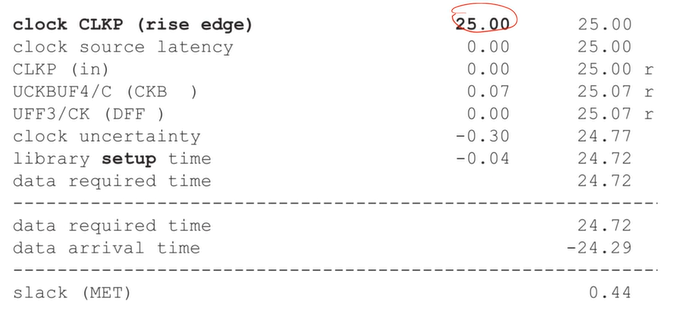

再考虑从快到慢

建立时间最严格的边沿在15时刻

hold同样也在0时刻进行检查

捕获路径

有相位差

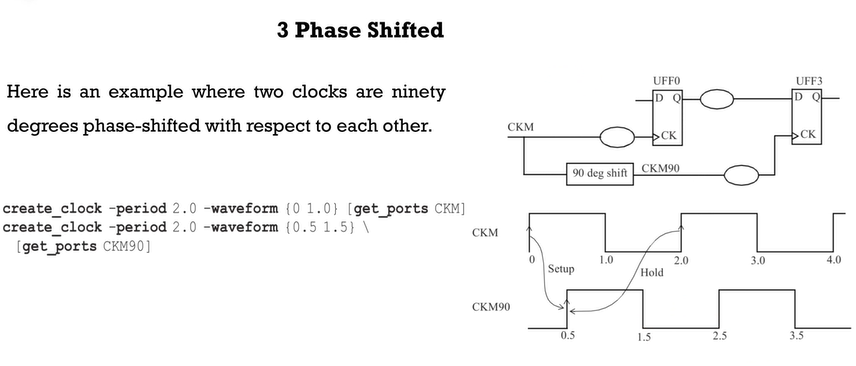

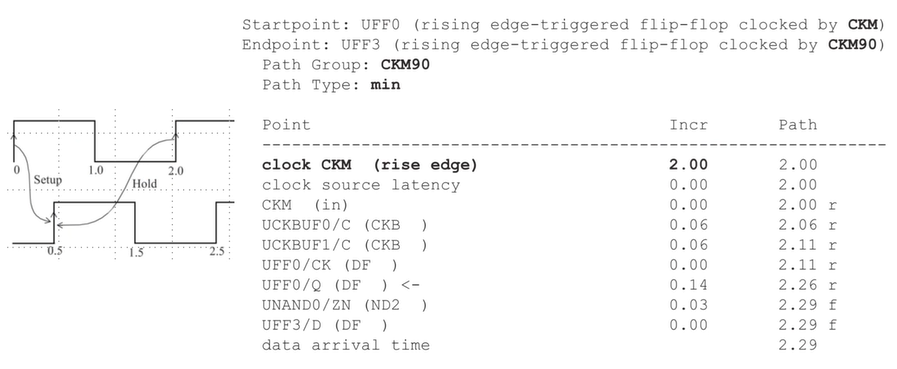

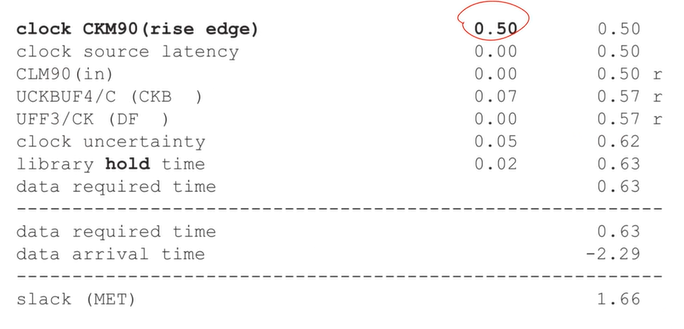

相位有移动的情况,下面的两个时钟有90°的相位差,约束如下

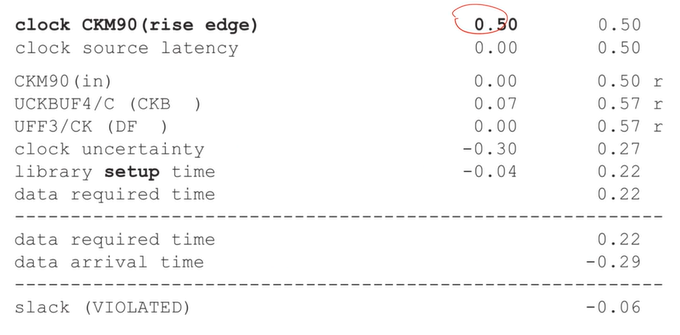

这里类似于半周期的约束,hold的裕度比较多而setup裕度比较少

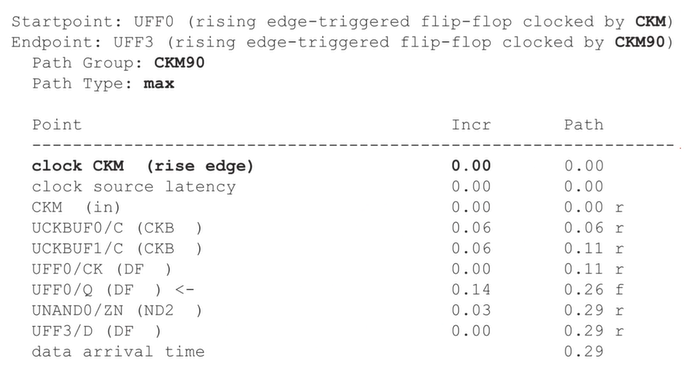

建立时间发射路径

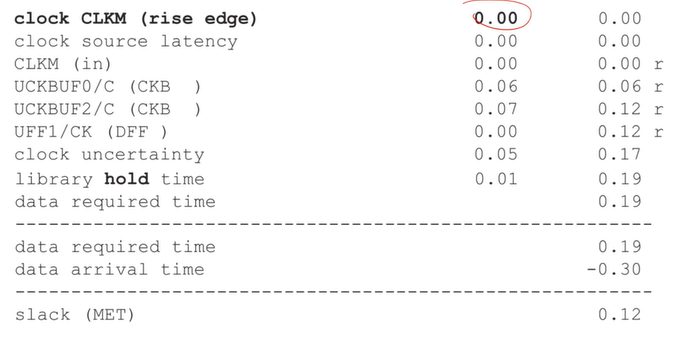

hold发射路径,注意这里开始时刻是2,而捕获时刻在0.5,所以说对保持时间裕度比较大

浙公网安备 33010602011771号

浙公网安备 33010602011771号