《数字集成电路静态时序分析基础》笔记⑧

欢迎关注个人公众号摸鱼范式

网络课程《数字集成电路静态时序分析基础》的笔记

多周期半周期伪路径

多周期路径

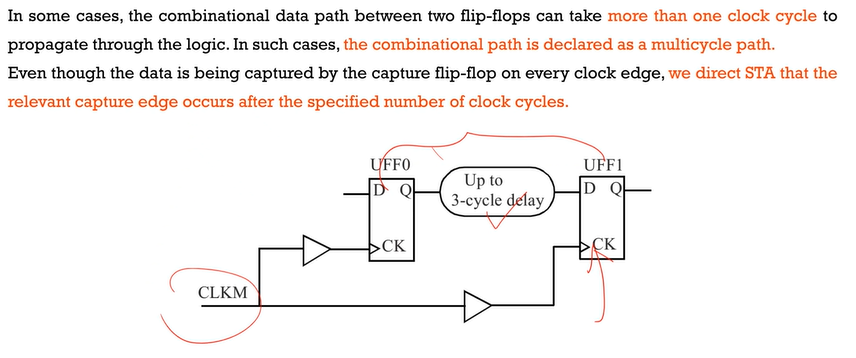

通常对于普通路径来说,路径延迟是T,但是某些情况下,中间延迟远远大于一个周期T。

建立时间检查

多周期时序约束

一个简单的例子,对于多周期路径,建立时间检查边沿会推到第三个周期

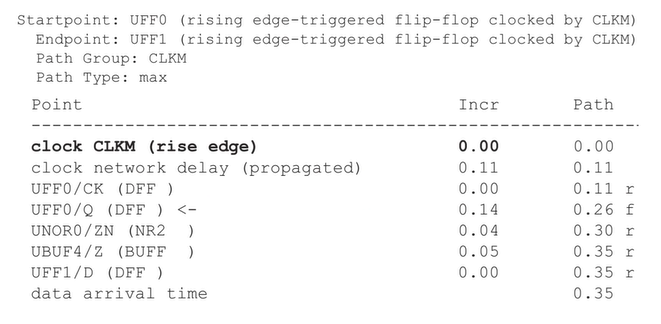

多周期时序路径,launch path和普通的没有区别

而captured path有些不一样,clock CLKM的incr达到了30,也就是三个周期。

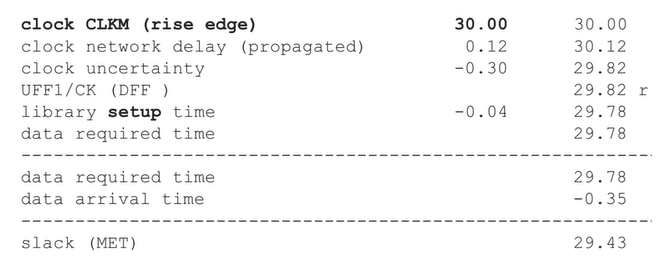

保持时间检查

对于hold来说,如果按照默认的边沿,所需要保持的时间就会非常长,过于严格,通过下面的约束可以将保持时间检查边沿向前移动两个边沿。

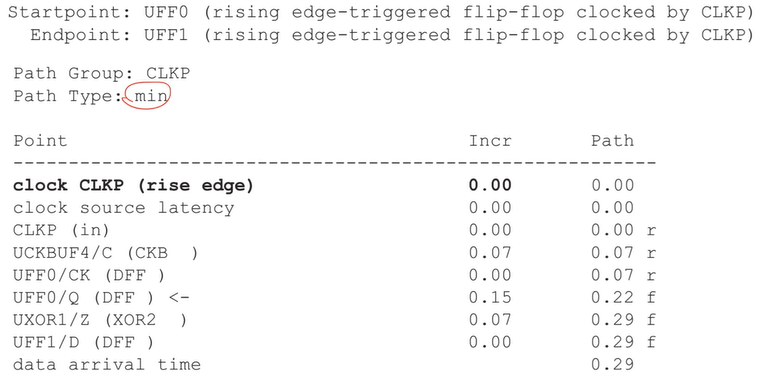

保持时间报告

默认的话,clock CLKP应该是20(建立时间检查边沿前一个),由于设置了前面的约束,变成0了。

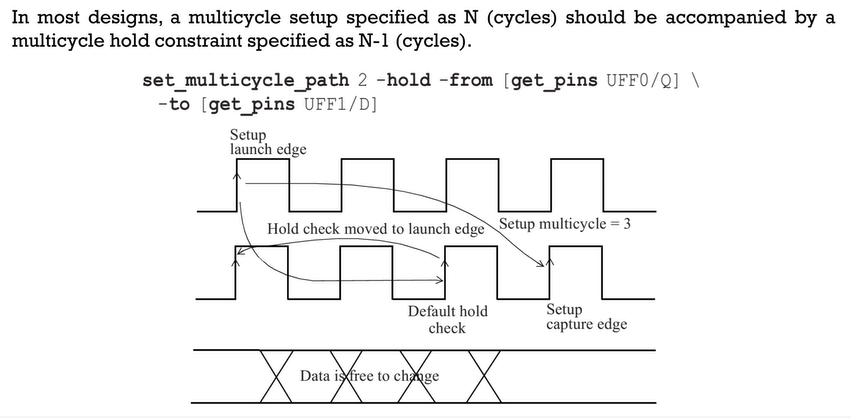

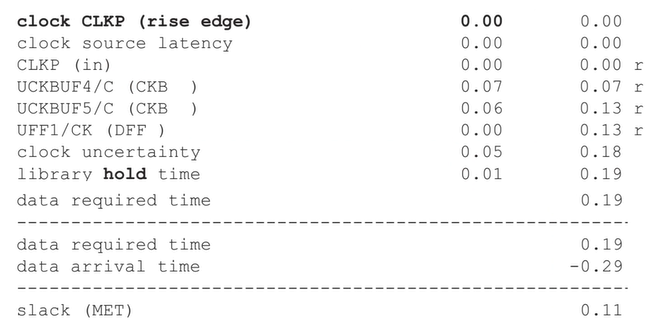

如果建立时间多周期约束了N,而保持时间N-1没有设定,那么会发生什么?

时序路径就会变化,launch path没有变化,主要是capture path变化了

clock CLKP变成了20,时序不满足。

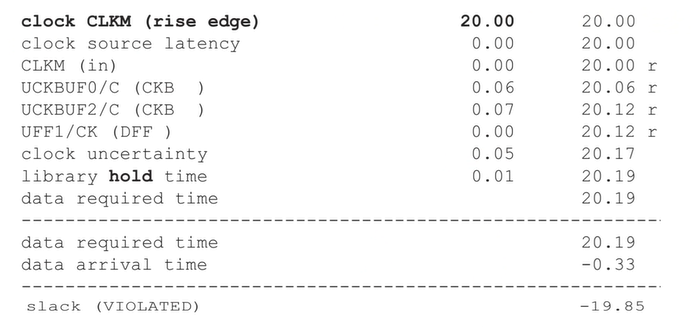

半周期路径

普通路径的触发时钟边沿是一致的,对于一个是正边沿,一个时负边沿来说,就要使用到半周期路径约束

如果两个边沿不一样,中间组合逻辑的裕度实际上就会减少到半个周期。

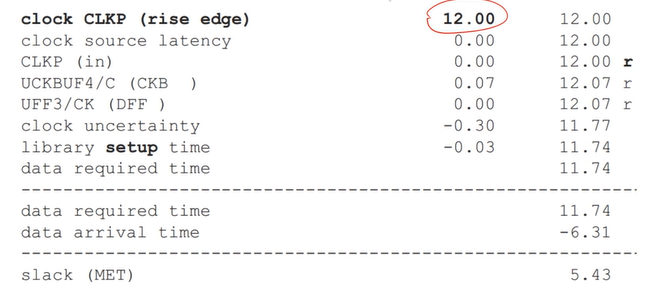

建立时间检查

launch path的clock incr会达到6,而capture path的clock incr依然是整个时钟周期12,于是中间裕度就只有半个周期了,6ns

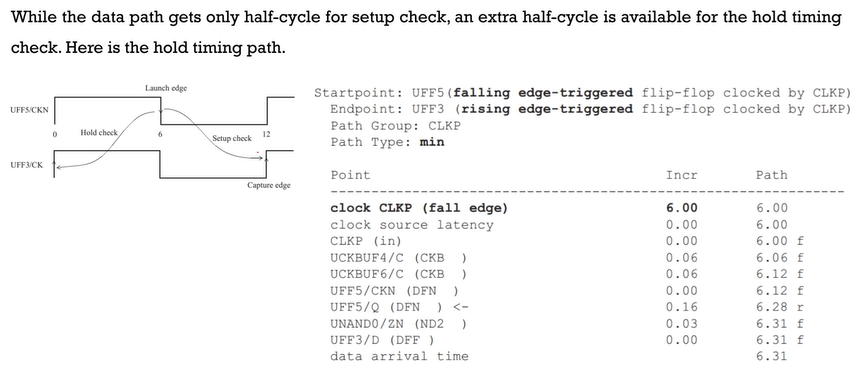

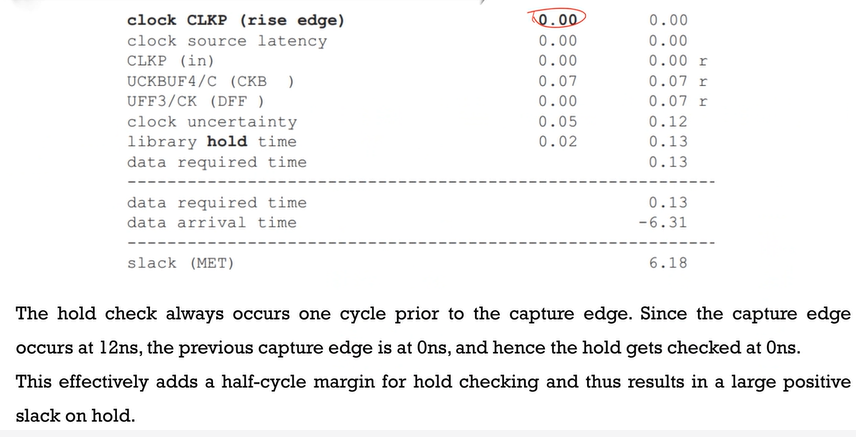

保持时间检查

会看到launch path和capture path的起点不一样

半周期路径中保持时间很轻松就能满足。

伪路径

有些路径并不是真实的,或者说不可能发生的,那么就需要伪路径告诉工具不需要进行检查。

伪路径通常出现在异步时钟,跨时钟域中

伪路径可以让STA工具速度变快,将时间花在真实的路径中。但是如果过多的使用伪路径反而会减慢STA的速度。

伪路径约束的例子

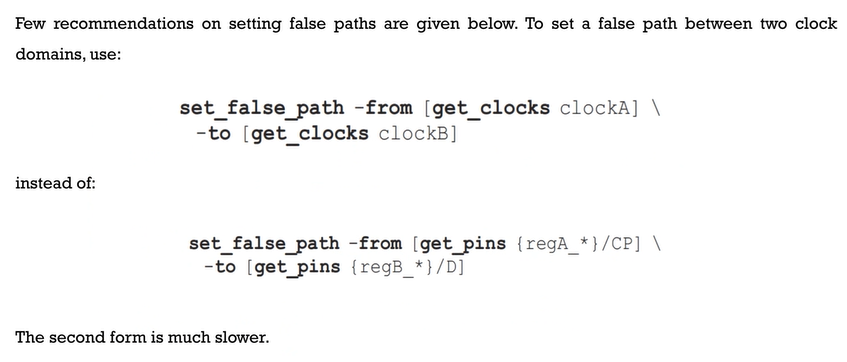

伪路径定义应该尽可能定义得精确

第二个约束的数量过多,第一个直接指定时钟会更加快一些。

尽可能少使用through,这也会增加计算量

必须确认是真的伪路径,例如多周期路径就不能被设定为伪路径。该分析的路径就应该施加准确的时序约束,只对真正的伪路径设定伪路径

浙公网安备 33010602011771号

浙公网安备 33010602011771号