《数字集成电路静态时序分析基础》笔记⑥

欢迎关注个人公众号摸鱼范式

网络课程《数字集成电路静态时序分析基础》的笔记

STA环境

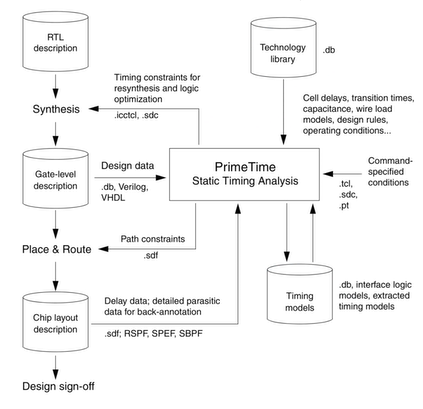

PT

本节主要讲解如何编写SDC文件

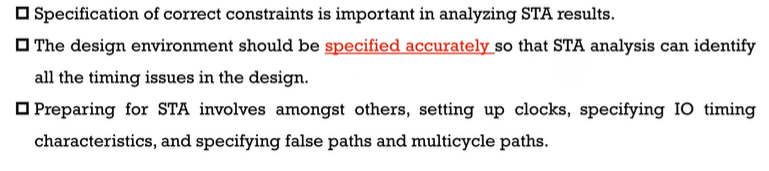

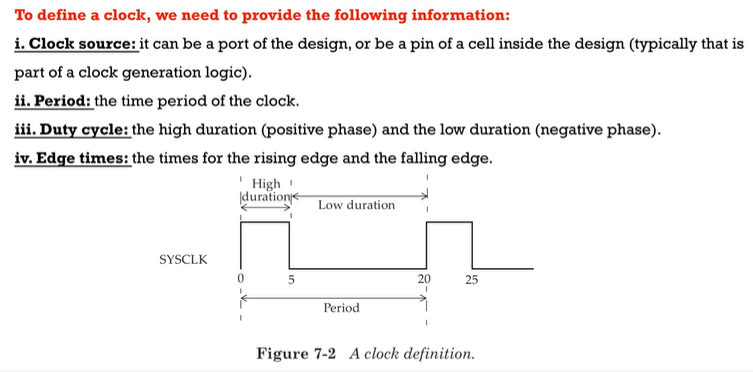

什么是STA环境

STA环境就是指导设计的环境,主要包括时钟、IO、特殊路径、多周期路径

STA针对的是同步电路,无法分析异步电路。

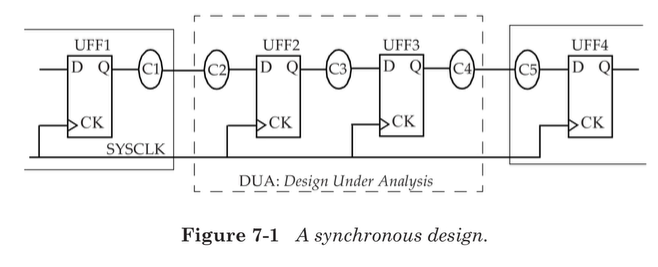

时钟约束

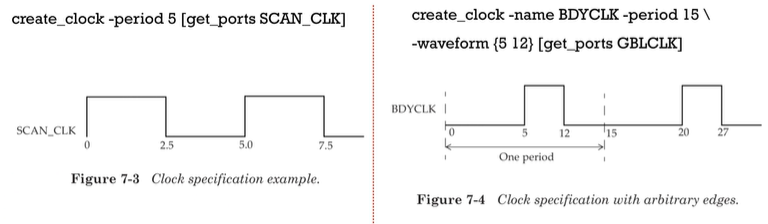

时钟约束包括:时钟源、周期、占空比、边沿翻转时间

create_clock -name SYSCLK -period 20 -waveform {0 5} [get_ports SCLK]

上面这条命令就是对时钟的约束,下面是其他例子。

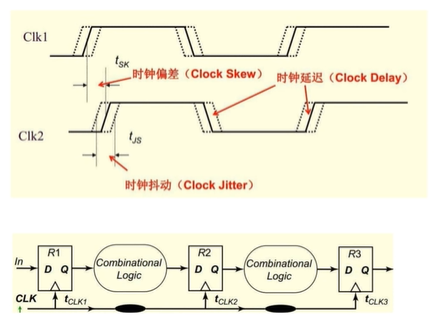

时钟的其他属性

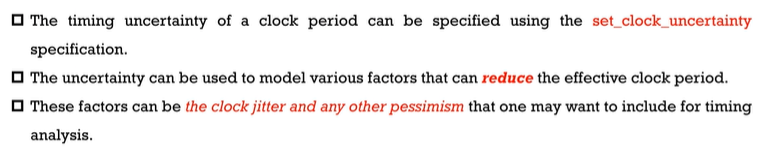

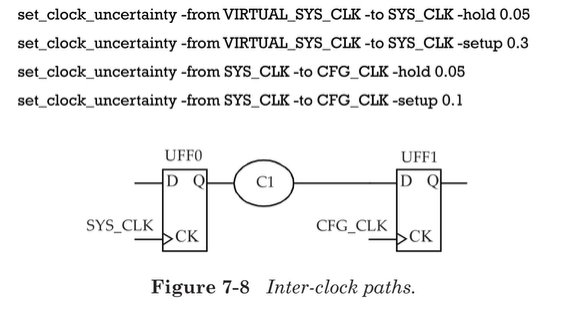

通过set_clock_uncertainty设定悲观条件,收紧约束,例如下图中设定建立时间和保持时间

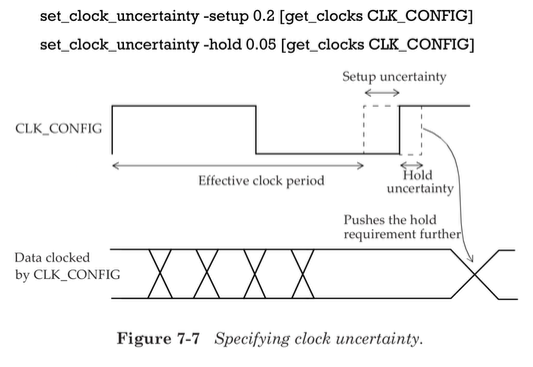

指定不同时钟之间的不确定度

时钟之间的不确定度的意义

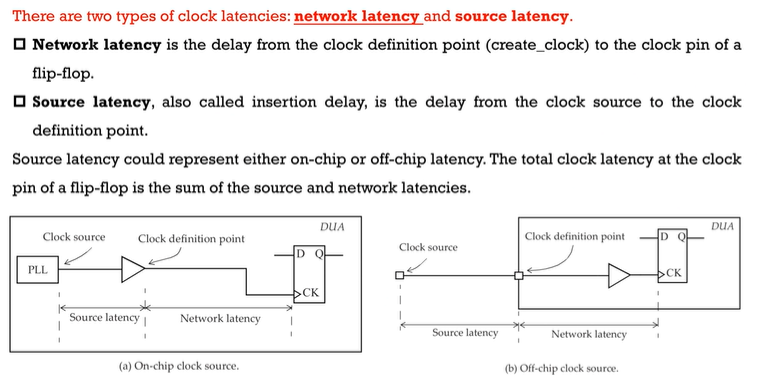

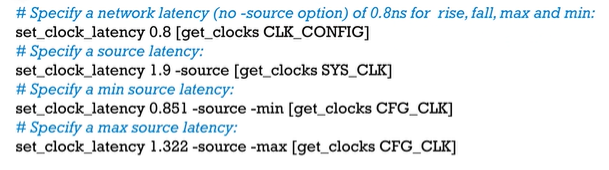

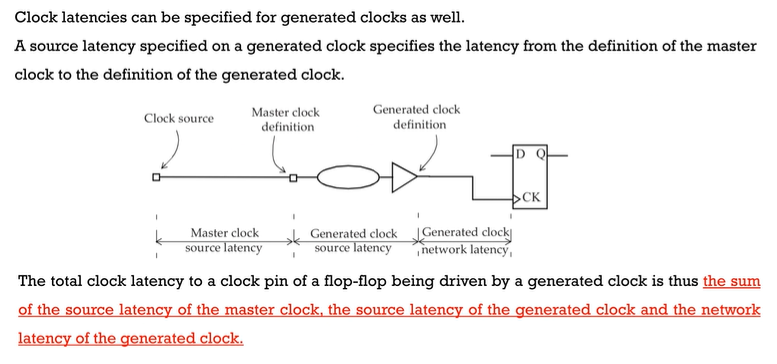

时钟延迟,networks延迟和source延迟

延迟指定方法,默认是networks延迟。

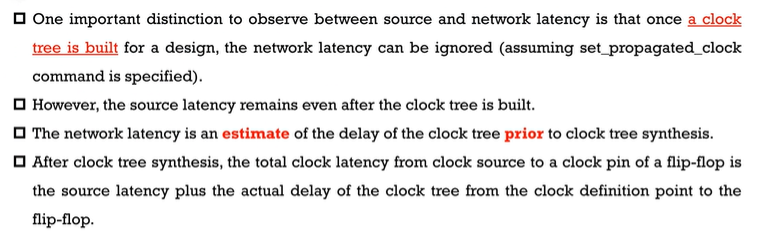

一些注意的点:

如果时钟树已经建立好了,就不需要关心network延迟,使用图中的指令可以获得精确的时钟。在时钟树建立以前,才需要对时钟进行估算。

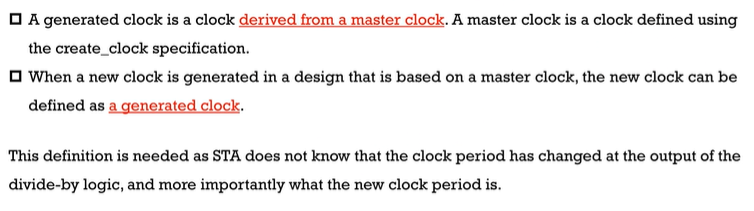

生成时钟

master clock通过分频等手段产生的时钟,需要定义为generated clock

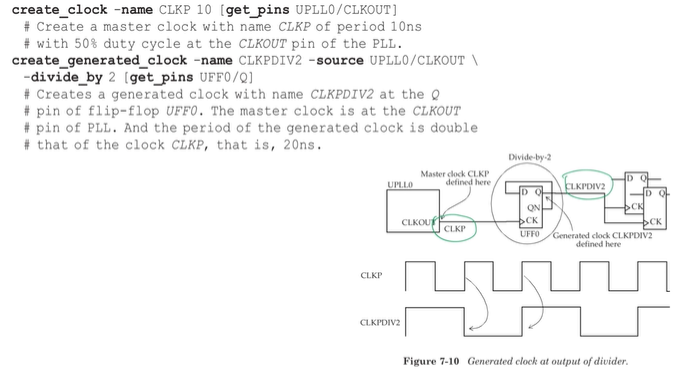

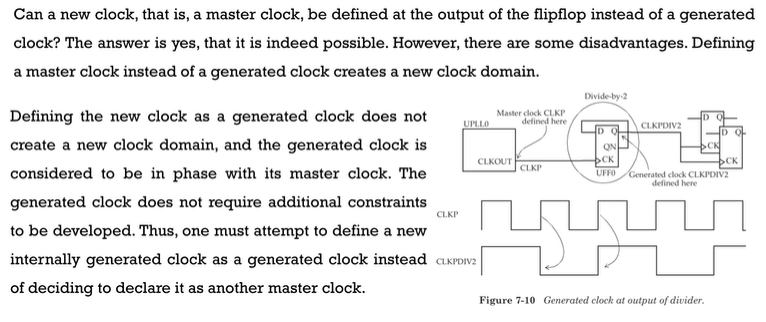

新时钟也可以定义为master clock,但是会存在一些问题。如果直接定义为master clock,会使两者失去联系,系统会认为两者是异步的,相关性丢失,导致出现问题。

此外,master clock和generated clock之间是有联系的,参数是有继承性的。

下图为一个例子,延迟会累加

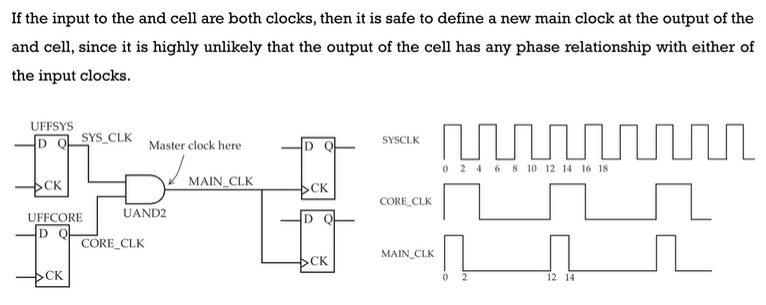

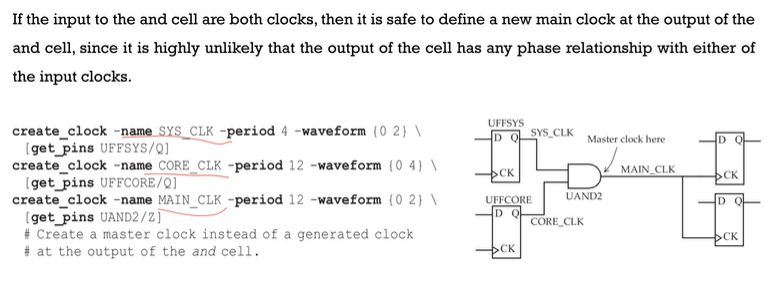

并不是所有情况下都需要定义生成时钟,下面的时钟通过逻辑门以后新时钟和原来的关系并不大,最好直接定义行时钟。

下面是例子

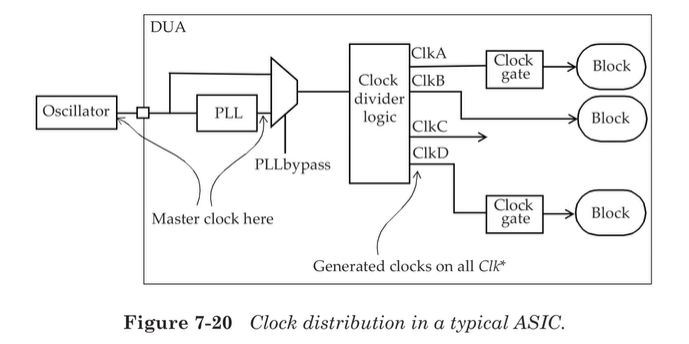

ASIC中的时钟

input path和output path

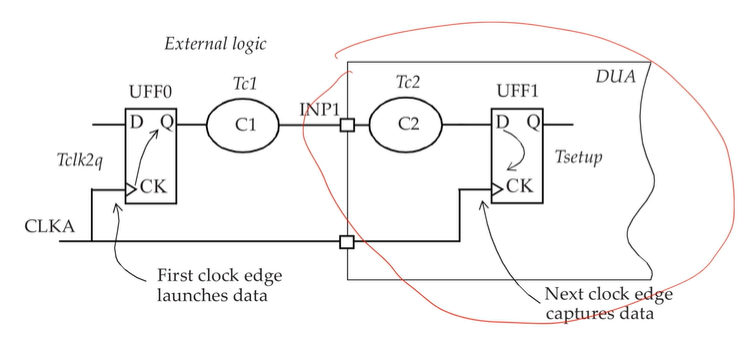

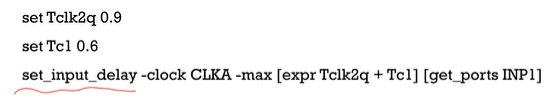

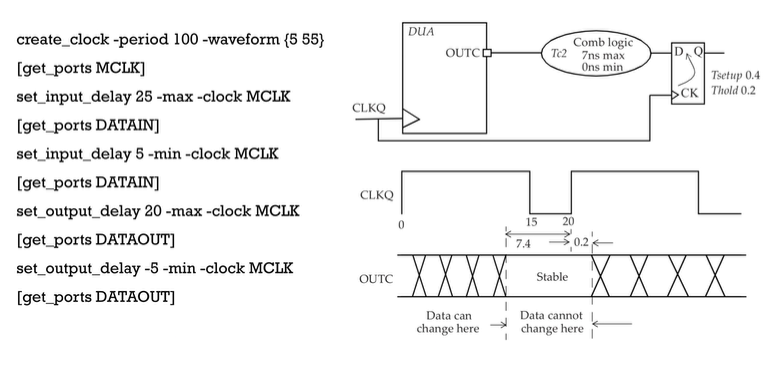

约束input path

由于输入路径只有终点有时钟,所以需要指定输入延迟

针对建立时间和保持时间分别设立最大最小延迟

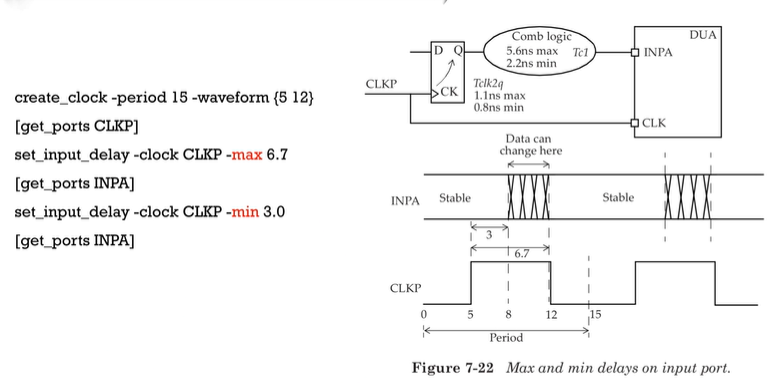

output path

和input path类似

针对建立时间和保持时间设定最大值最小值

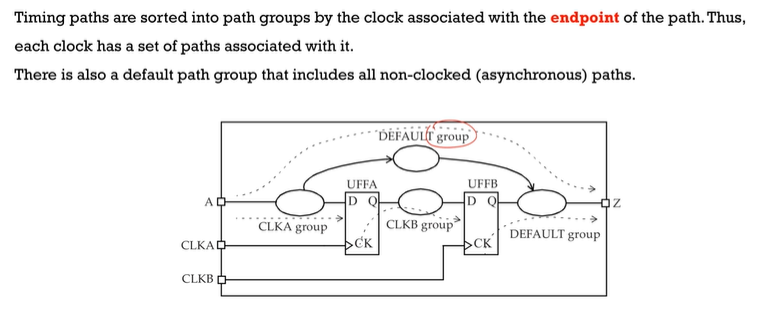

路径组

路径通过终点进行分类。

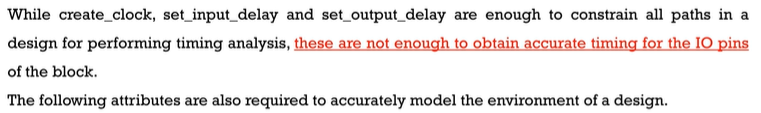

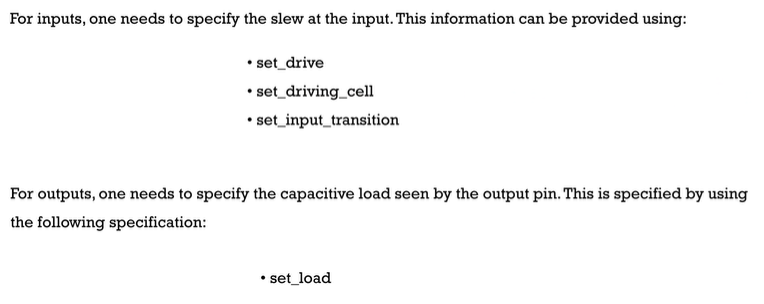

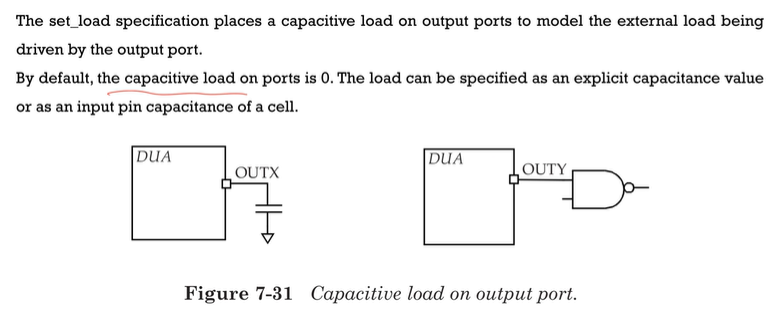

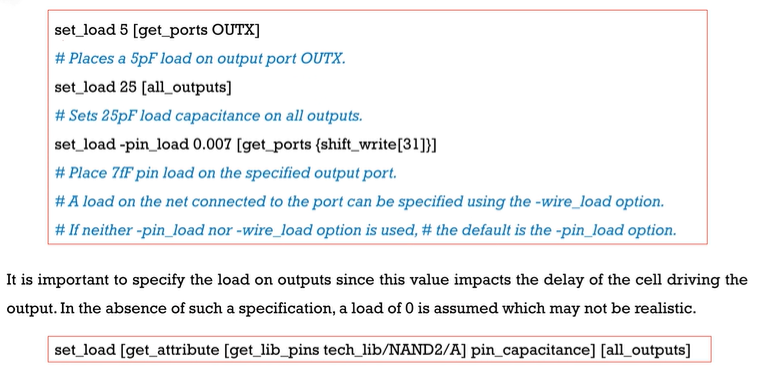

对IO pins来说,时钟和输入输出的延迟约束是不够的,还需要约束其他参数

属性设定方法

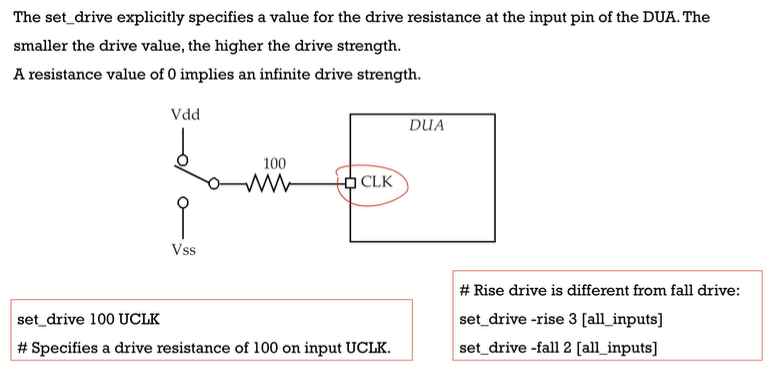

驱动值越小,驱动能力越大,0代表无限大。

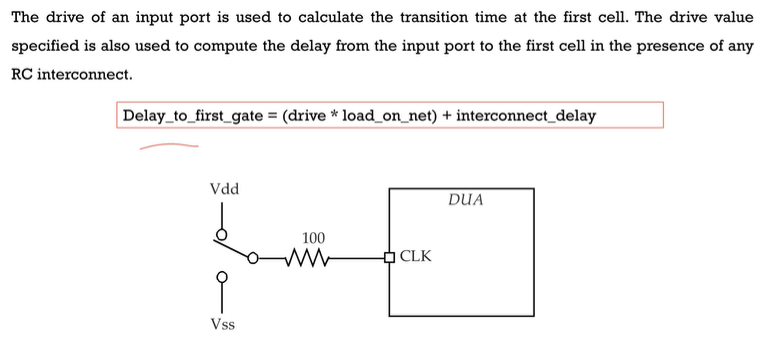

设定驱动能力以后,就能够计算第一个门的延迟。

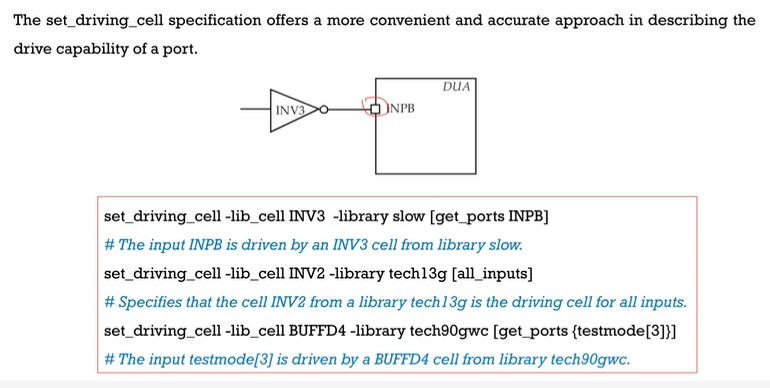

也可以从库里参考驱动能力,取库里cell的属性拿来用。

输入路径的第一个cell一定要通过约束设定delay,而默认是理想值,即0

输出路径也是类似的

理想情况下也是0,实际需要自行设定相关值。

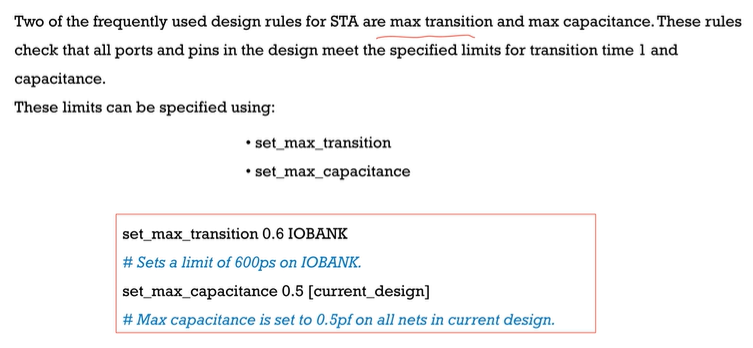

design rule checks

缩写就是DRC

主要的两个参数就是max_transition和max_capactiance

其他的属性,但是并不是主要的,和库有关系

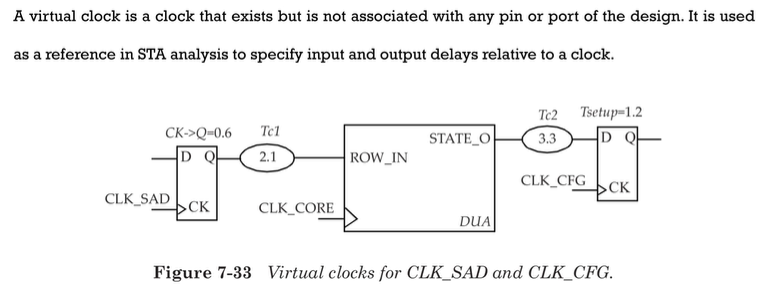

虚拟时钟

虚拟时钟和所有pin和port都没关系,它用来作为STA的参考,指定输入和输出延迟和一个时钟的关系

定义方法,这里不需要指定那个pin或者port是时钟

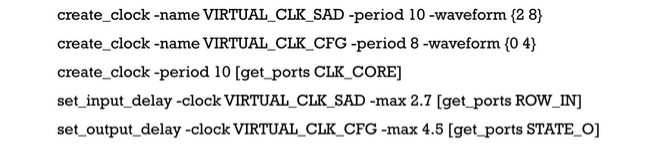

让STA更加精确

有四点

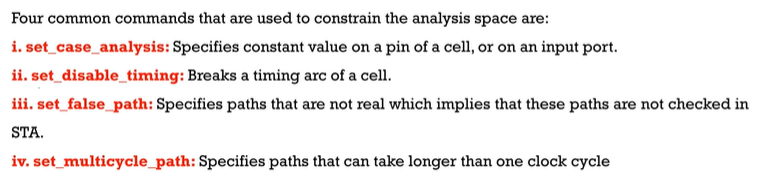

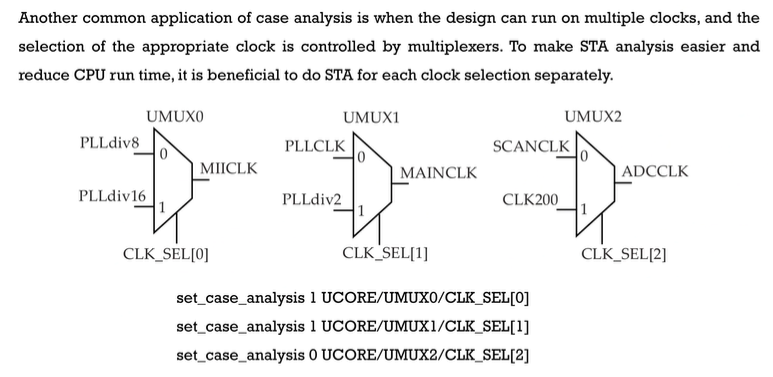

case_analysis

芯片在不同情况下的约束,例如在DFT下,可以关闭DFT部分的检查

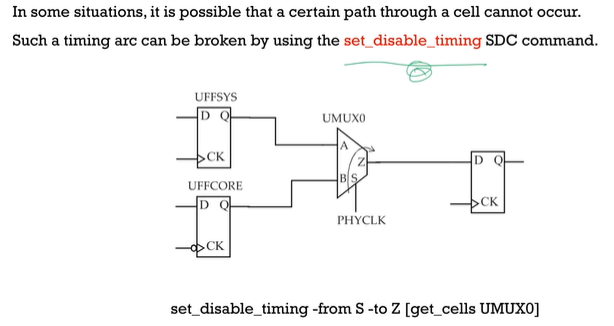

disable_timing

告诉工具这不是一条timing path

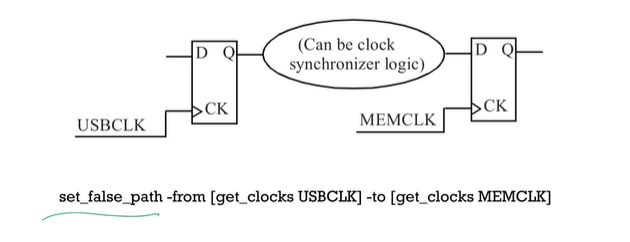

false_path

伪路径,告诉工具不需要检查

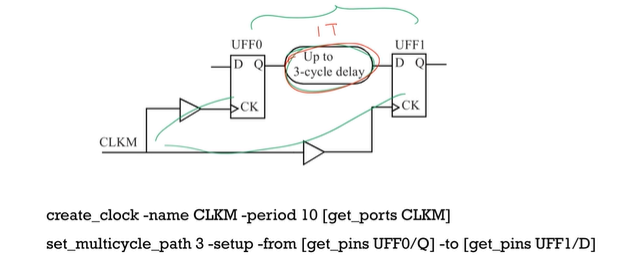

multicycle_path

多周期路径

参考书目

浙公网安备 33010602011771号

浙公网安备 33010602011771号