FPGA —— Quartus II 15.0 使用 ModelSim SE-64 2019.2 软件进行仿真

Quartus II 15.0 使用 ModelSim SE-64 2019.2 软件进行仿真

ModelSim 仿真 Verilog HDL 时需要编写一个 TestBench 仿真文件,通过仿真文件提供激励信号。可以简单的理解成信号发生器,给我们的代码提供模拟时钟信号。因此编写 TestBench 仿真文件是仿真过程中的一个重要步骤。

Quartus II 15.0自身是不提供仿真功能的,但是可以用 Quartus II 15.0 创建 TestBench 仿真文件模板,而我们稍微修改一下这个生成的模板文件就能进行仿真了,非常方便。

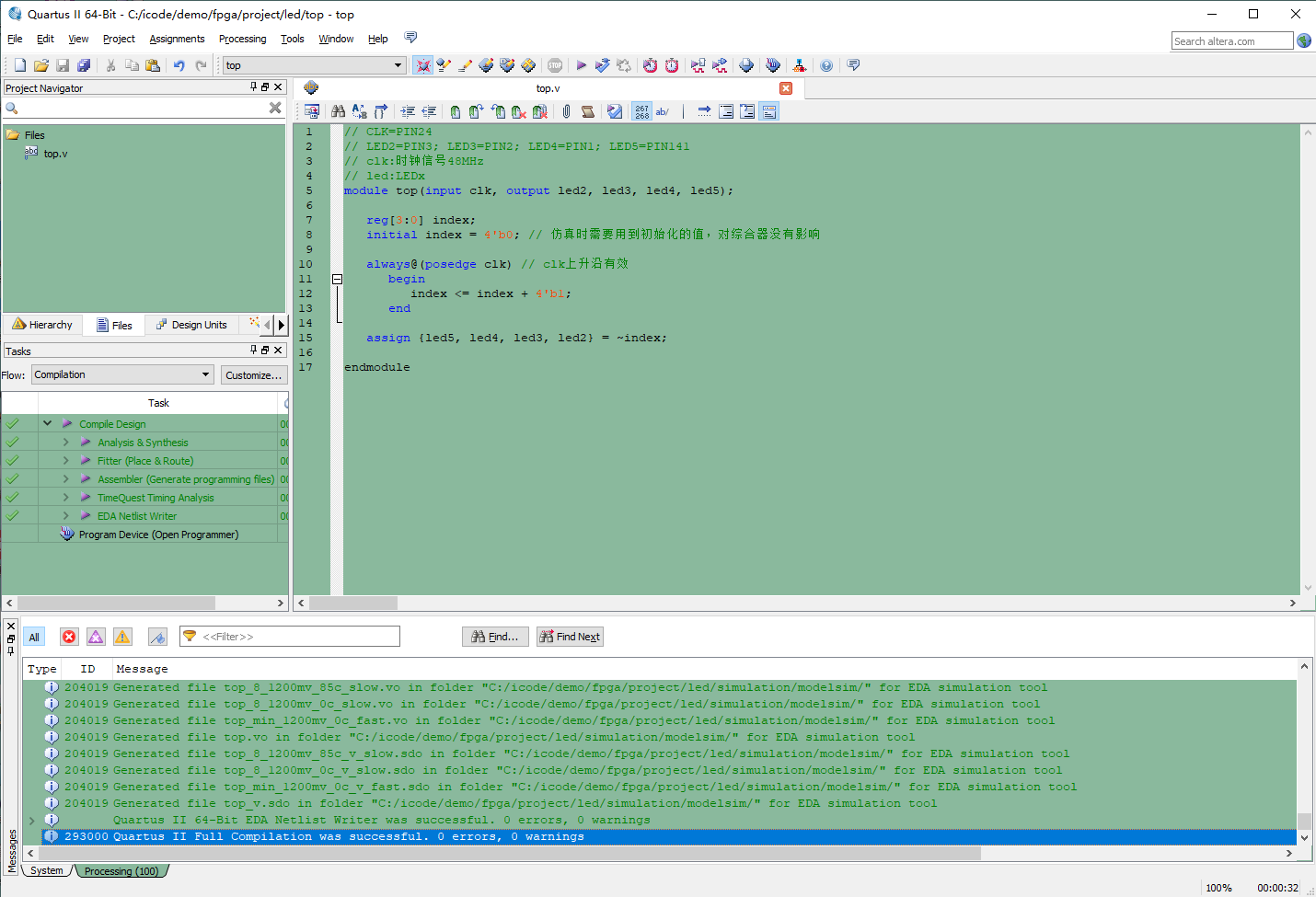

准备一个可以编译正常的工程(如果编译有问题可以参考上一篇博客)

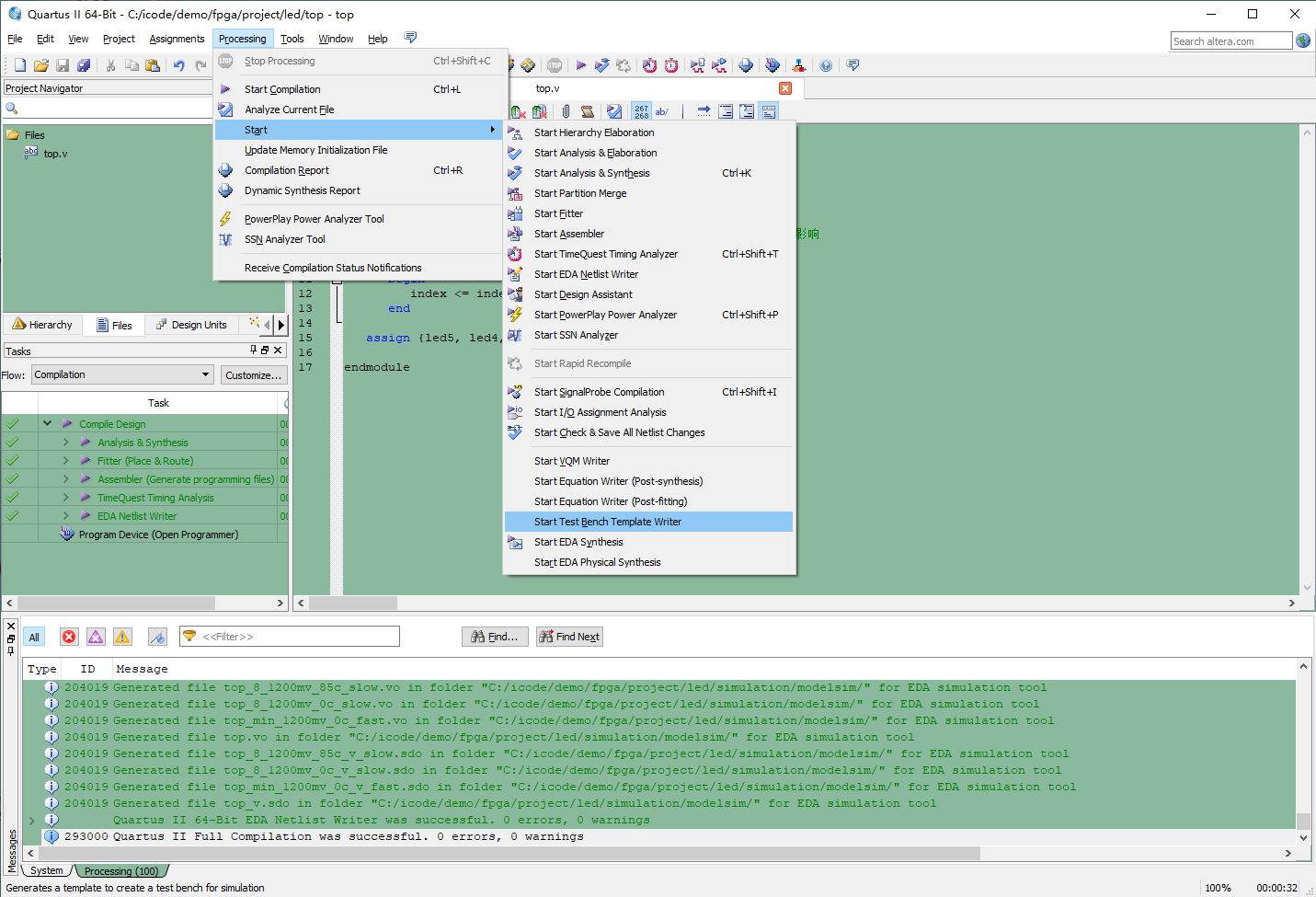

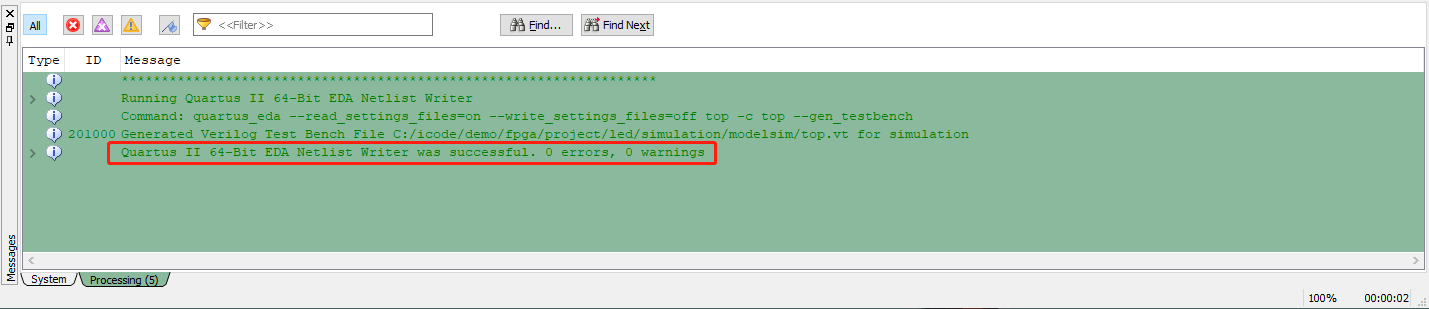

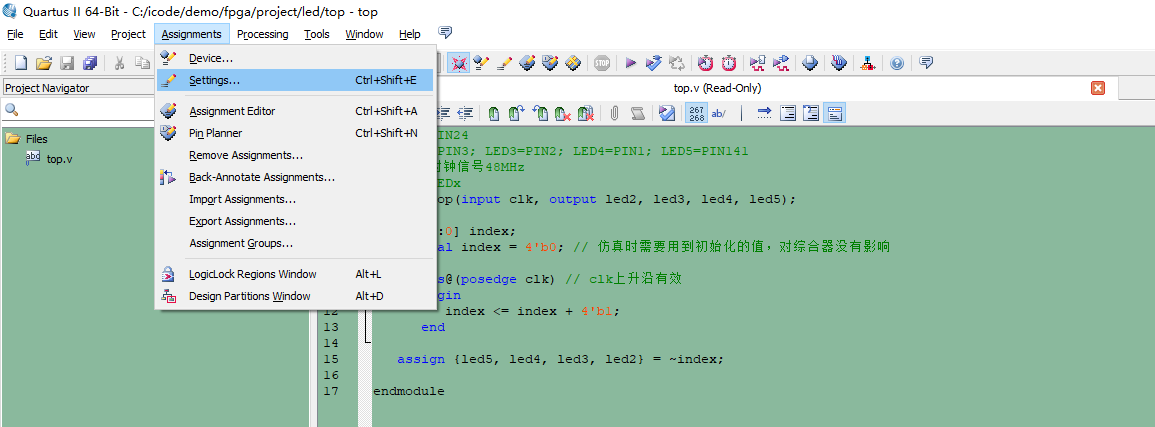

使用 Quartus II 创建 TestBench 模板文件,如下如图:

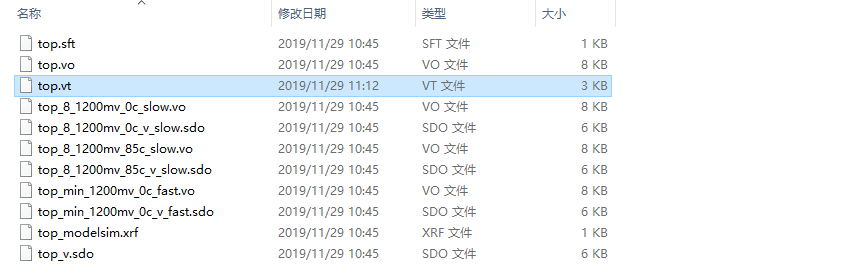

创建的文件后缀名是 .vt ,自动保存在工程目录\simulation\modelsim 中,我这里是 top.vt 文件

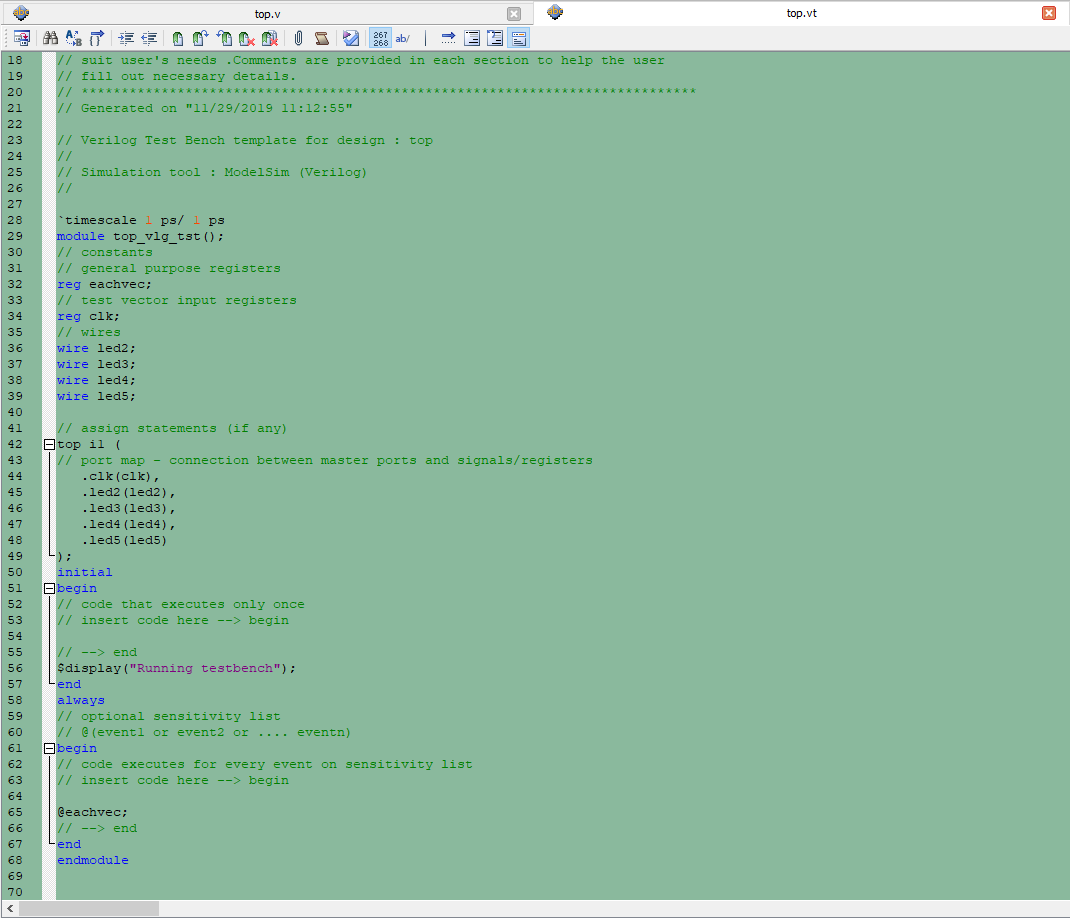

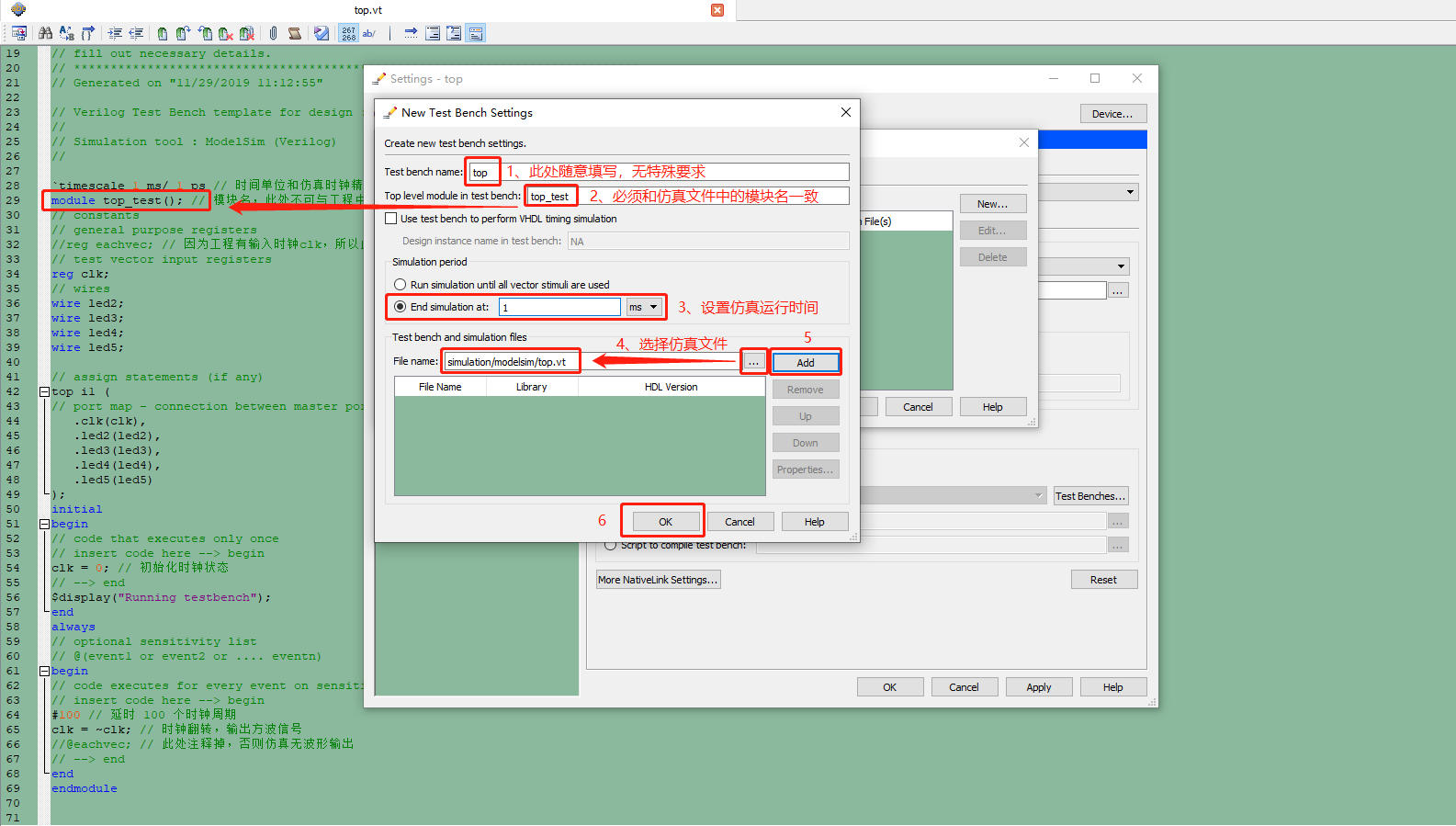

打开 top.vt 文件,文件内容如下:

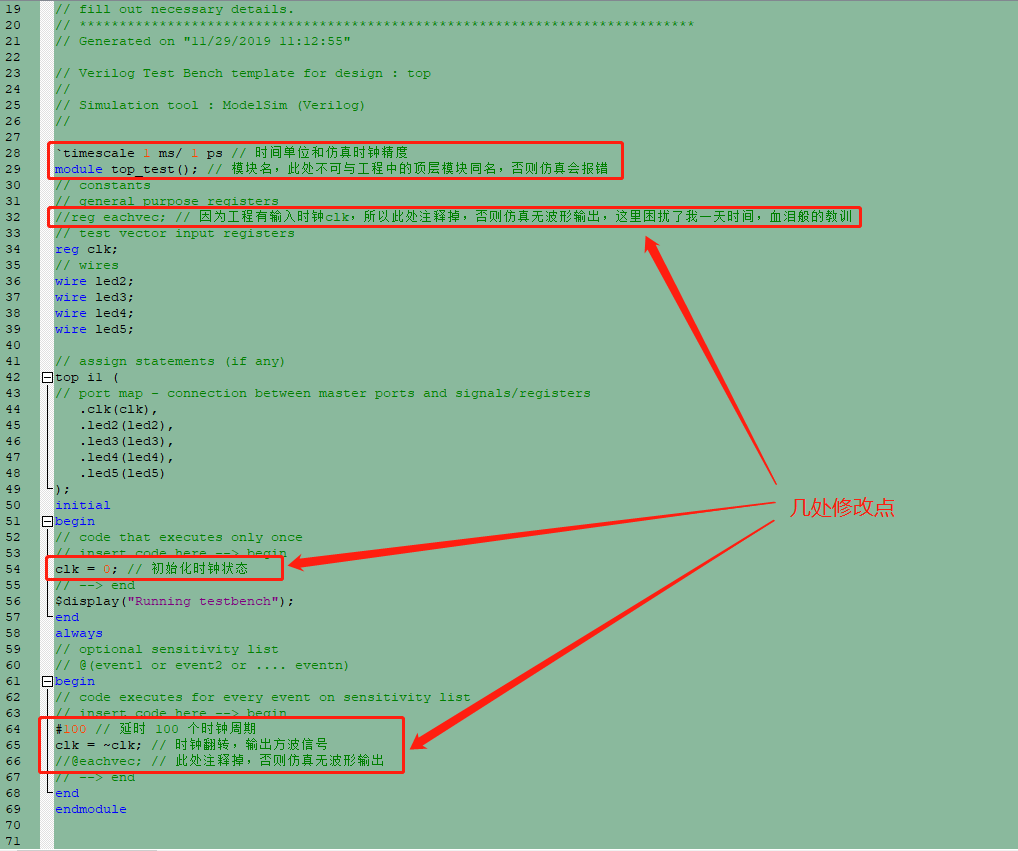

修改 top.vt 文件

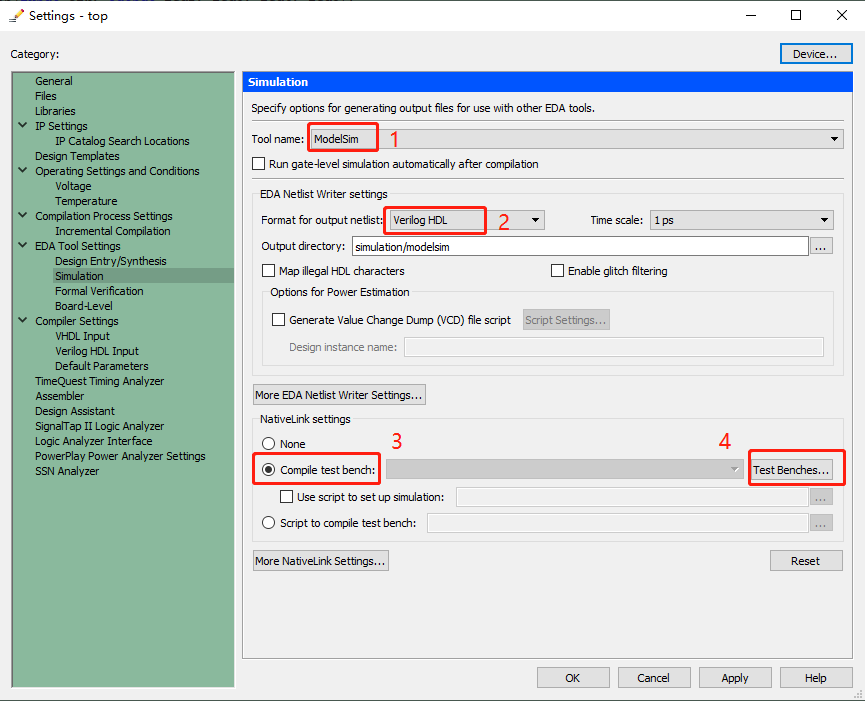

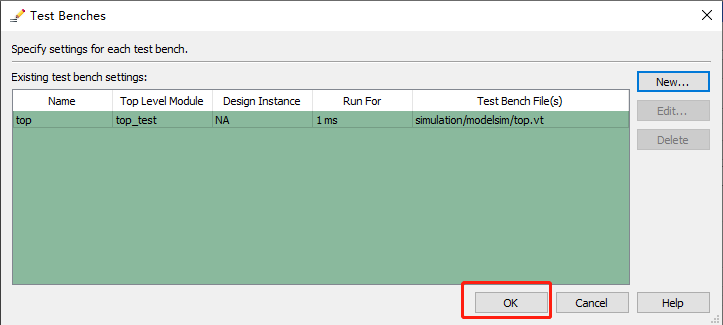

TestBench 仿真文件修改完成,接下来使用仿真文件:

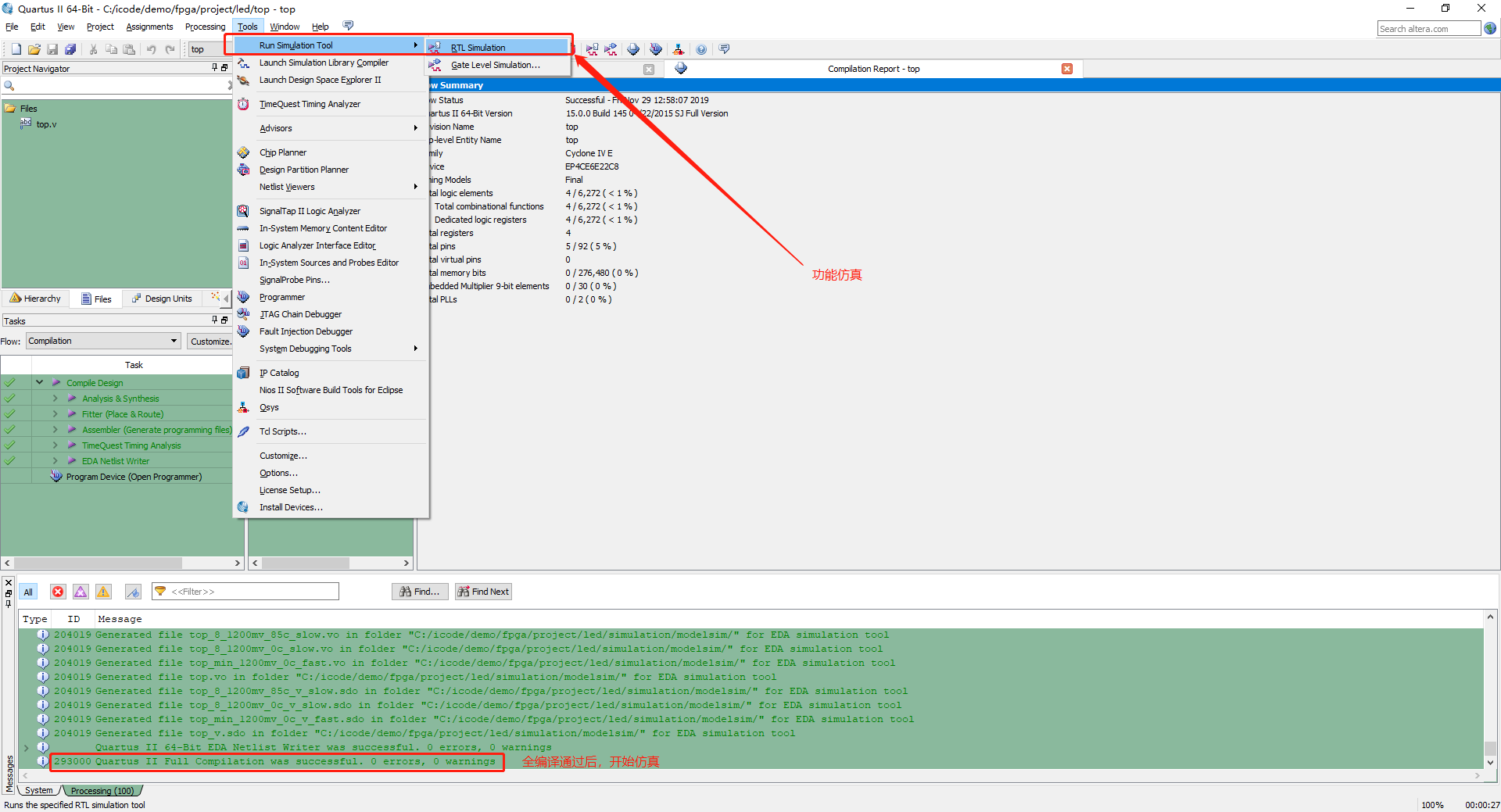

下面一路 OK 结束就可以了,然后再全编译一次,切记一定是全编译,编译完成后启动仿真软件,如下图:

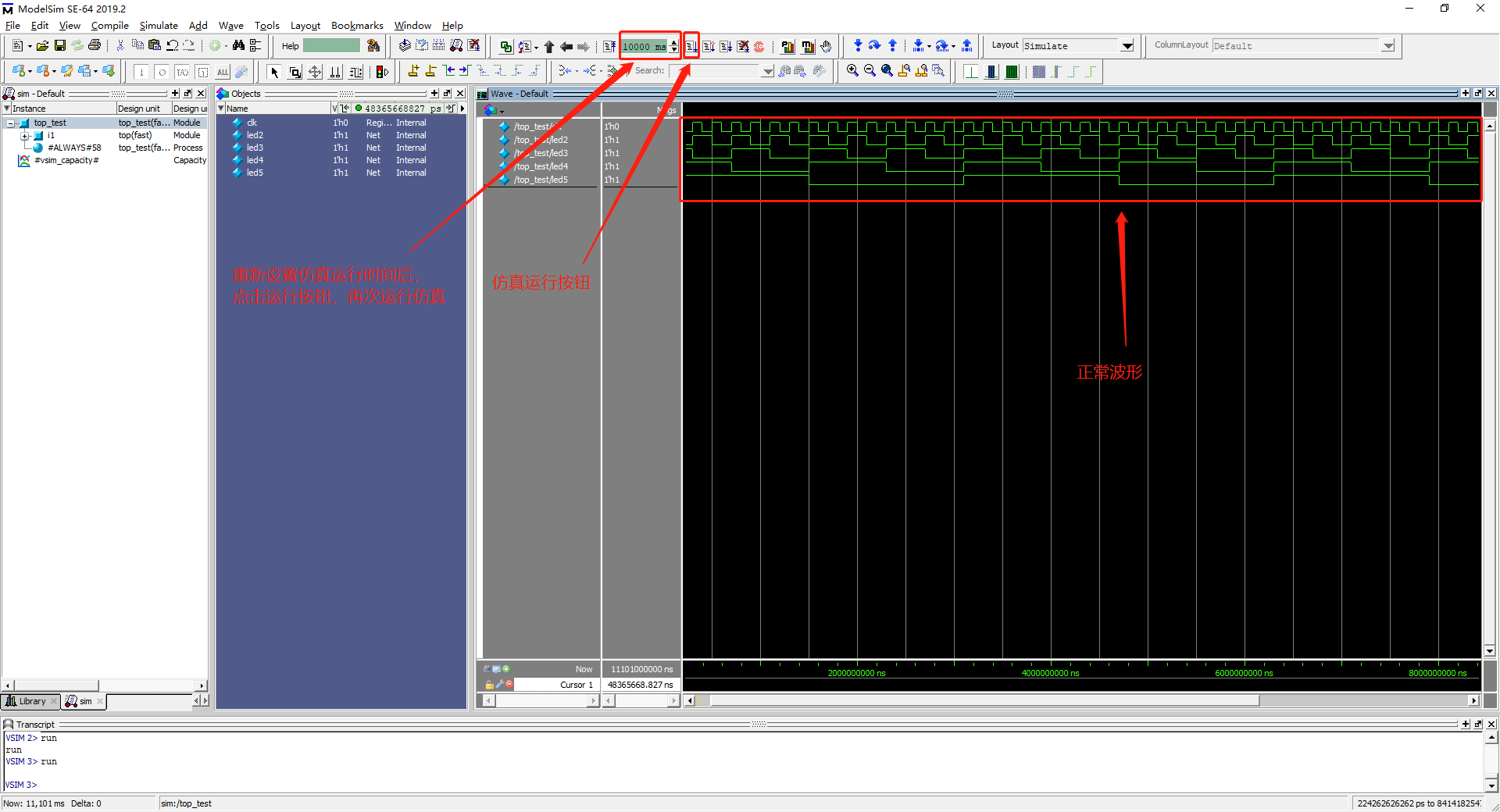

启动仿真运行后 Quartus II 会自动打开 ModelSim 软件,ModelSim 软件打开后会自动编译仿真文件,然后加载仿真文件中的接口,并且自动运行一次仿真。

总之在点击 RTL Simulation 后就什么都不要做了,等着看波形就好了。

如果波形是红色的直线就表示参数未初始化,工程模块内部参数初始化可以在工程代码中做掉,工程输入输出参数则在仿真文件里初始化。

如果没有任何波形出现,那就重新检查一下仿真文件以及仿真文件使用过程配置是否正确。

我刚才在 New TestBench Setings 窗口将 End simulation at 设置为 1ms,而仿真文件中的时间单位也为1ms,所以第一次仿真运行时由于时间长度不够,导致波形都是一条直线。后面在 ModelSim 中修改仿真运行时间为 10000ms,再次运行,波形就都显示出来了。

仿真结果如下:

至此 Quartus II 15.0 与 ModelSim SE-64 软件联合仿真运行完毕

一个小小的联合仿真功能花了我两天时间,吐血中。。。

总结:在执着中痛苦,在痛苦中觉悟,觉悟之后如履平地,觉悟之前如临深渊