FPGA —— LED控制

第一次接触新东西的时候,难免会磕磕碰碰,不过遇到问题不要着急,慢慢来。原因总归是我们自己引起的,一步步找到问题的根源,然后彻底解决它,避免下次再犯。

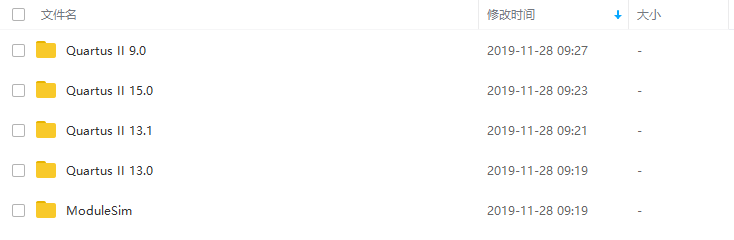

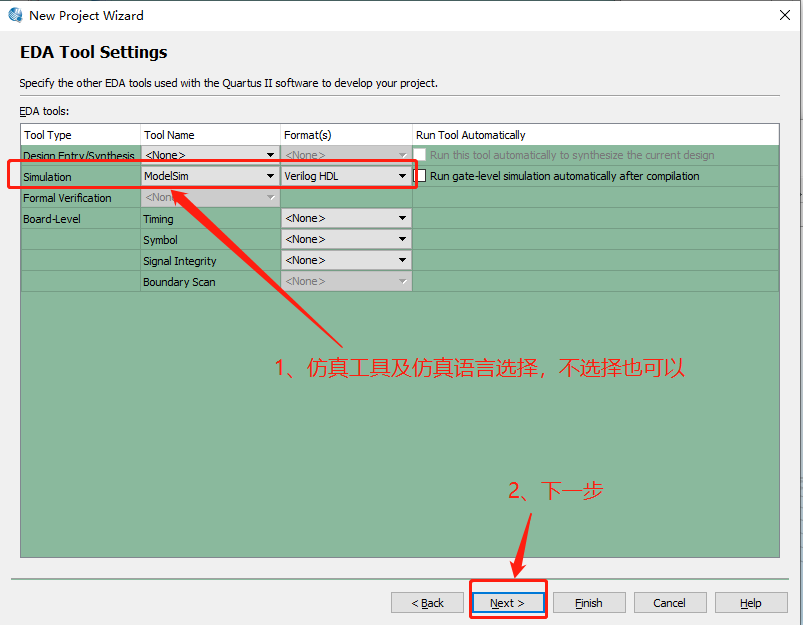

在开始之前先分享一下工具:(Quartus II 9.0、Quartus II 13.0、Quartus II 13.1、Quartus II 15.0、相应版本的器件库、Modulesim)

链接:https://pan.baidu.com/s/1RfwdpcfD5gmHJvndAgxh0A

提取码:0q8x

接下来进入正题

目标:创建 Quartus II 第一个工程 —— LED控制

开发环境:Quartus II 15.0.0.145 64Bit

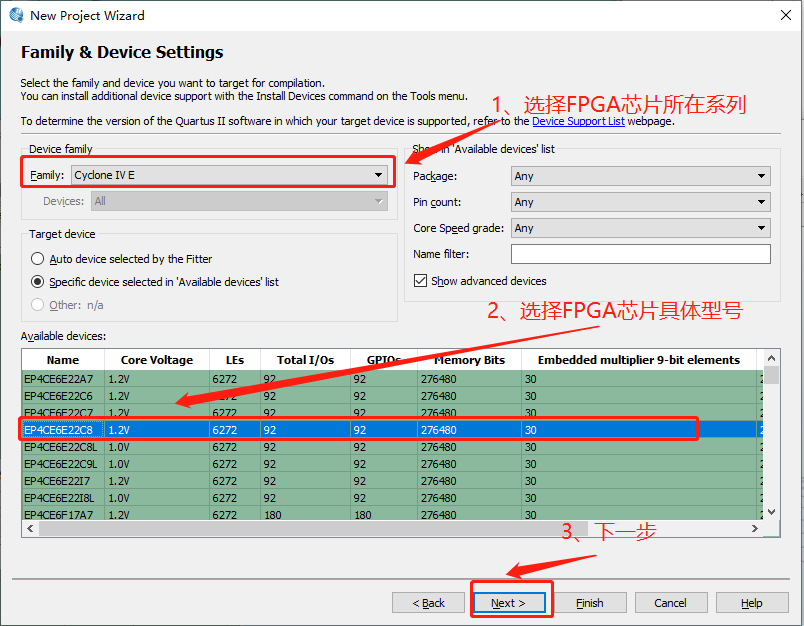

FPGA芯片:EP4CE6E22C8N

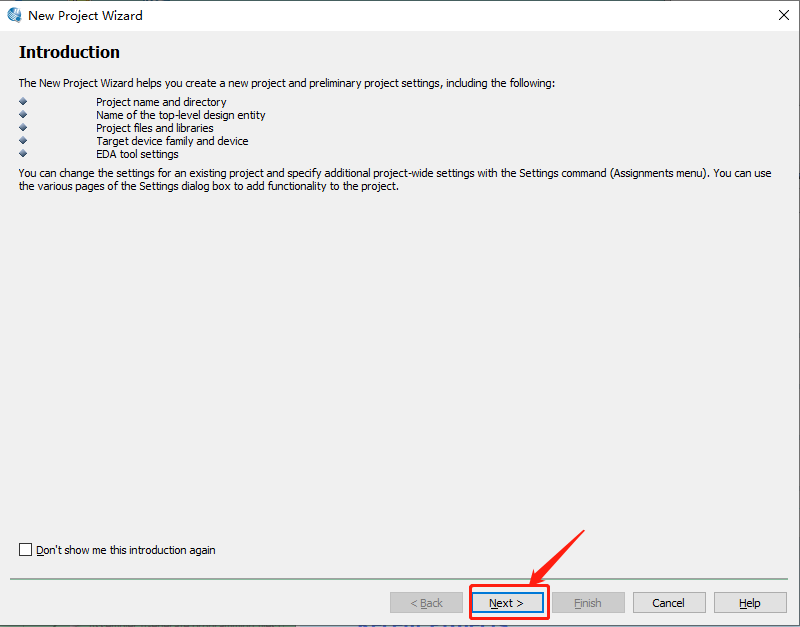

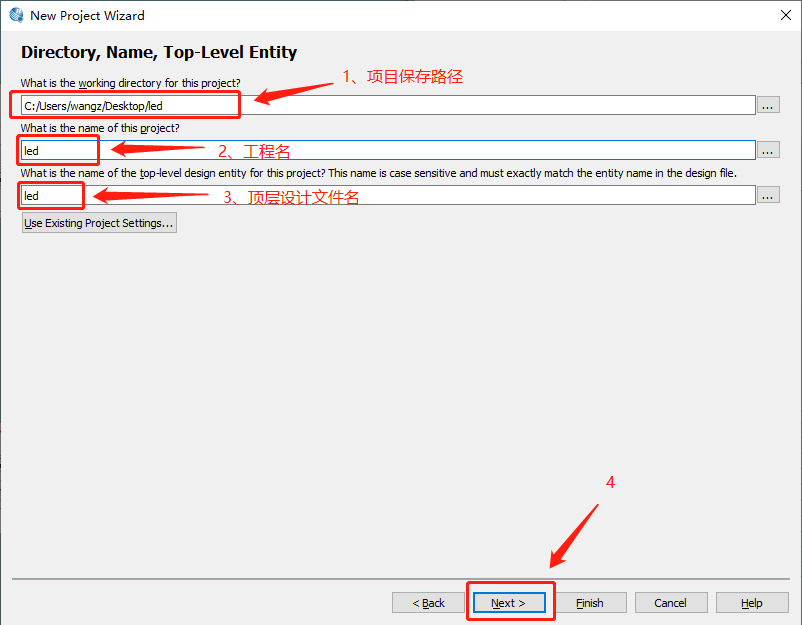

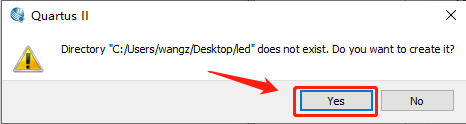

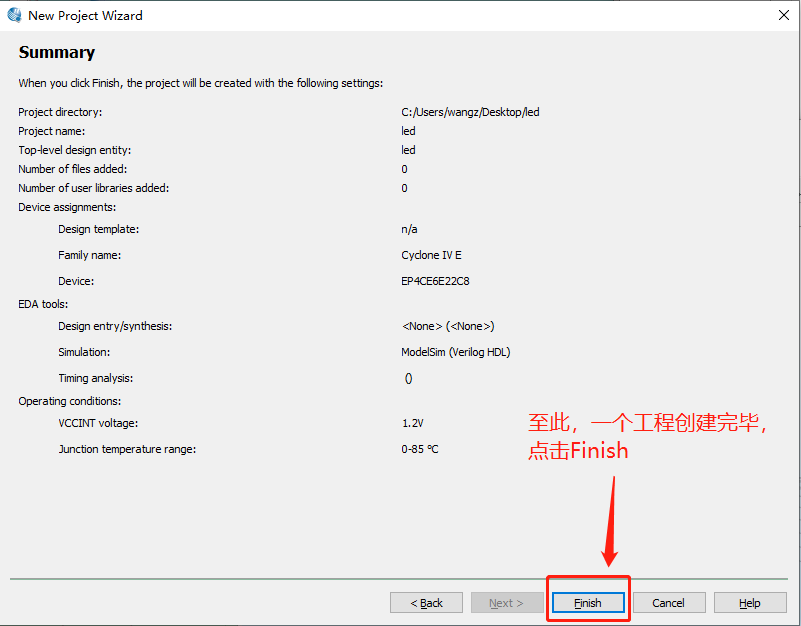

第一步:创建工程,打开Quartus II软件,选择 File->New Project Wizard,如下图:

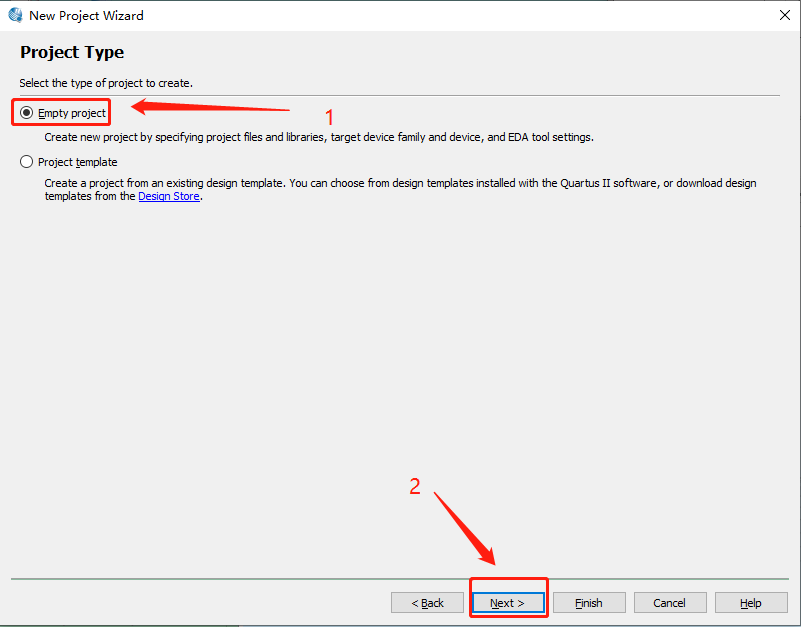

下面选择创建一个空的工程

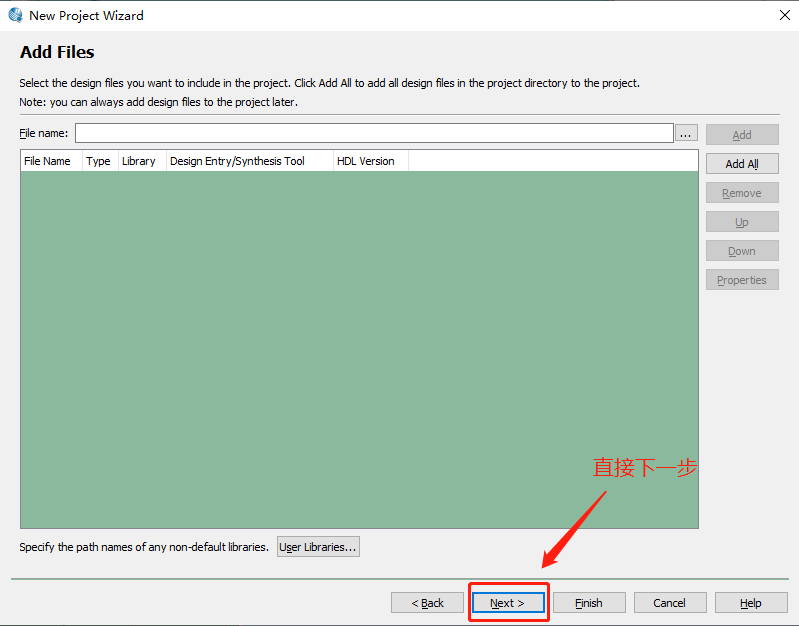

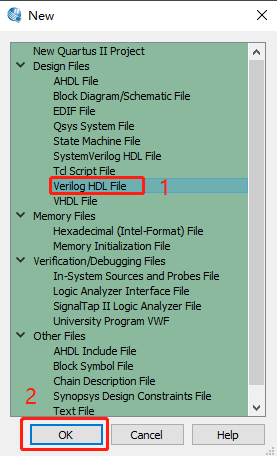

工程创建完毕,接下来就是添加代码文件,在菜单栏选择 File->New

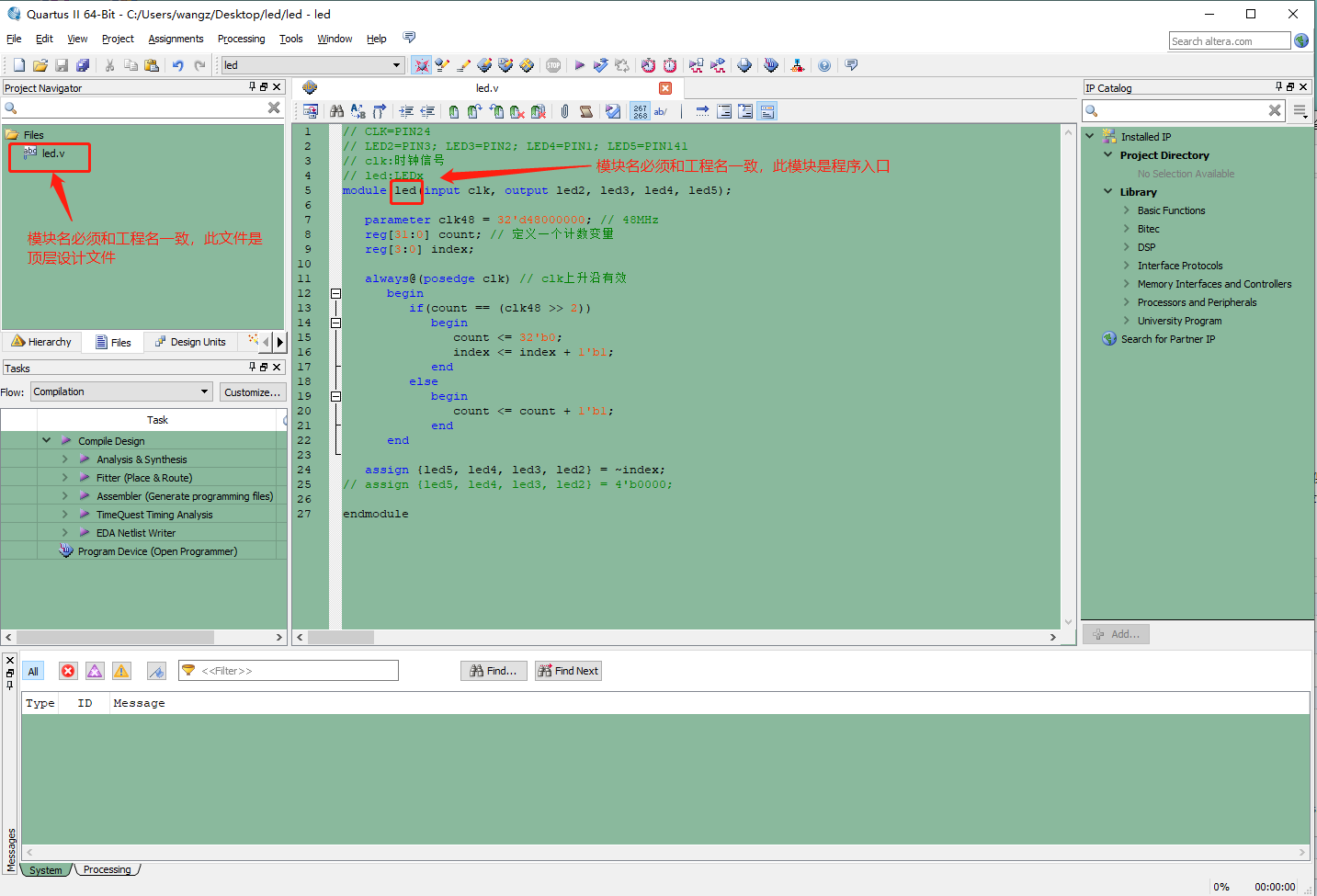

这里我选择的是Verilog HDL语言,文件创建完成后,向文件中添加代码,并保存。注意:保存的时候文件名必须和工程名一致。

我们都知道在单片机中程序入口函数是main函数,但是Quartus II不一样,在Quartus II的工程中必须要有一个顶层设计文件,并且顶层设计文件中的模块名必须和工程名一致。

顶层设计文件名也必须和工程名一致,而这个顶层设计文件中和工程同名的模块就是程序入口。

在单片机中要控制LED就必须要指定IO,并初始化IO,在这里IO不需要我们去初始化,我们只要指定就好了。

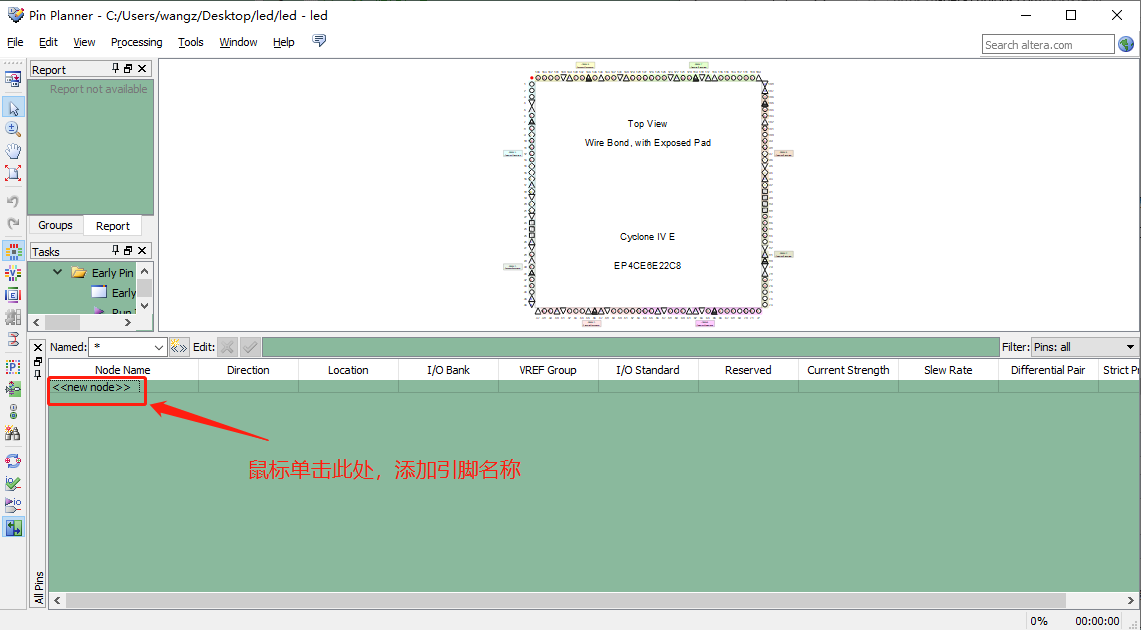

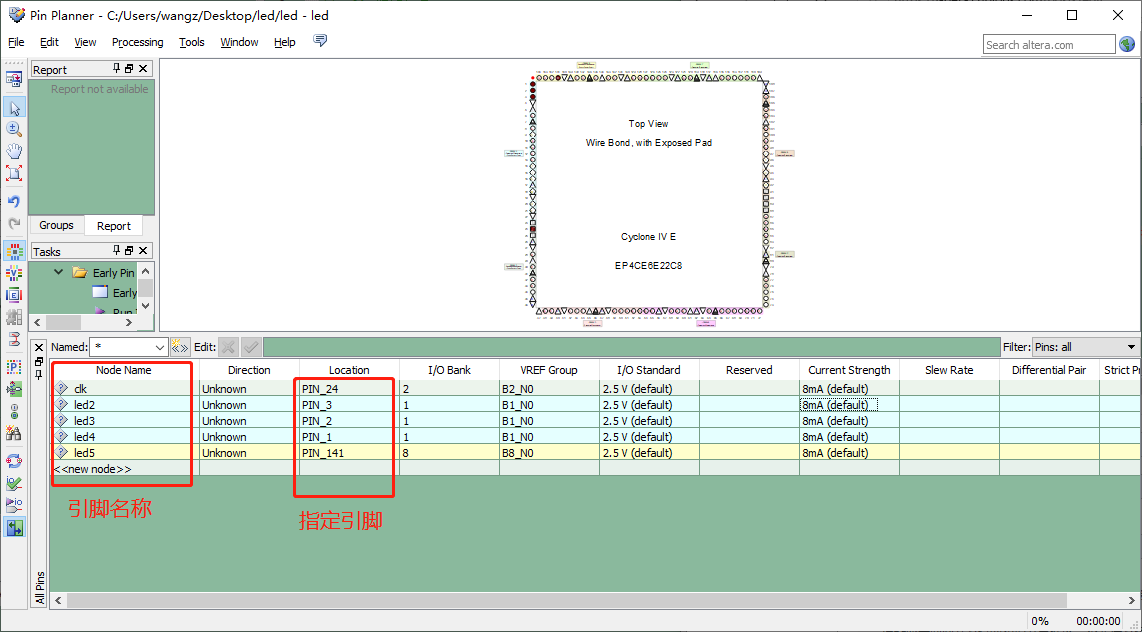

使用快捷键 Ctrl + Shift + N 打开引脚分配窗口,或者菜单栏 Assignments -> Pin Planner 打开引脚分配窗口。

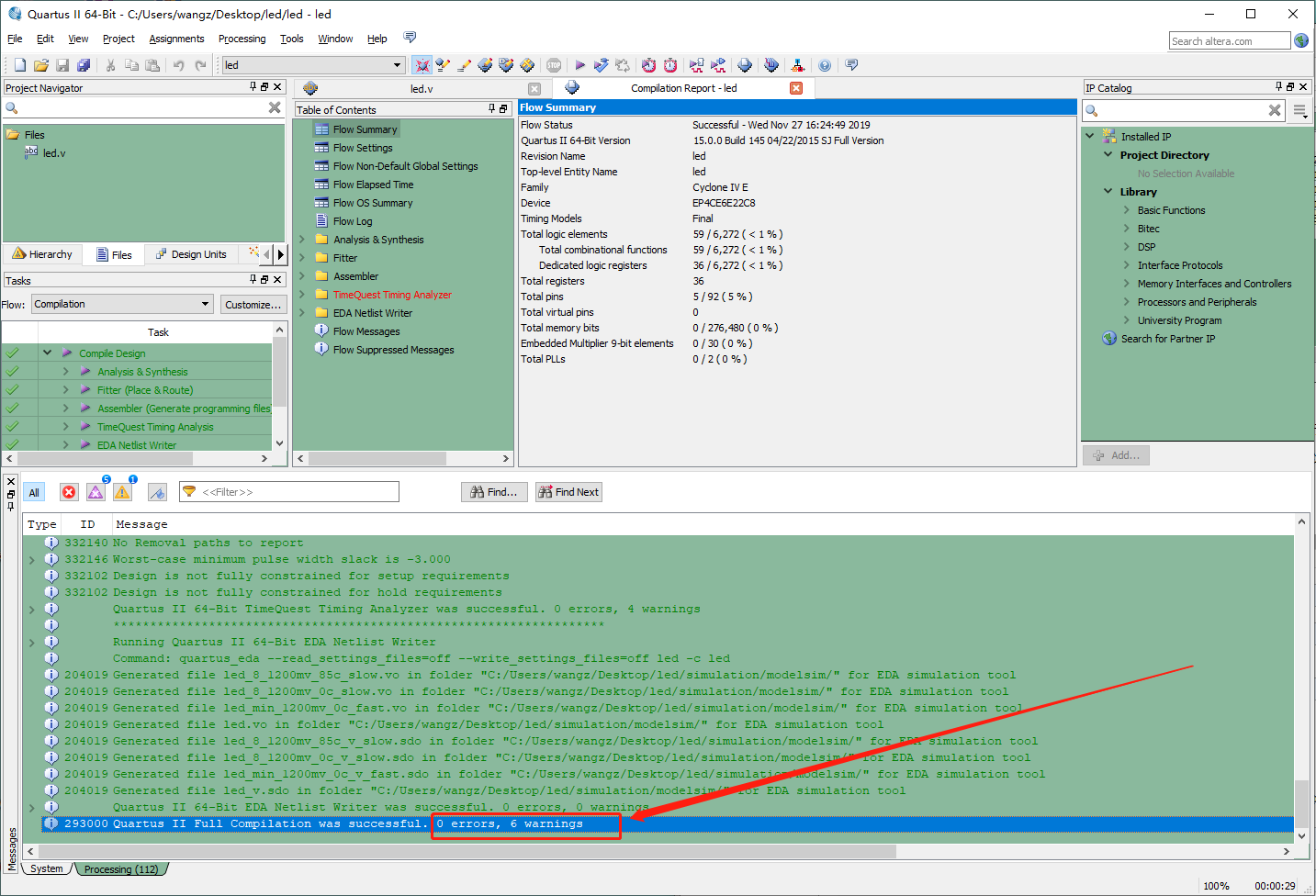

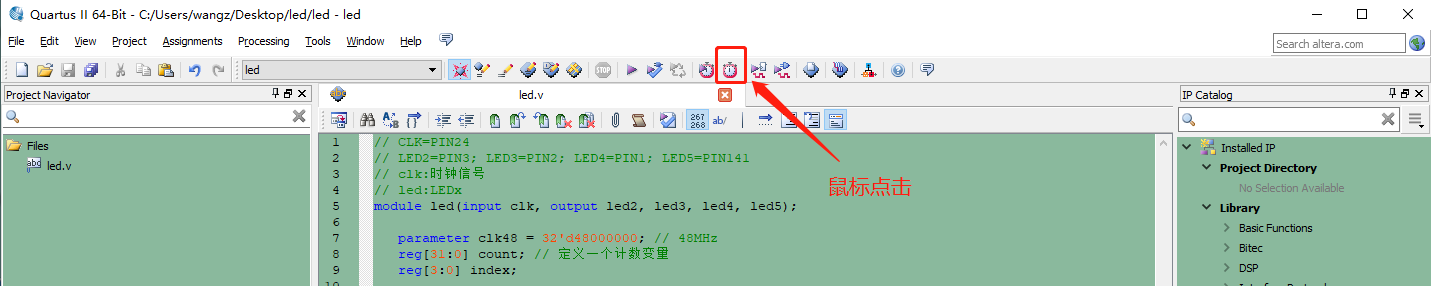

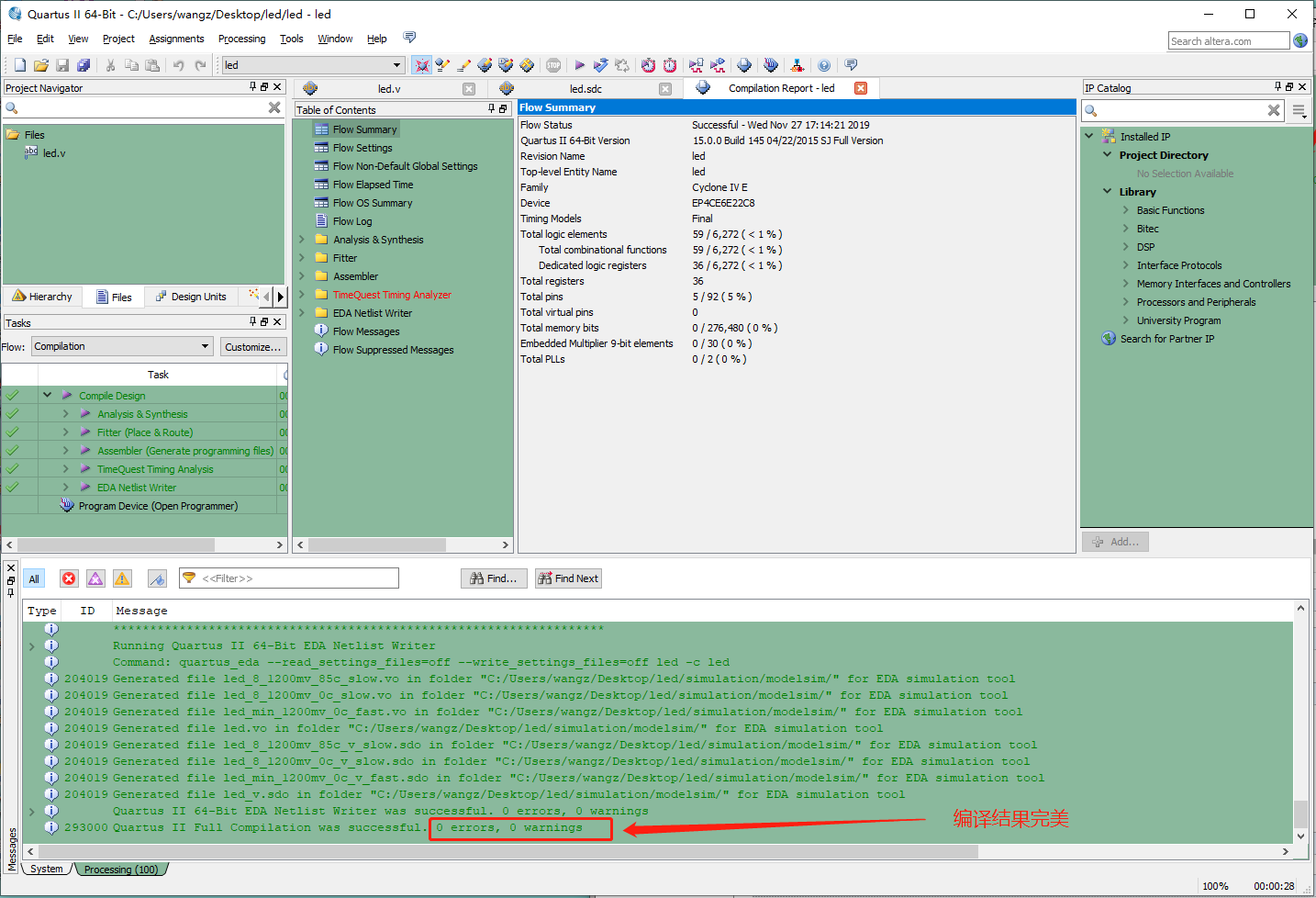

OK启动编译。编译结果:Info (293000): Quartus II Full Compilation was successful. 0 errors, 6 warnings

第一个警告:Warning (15714): Some pins have incomplete I/O assignments. Refer to the I/O Assignment Warnings report for details

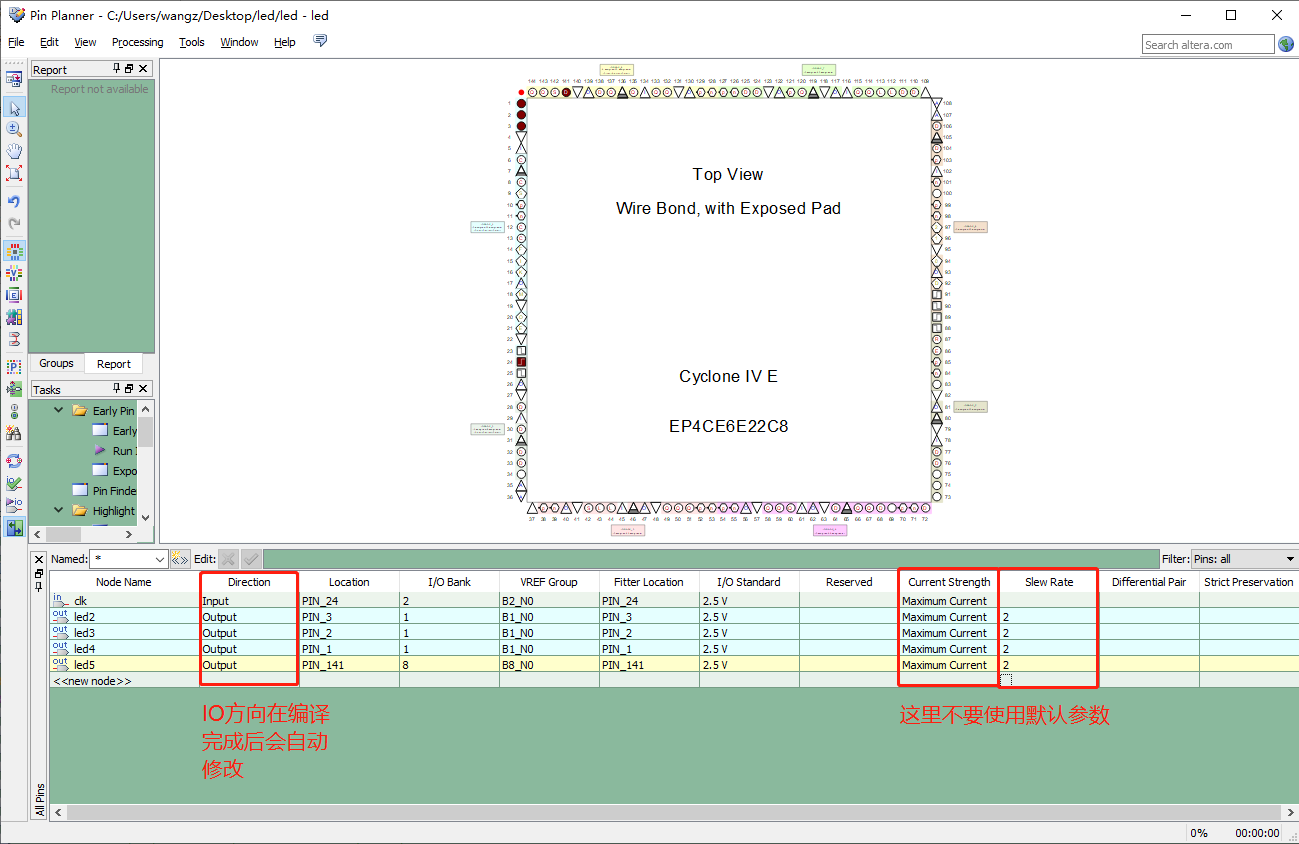

这个警告的意思是IO参数配置不完整,解决方法如下:

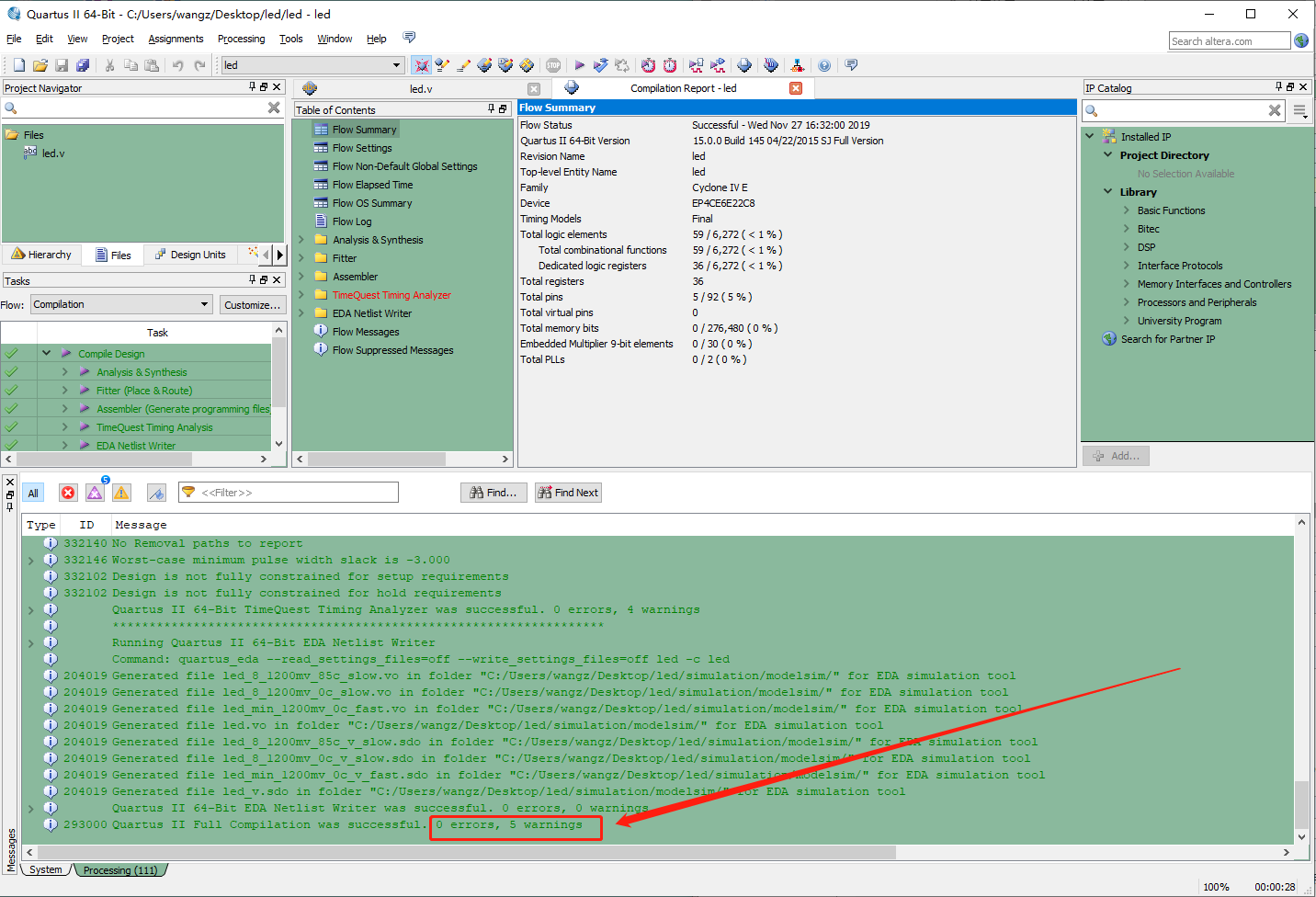

执行编译,编译后还有五个警告。

警告信息如下:

1、Critical Warning (332012): Synopsys Design Constraints File file not found: 'led.sdc'. A Synopsys Design Constraints File is required by the TimeQuest Timing Analyzer to get proper timing constraints. Without it, the Compiler will not properly optimize the design.

2、Critical Warning (332012): Synopsys Design Constraints File file not found: 'led.sdc'. A Synopsys Design Constraints File is required by the TimeQuest Timing Analyzer to get proper timing constraints. Without it, the Compiler will not properly optimize the design.

3、Critical Warning (332148): Timing requirements not met

4、Critical Warning (332148): Timing requirements not met

5、Critical Warning (332148): Timing requirements not met

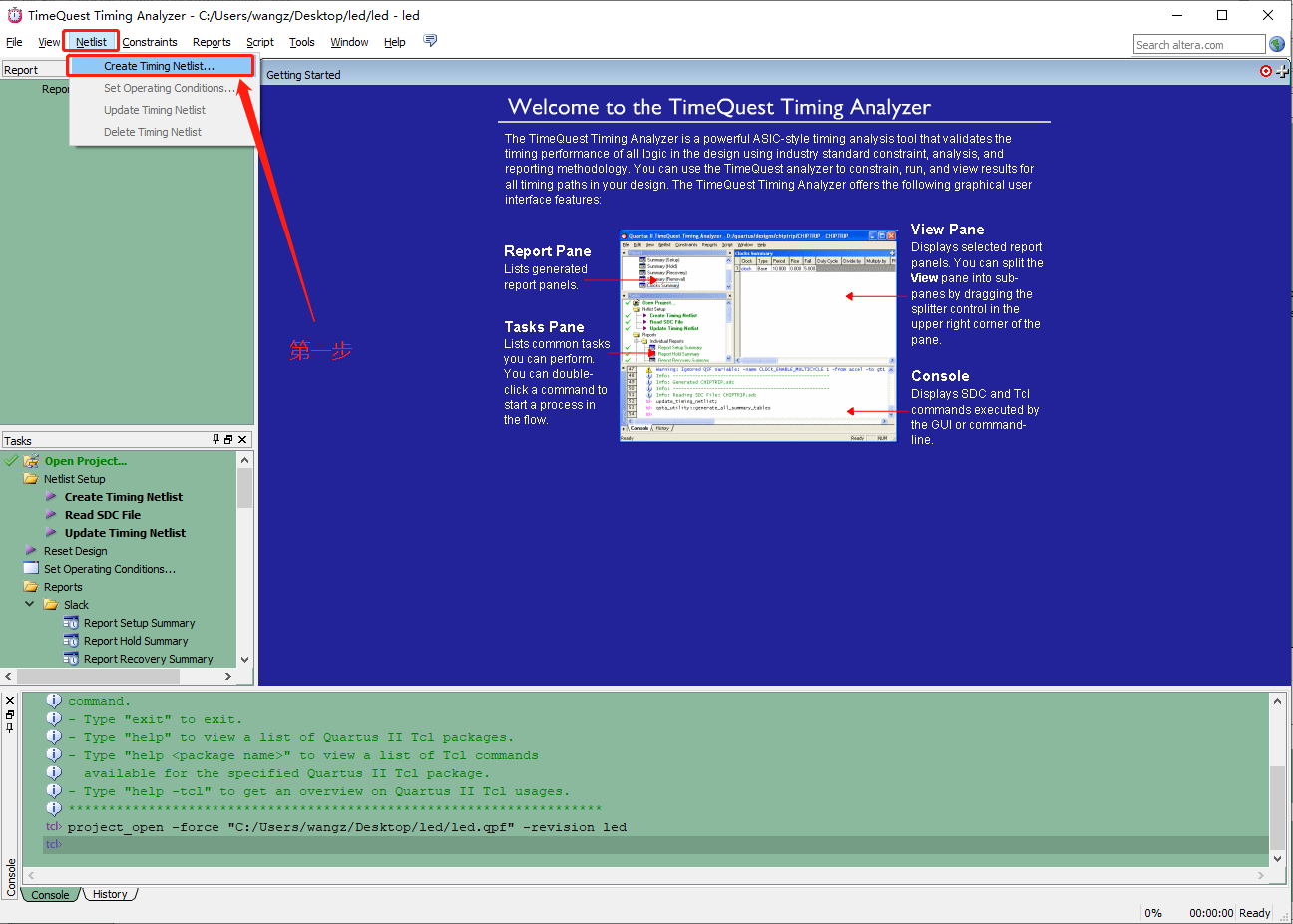

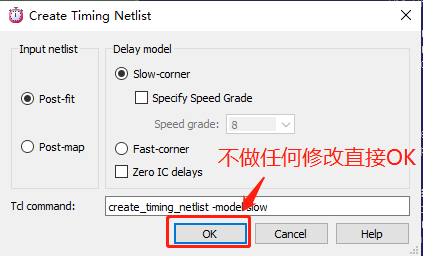

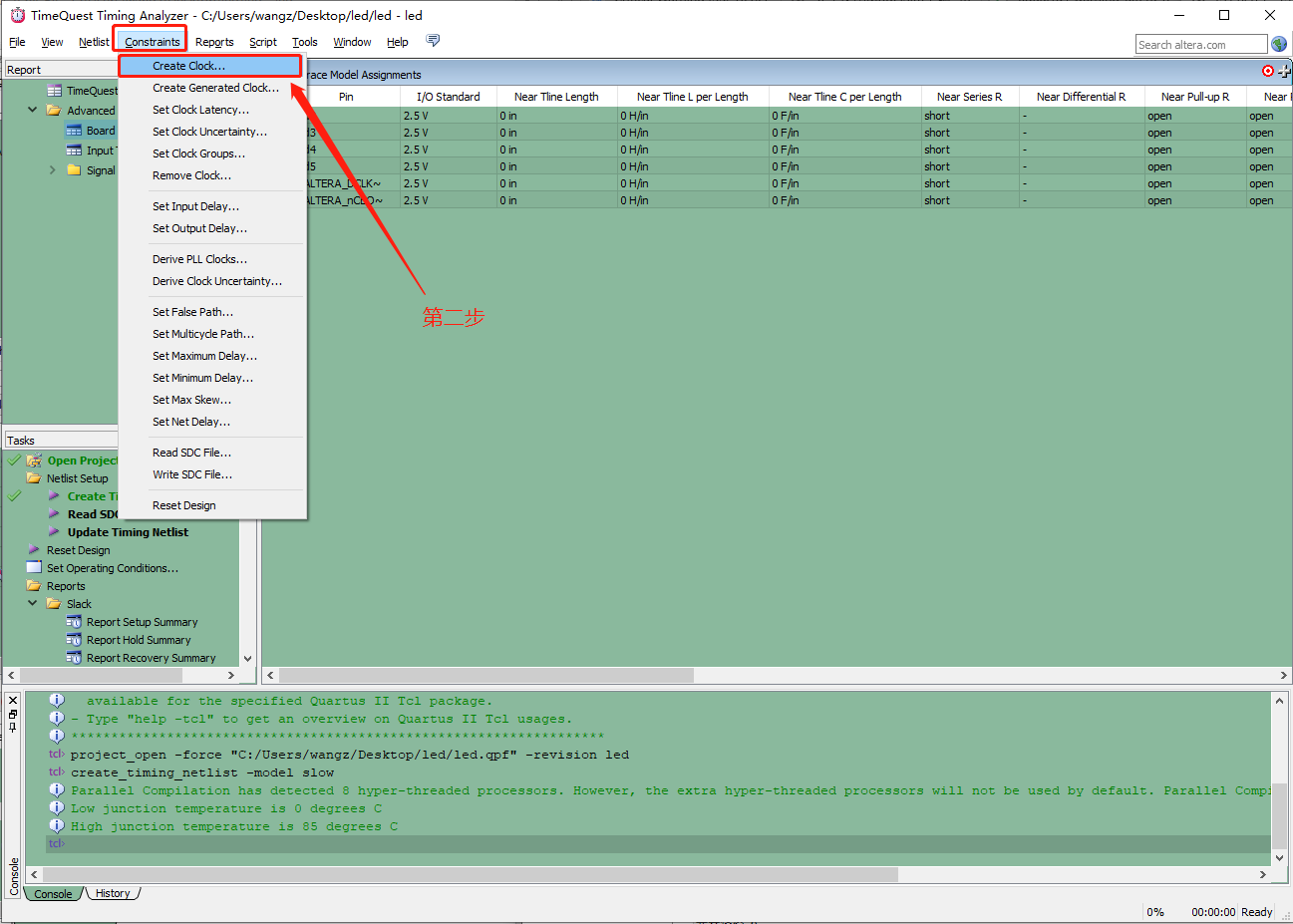

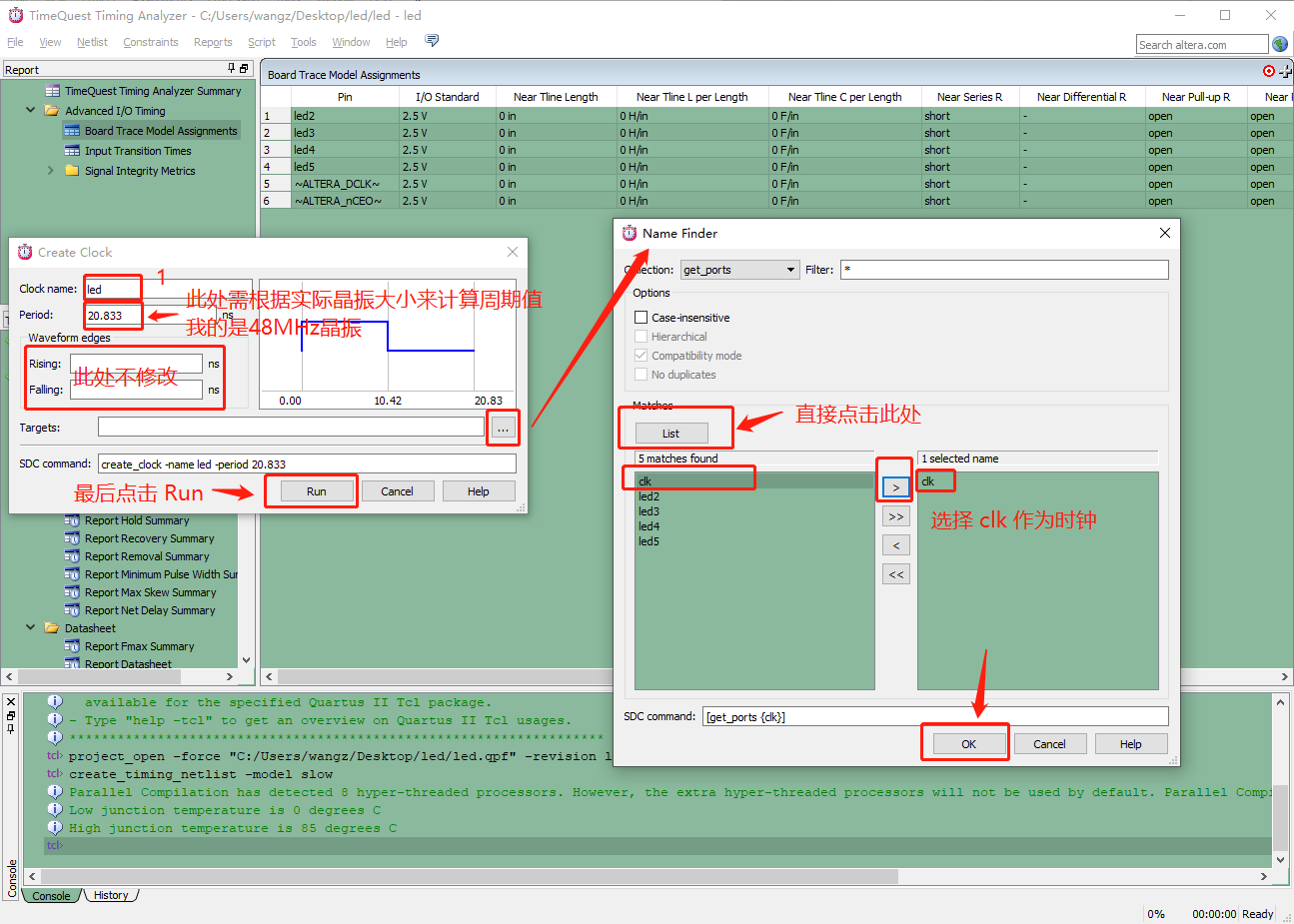

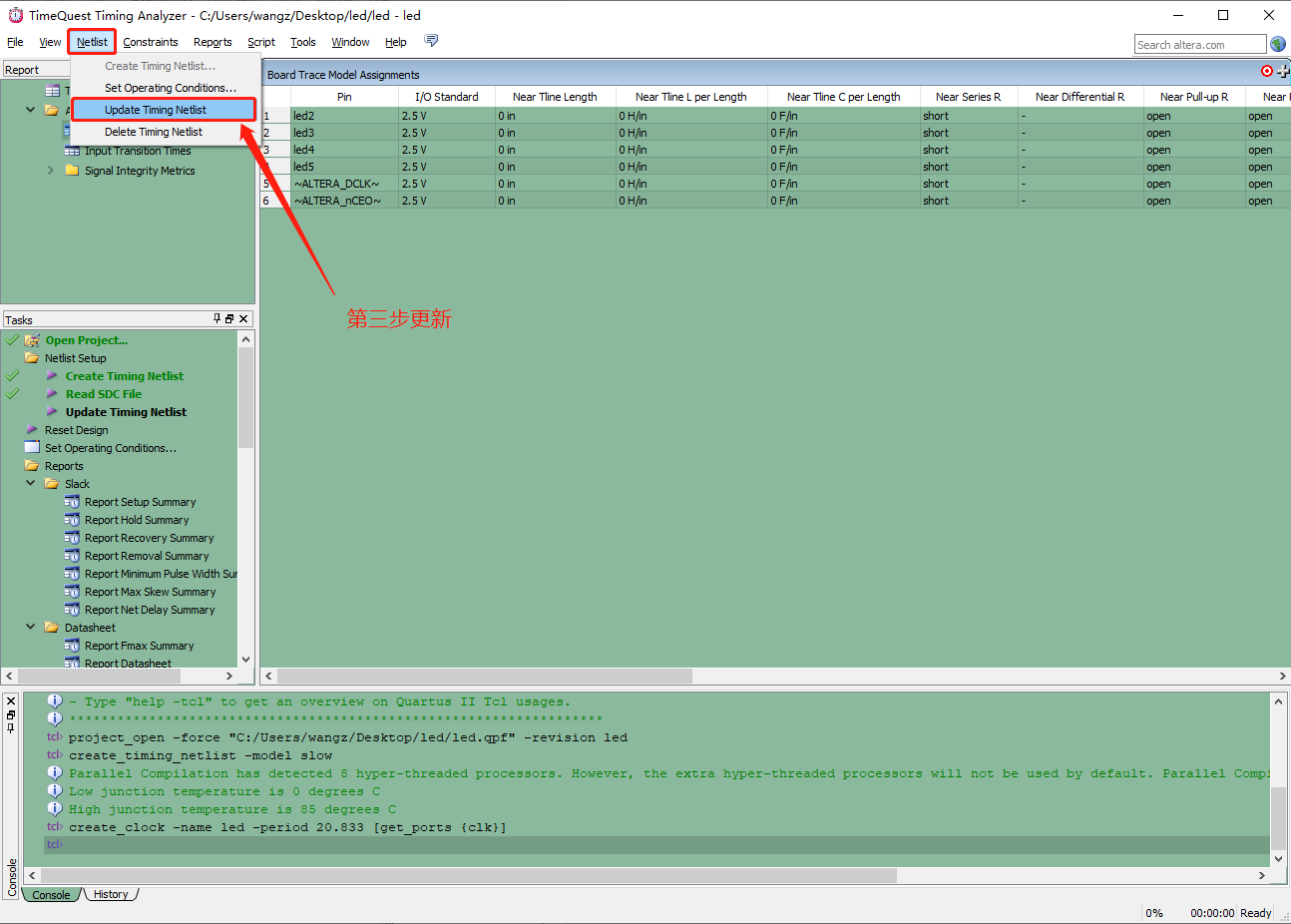

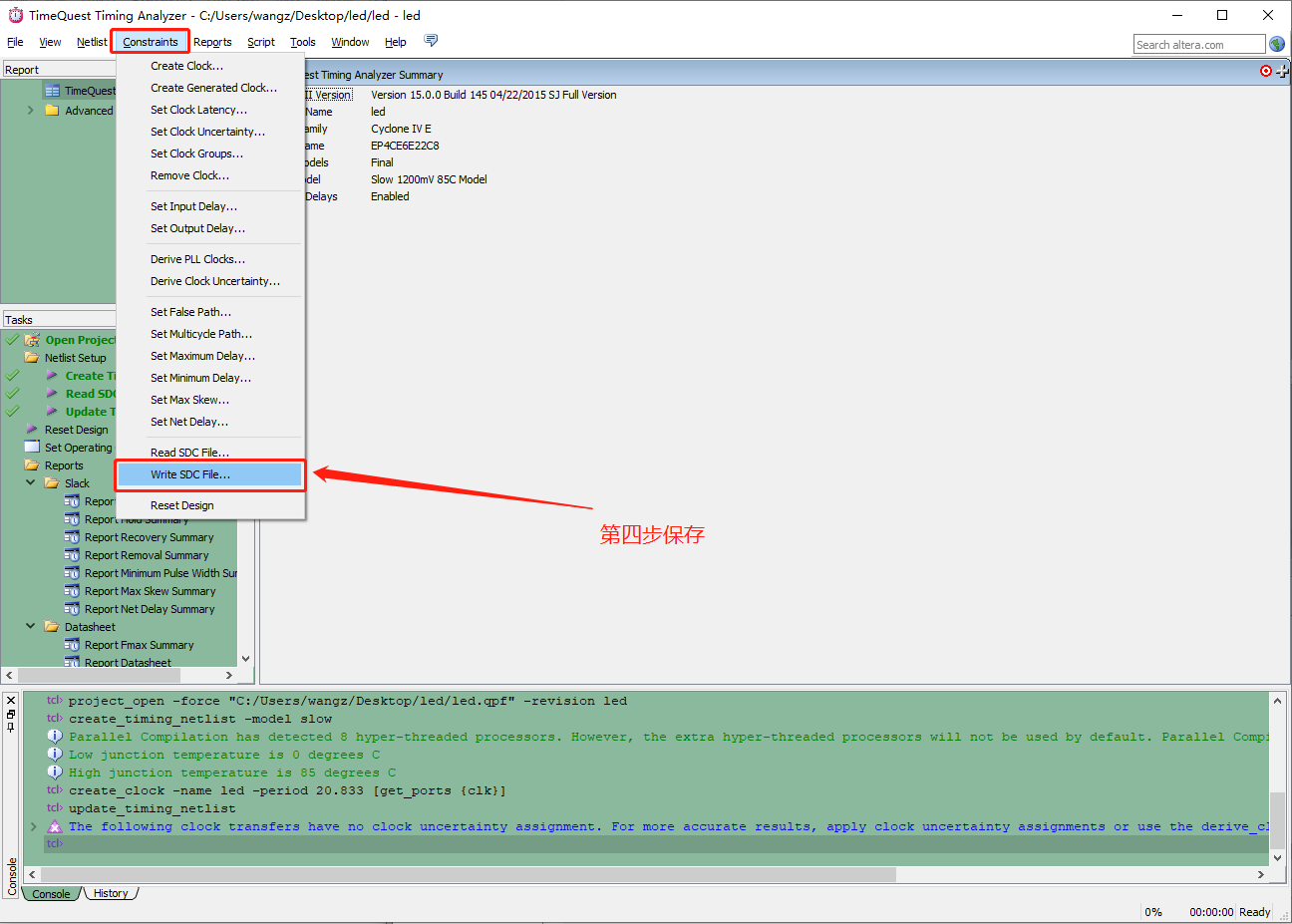

以上警告信息其实是一个时钟约束的问题所导致的,问题解决方法如下:

关闭窗口,再编译一次,编译后发现结果与理想中的不一样,警告信息如下:

1、Critical Warning (332168): The following clock transfers have no clock uncertainty assignment. For more accurate results, apply clock uncertainty assignments or use the derive_clock_uncertainty command.

2、 Critical Warning (332169): From led (Rise) to led (Rise) (setup and hold)

警告信息:时钟传输没有时钟不确定性分配。要获得更精确的结果,请应用时钟不确定性分配或使用derive_clock_uncertainty命令。解决方法如下:

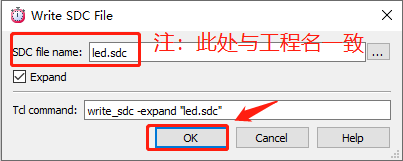

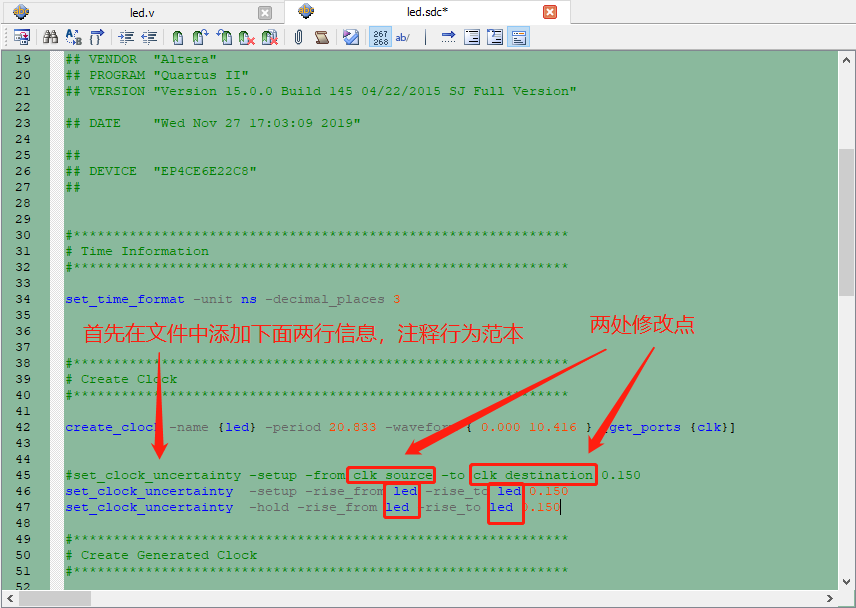

打开我们刚保存的 led.sdc 文件,该文件就在工程目录下,然后添加两行信息,并将 clk_source 和 clk_destination 改为自己设置的 Clock name(第二步中 Create Clock 窗口中设置的 Clock name,我设置的 Clock name 是 led)。

添加信息如下:

#set_clock_uncertainty -setup -from clk_source -to clk_destination 0.150

set_clock_uncertainty -setup -rise_from led -rise_to led 0.150

set_clock_uncertainty -hold -rise_from led -rise_to led 0.150

保存文件再编译,编译结果如下:

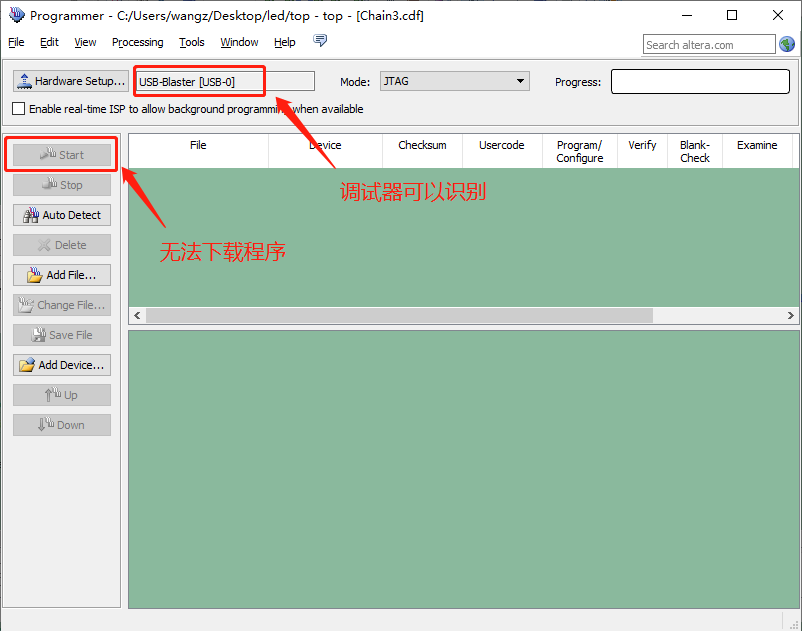

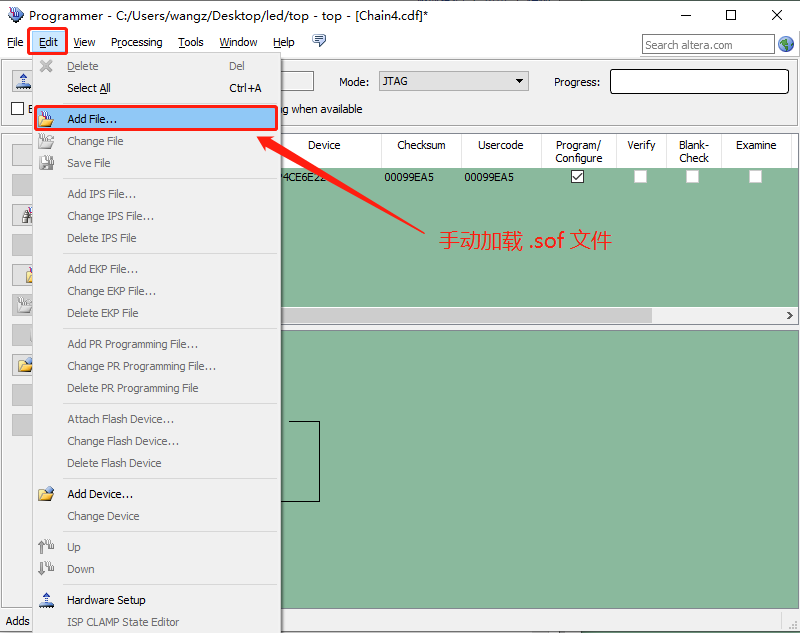

修改后编译警告没有了,打开下载窗口下载程序。此时发现可以识别调试器,但是 Start 按钮是灰色的,无法点击。

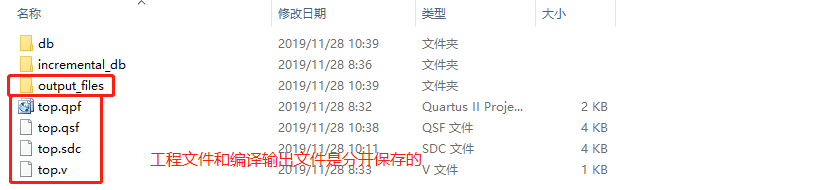

导致这个问题的原因是 Programmer 软件只会查找工程文件所在路径,当生成文件和工程文件不在同一路径下,就会导致这一问题。

解决方法如下:

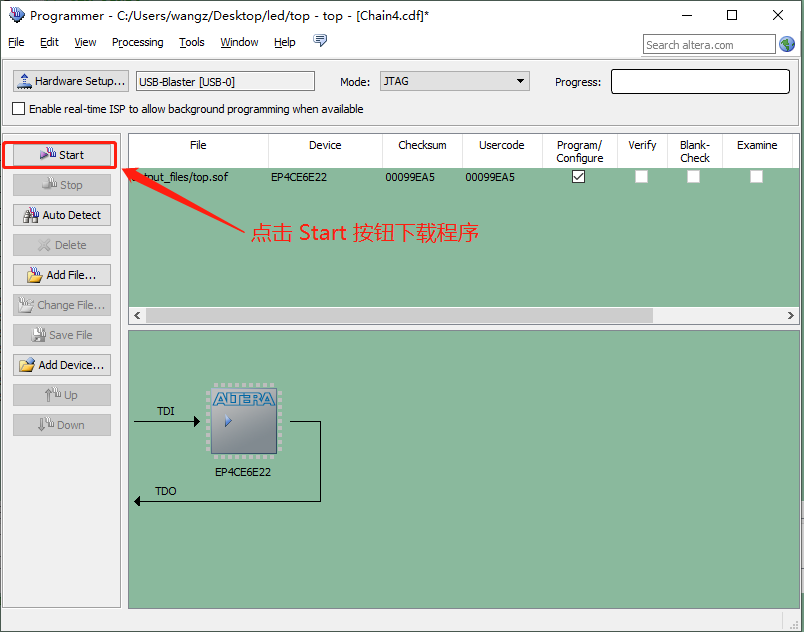

Quartus II 的第一个工程创建到此就结束了,最后烧写代码至开发板运行测试。下载后运行结果正常。

勤能补拙,遇到问题时,不要为了解决问题而解决问题,要找到问题产生的原因。

总结一句:不但要知其然,还要知其所以然。