计数器,寄存器

寄存器

寄存器的顺序一般是:Q0Q1Q2Q3

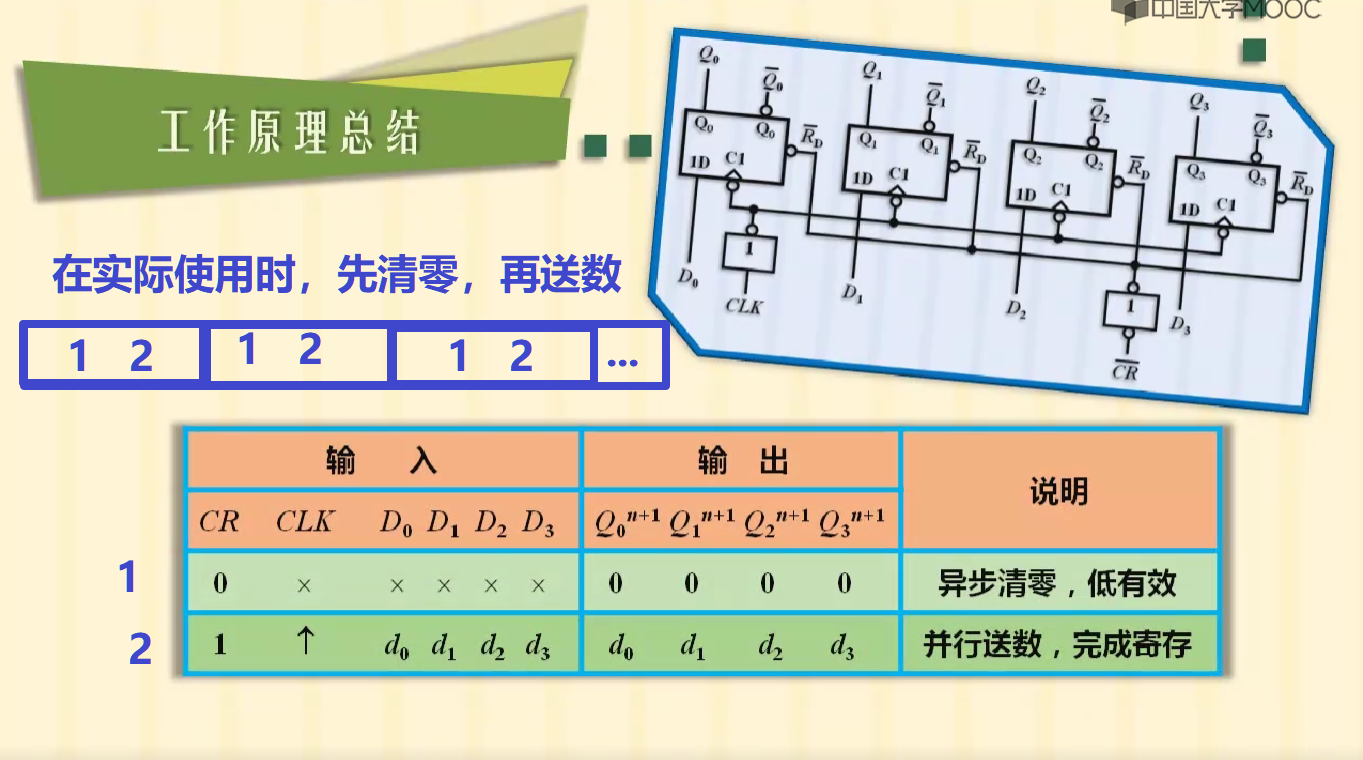

基本寄存器

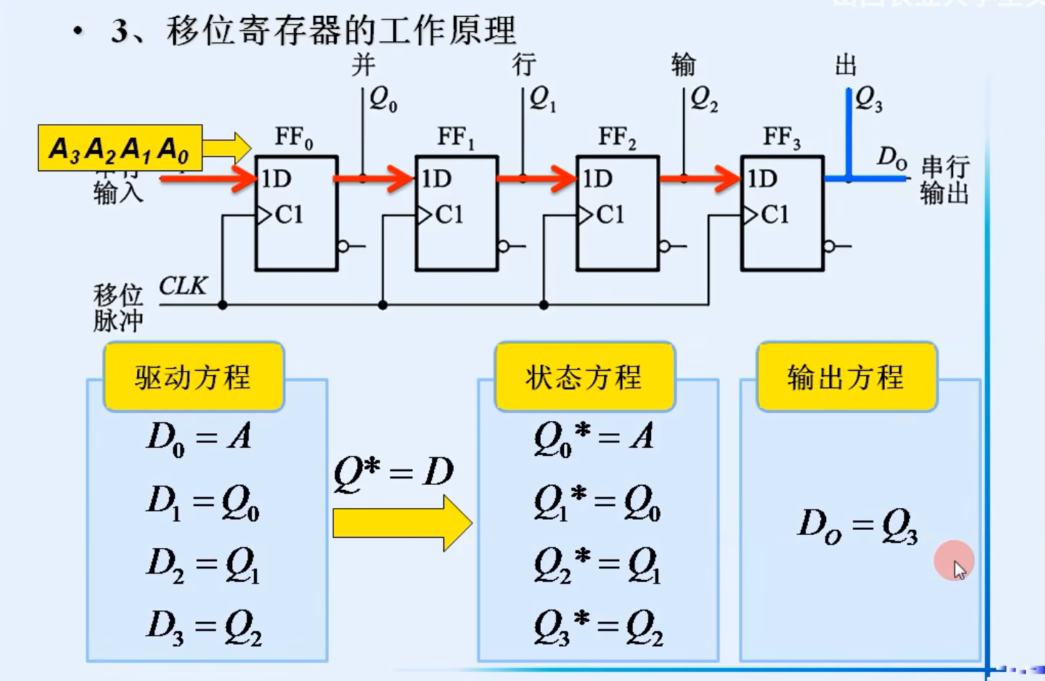

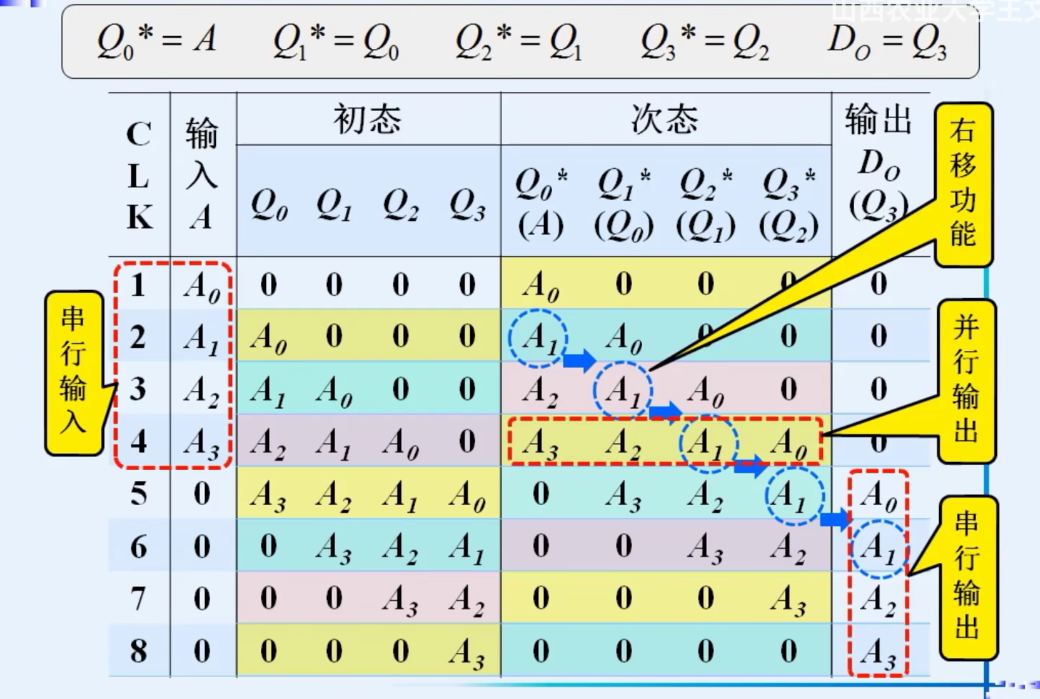

移位寄存器

移位寄存器可以看做一个队列,里面的数据在移位脉冲的作用下依次往前走,它可以实现:

- 存储数据

- 串并行转换

- 移位计数器(请看计数器>各种计数器>寄存器型计数器)

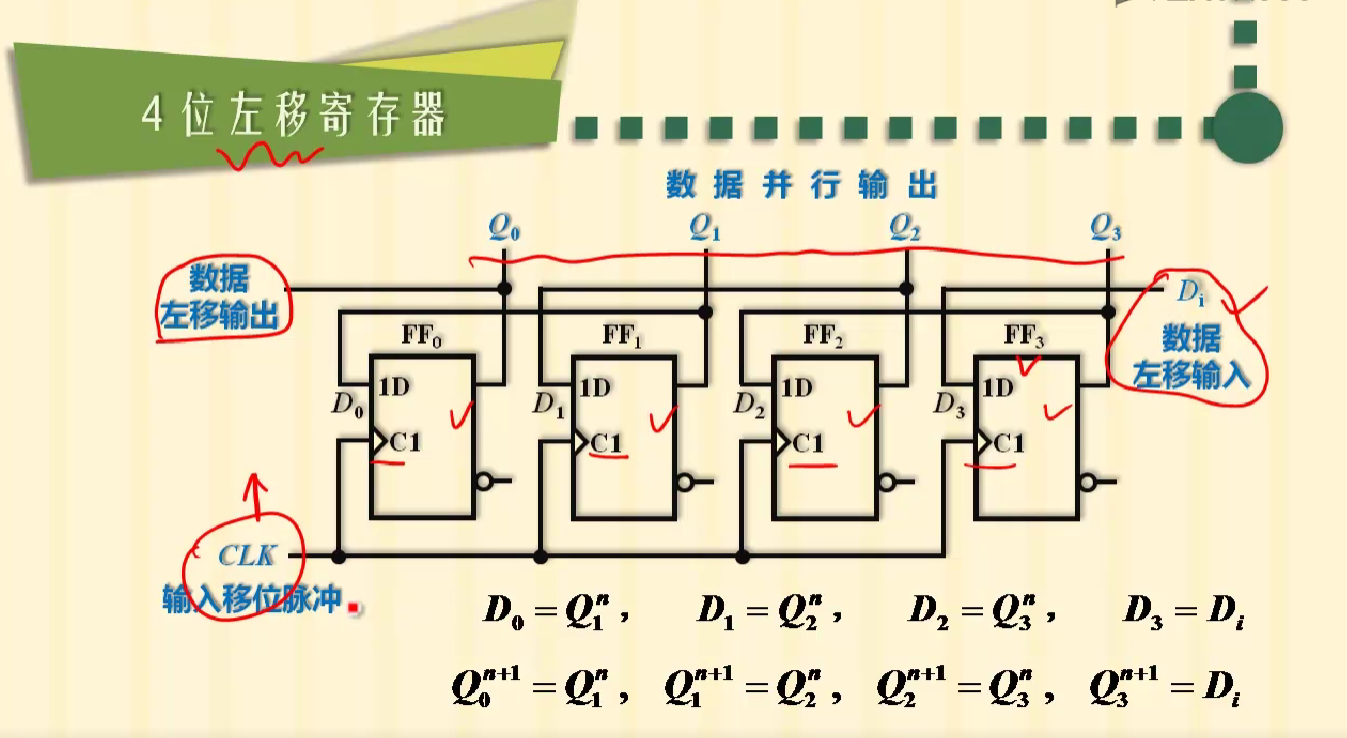

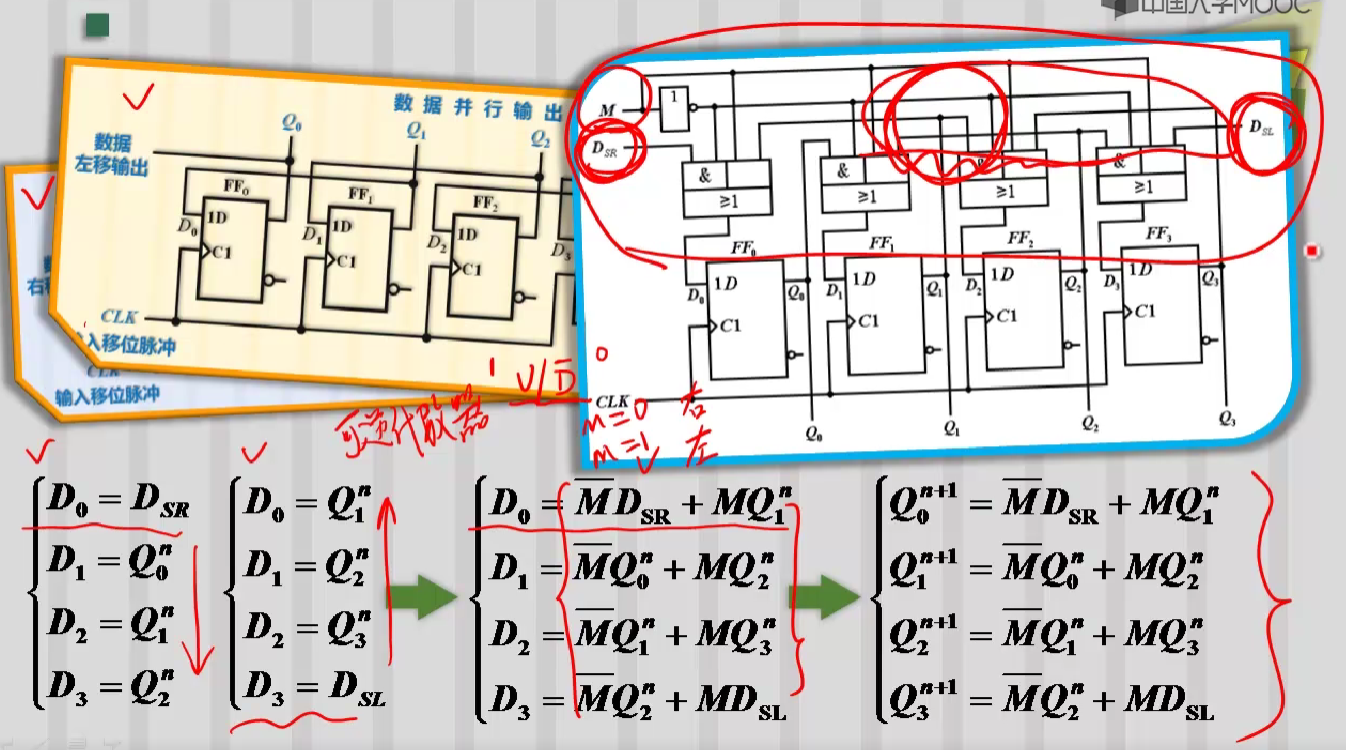

左移和双向移动寄存器

左移寄存器:

双向移动寄存器:

实现的思路和下面的可逆计数器一样,增加一个控制端M。看看方程就行了。

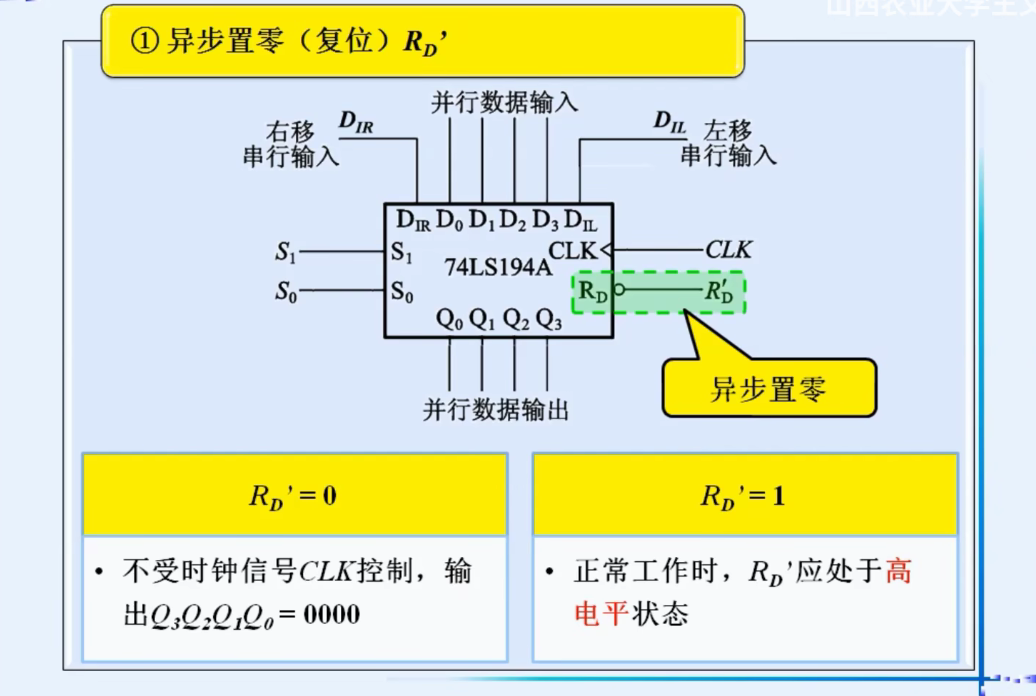

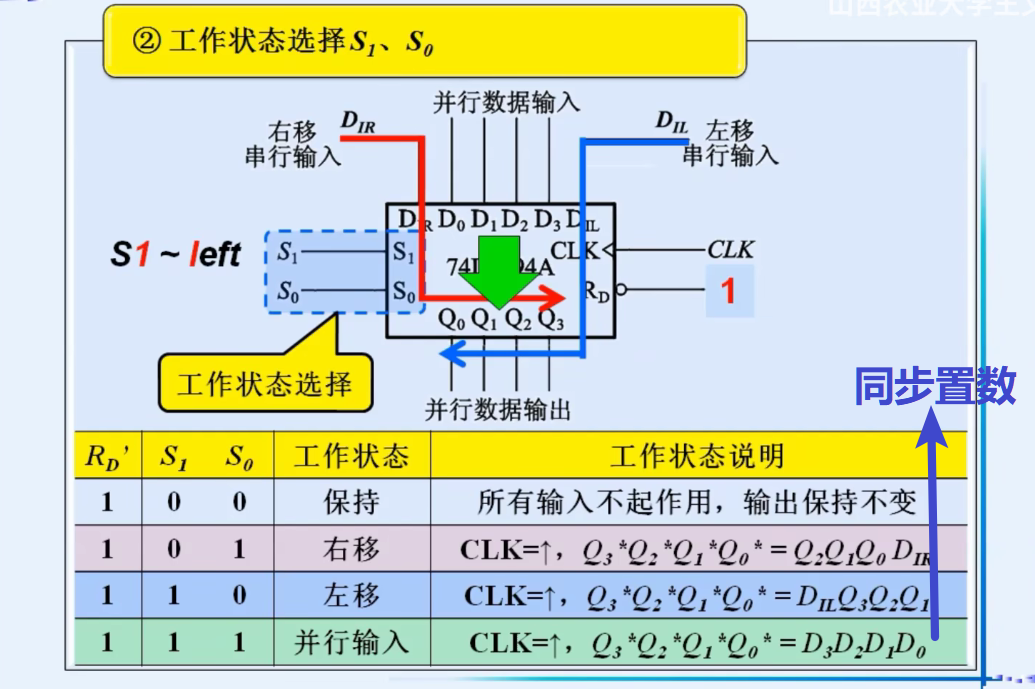

双向移位寄存器74194

异步置零:

同步置数:

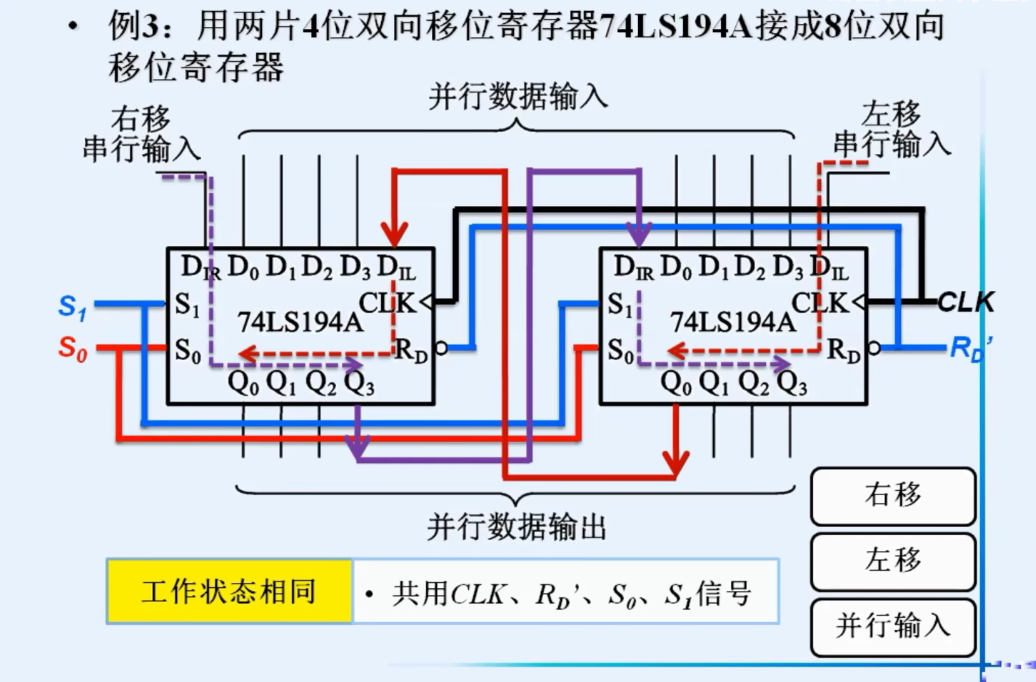

双向移位寄存器的扩展

扩展一共五组线:

- 两个时钟连在一起

- 两个清零连在一起

- 两个控制S0,S1连在一起

- 左边的Q3连右边的右移输入

- 右边的Q0连左边的左移输入

寄存器型计数器

请看计数器>各种计数器>寄存器型计数器

计数器

计数器的顺序一般是:

Q3 Q2 Q1 Q0

8 4 2 1

计数器的设计与实现

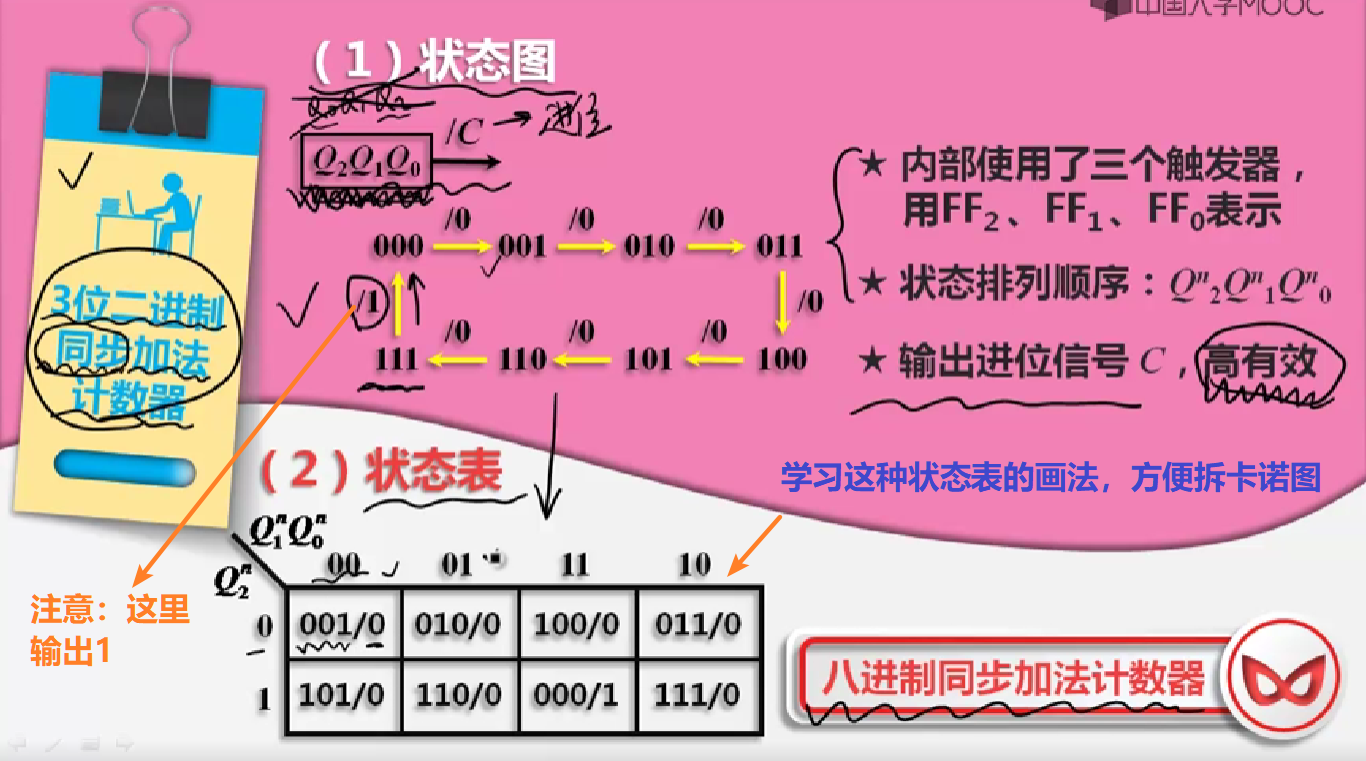

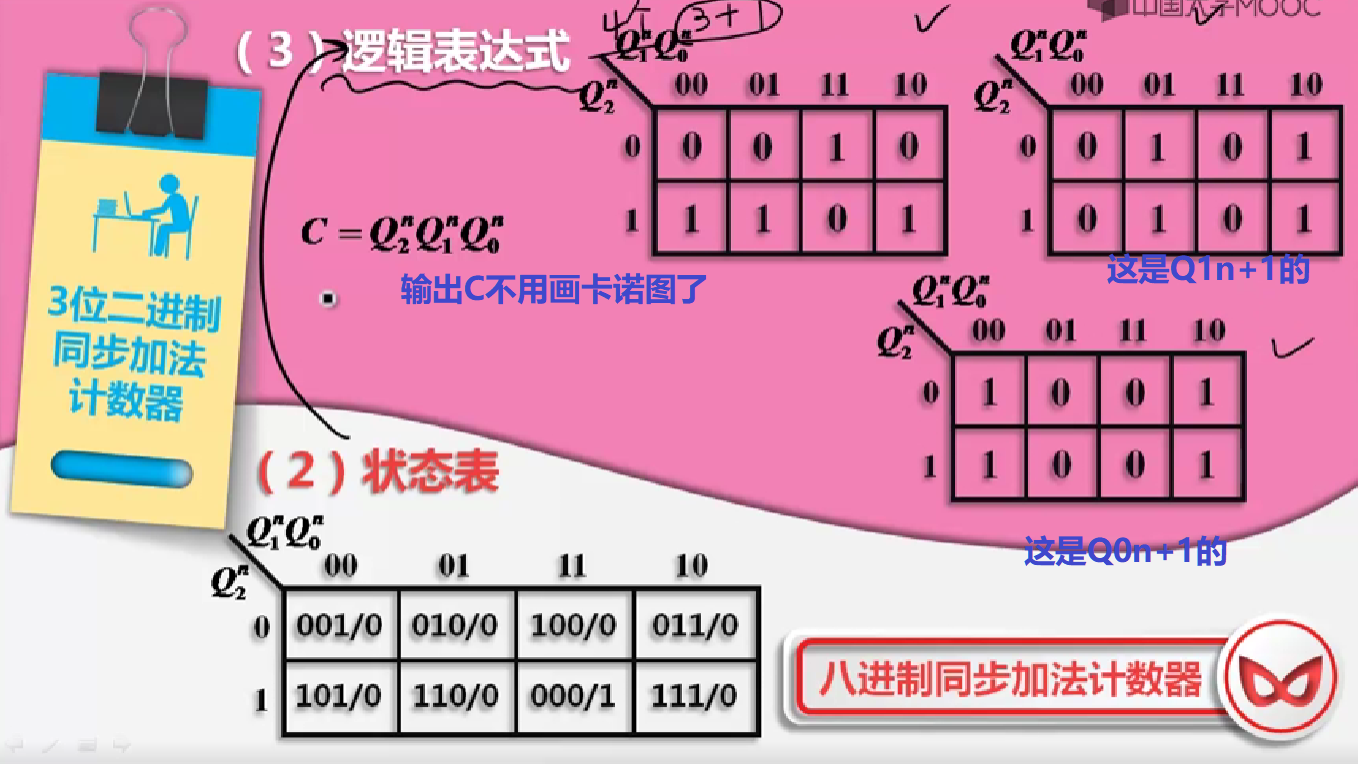

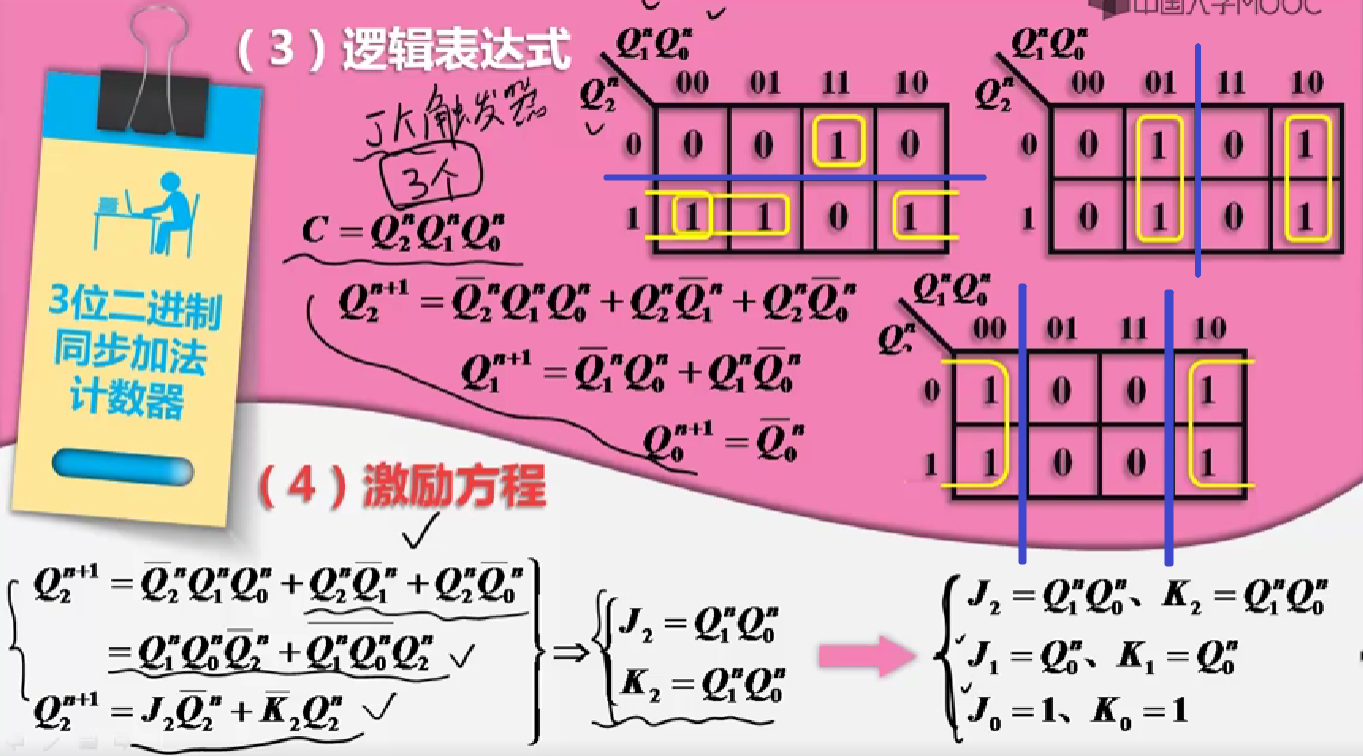

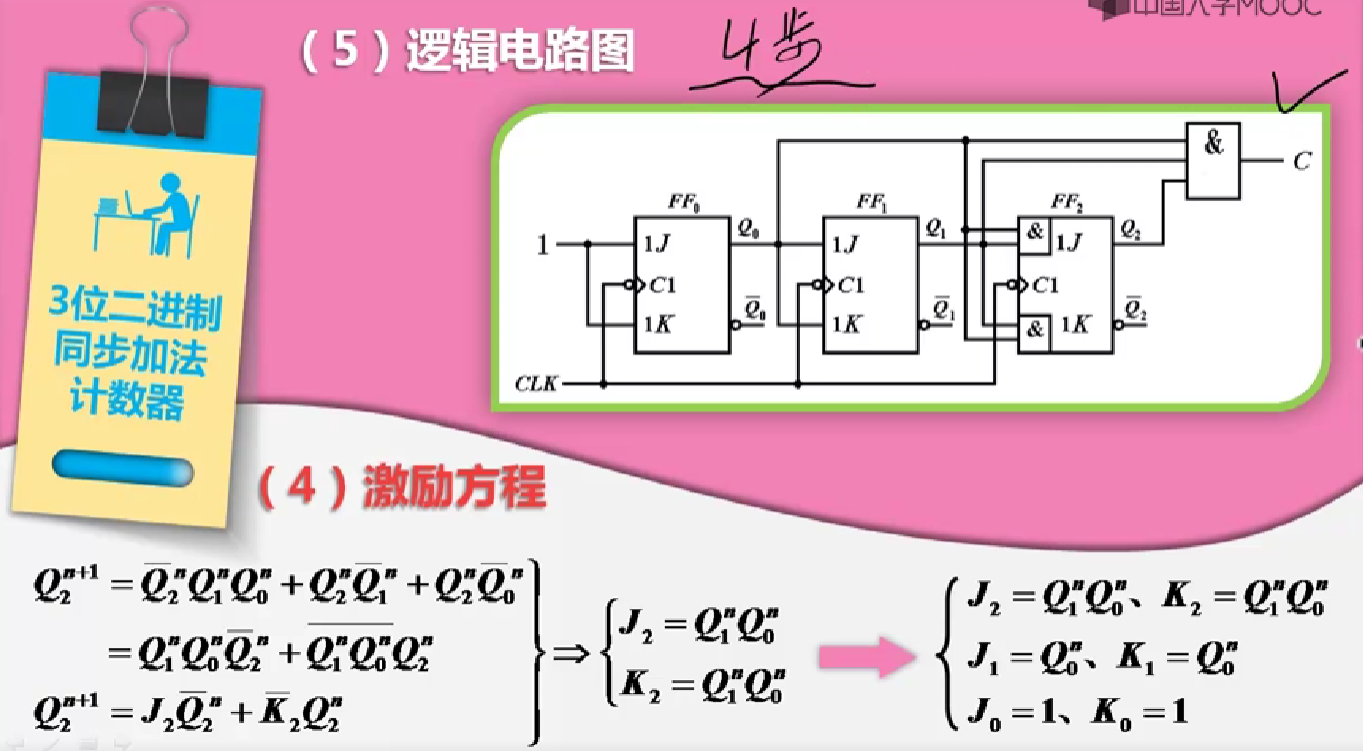

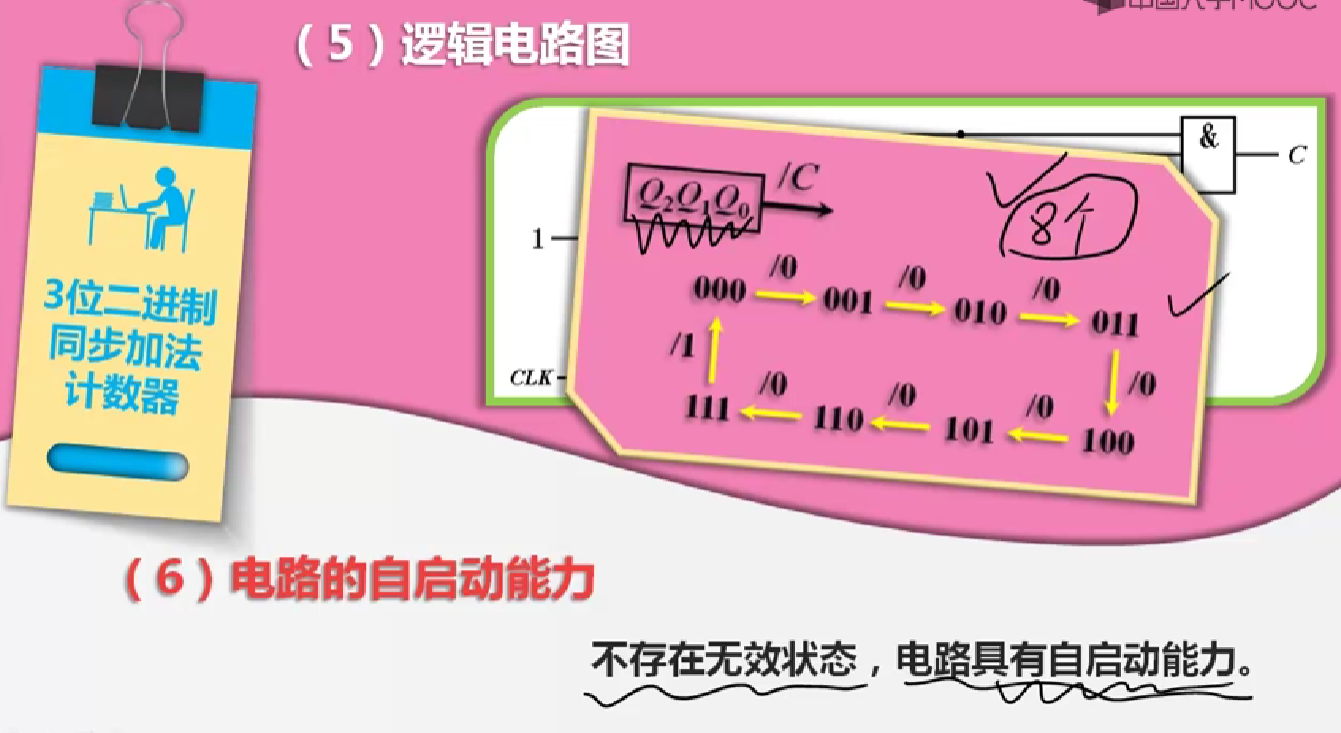

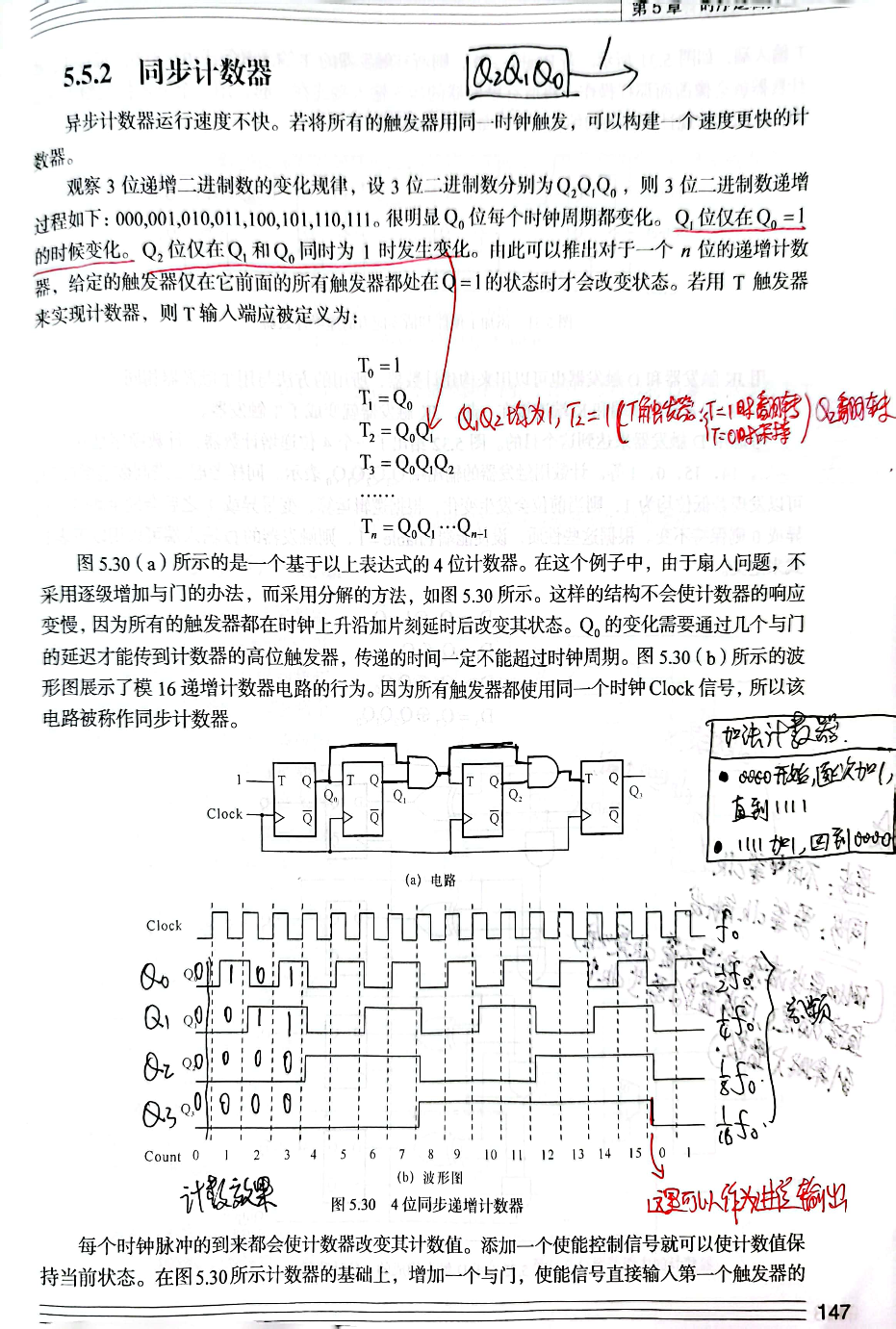

1、以3位二进制同步加法计数器为例

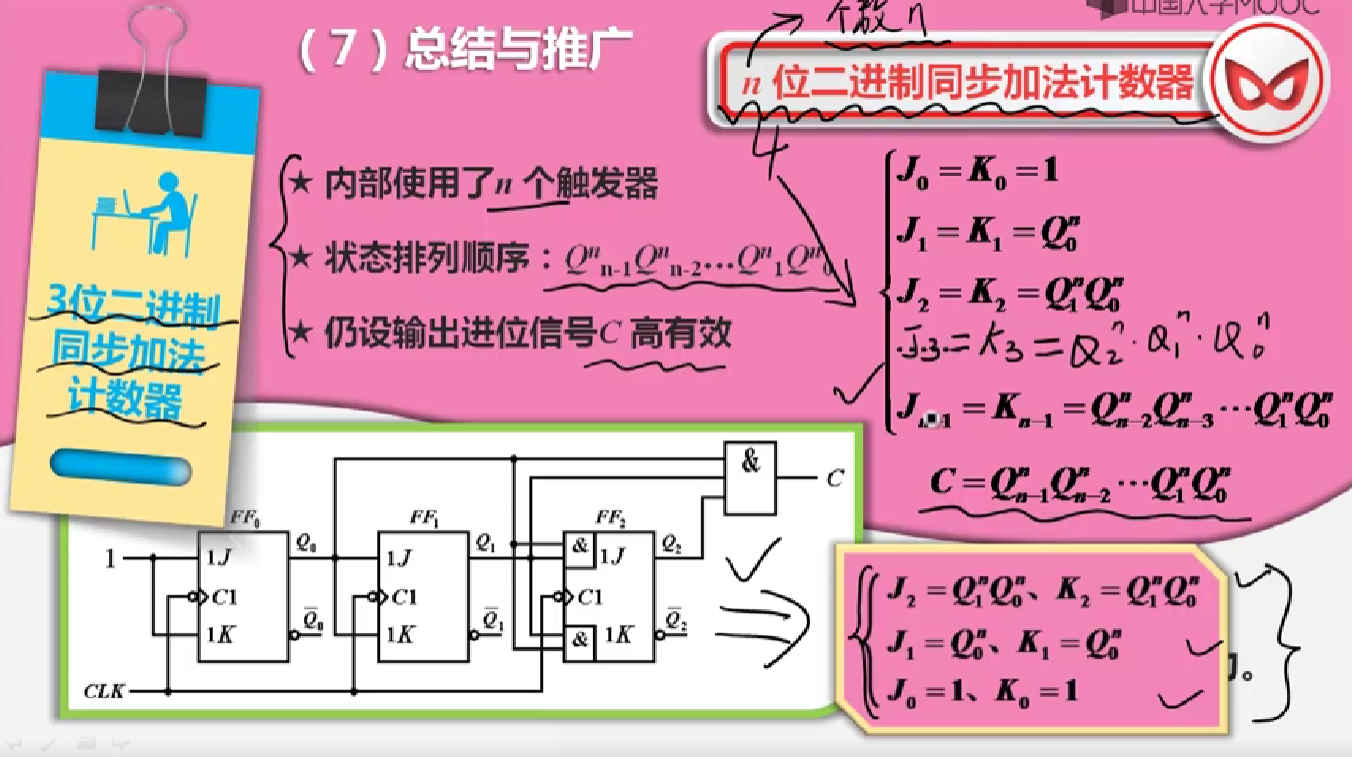

由此衍生出n位二进制同步加法计数器用jk触发器实现的方程:

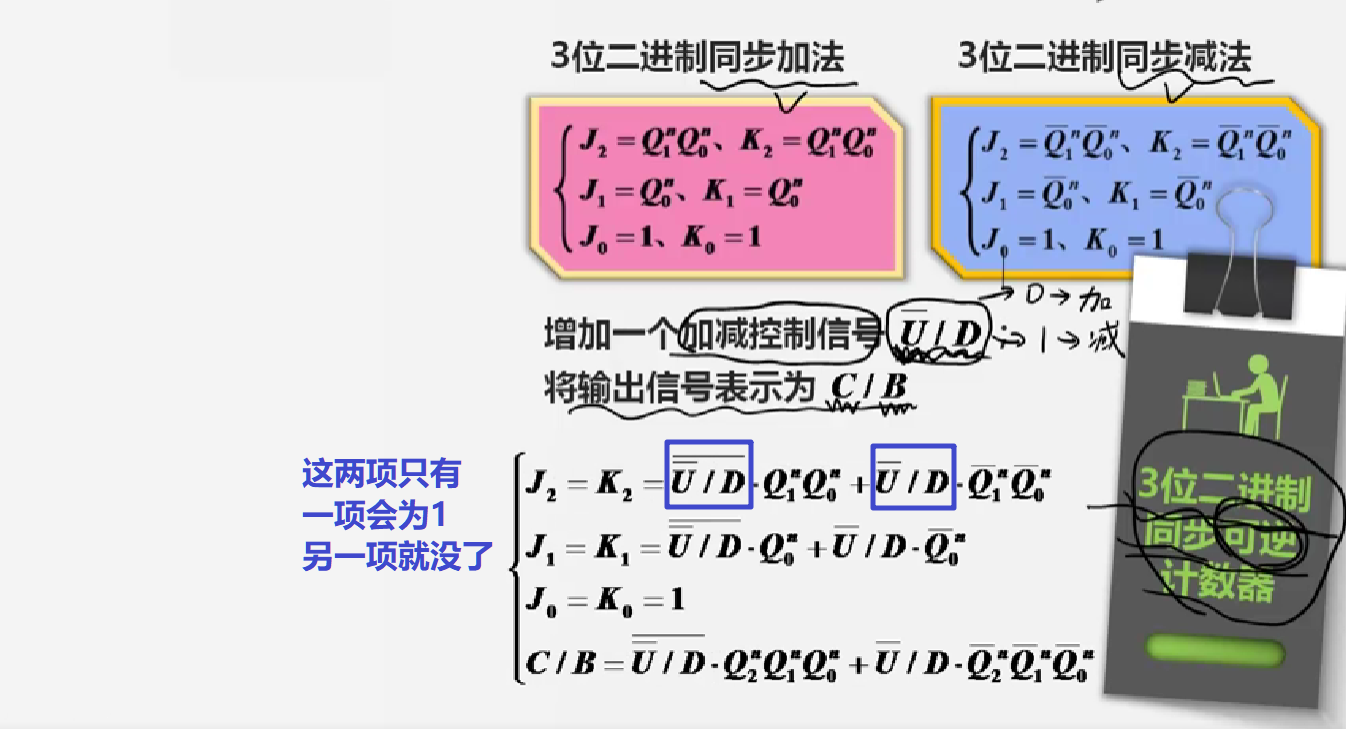

还有减法计数器的方程:

可逆计数器的方程:加了一个加减控制信号

书上用T触发器实现的:

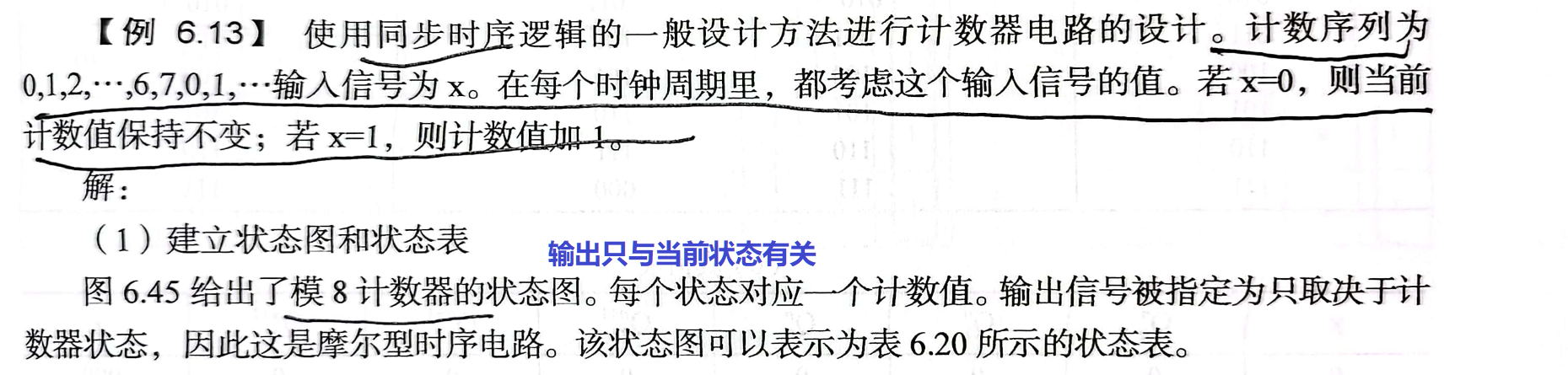

2、添加一个控制信号x

状态图:

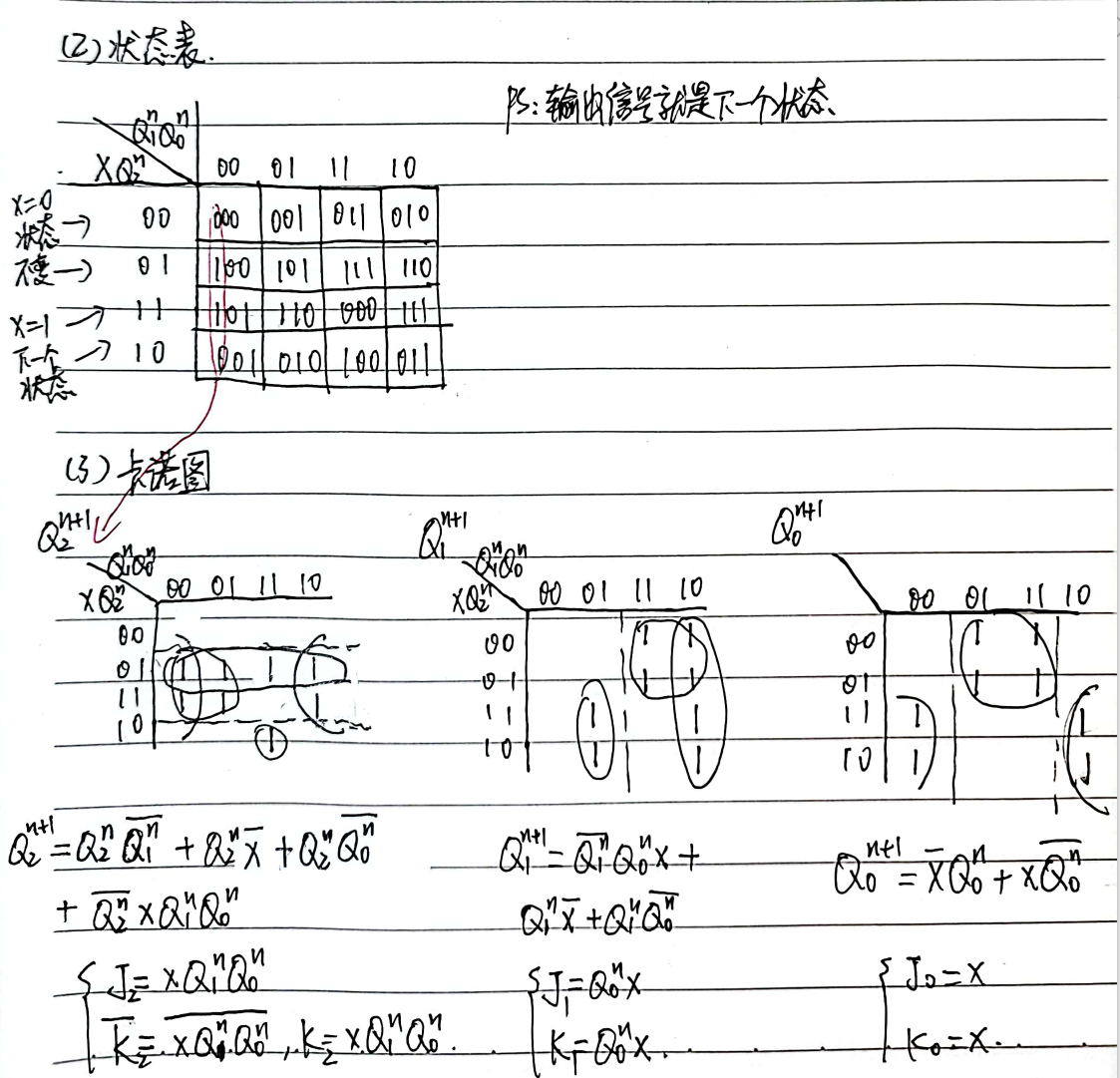

状态表和卡诺图:

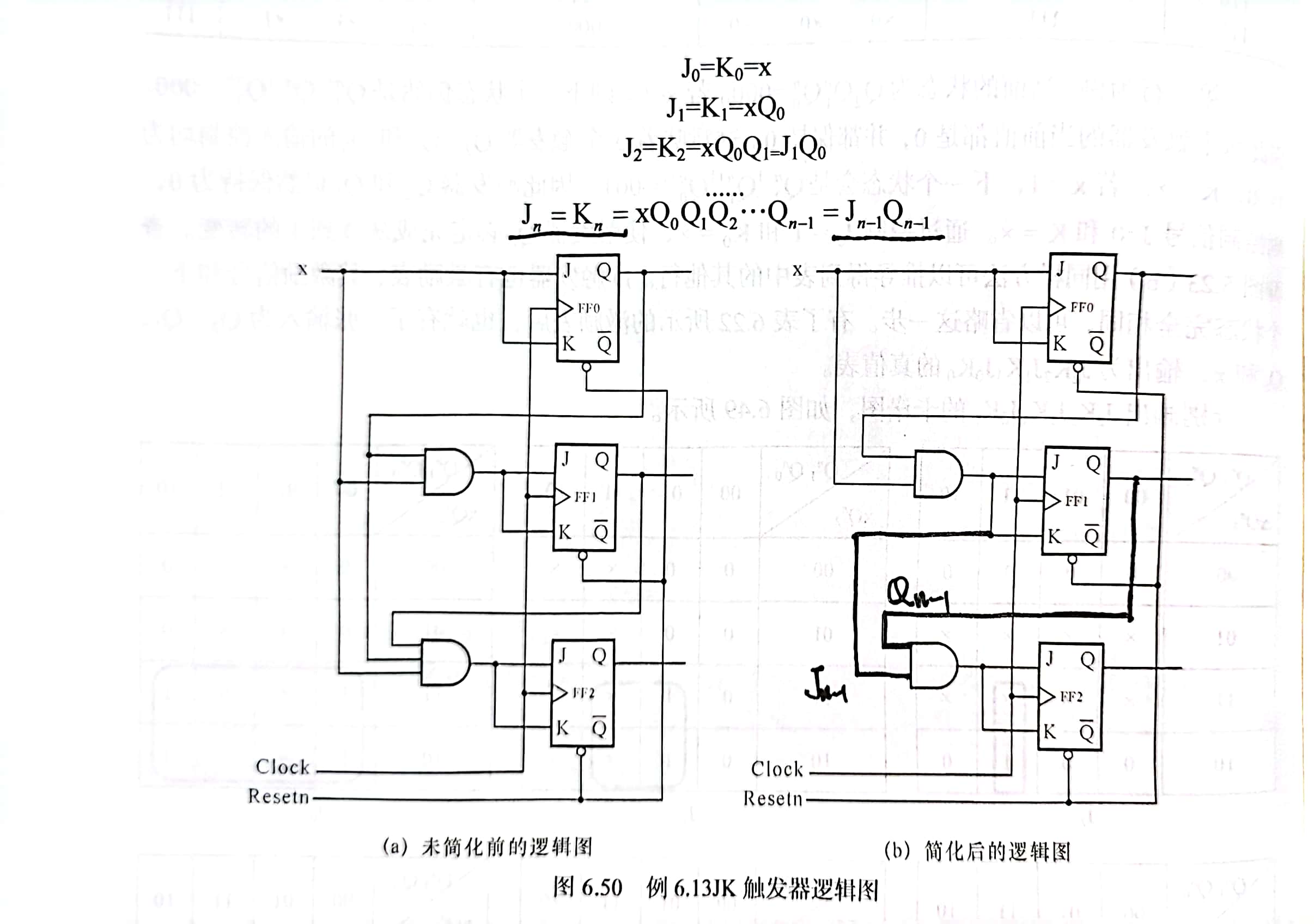

电路:

书上183页给出了用D触发器和JK触发器实现的方法

还有一道类似的例题【例6.14】在186页

还有试卷上的11题也是类似的计数器的时序逻辑电路设计

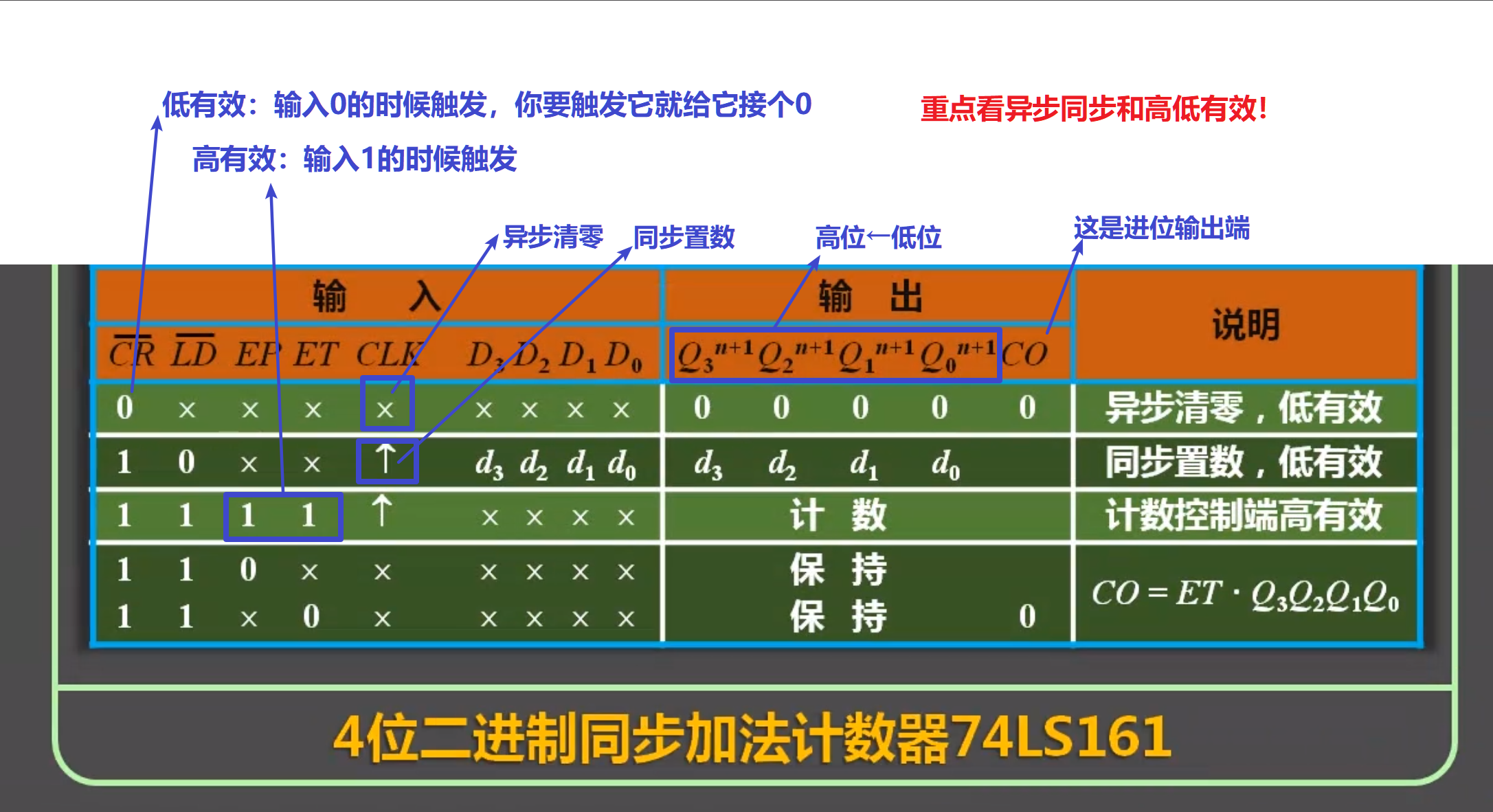

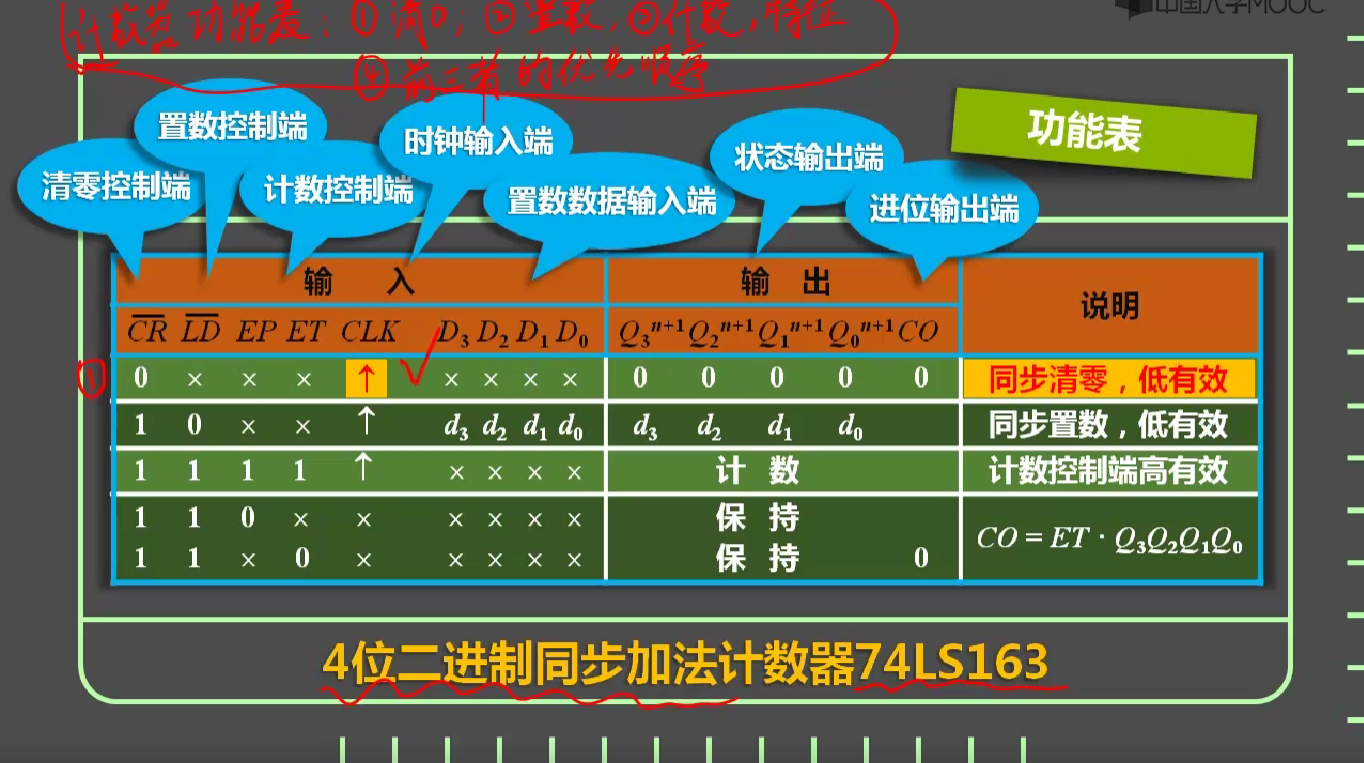

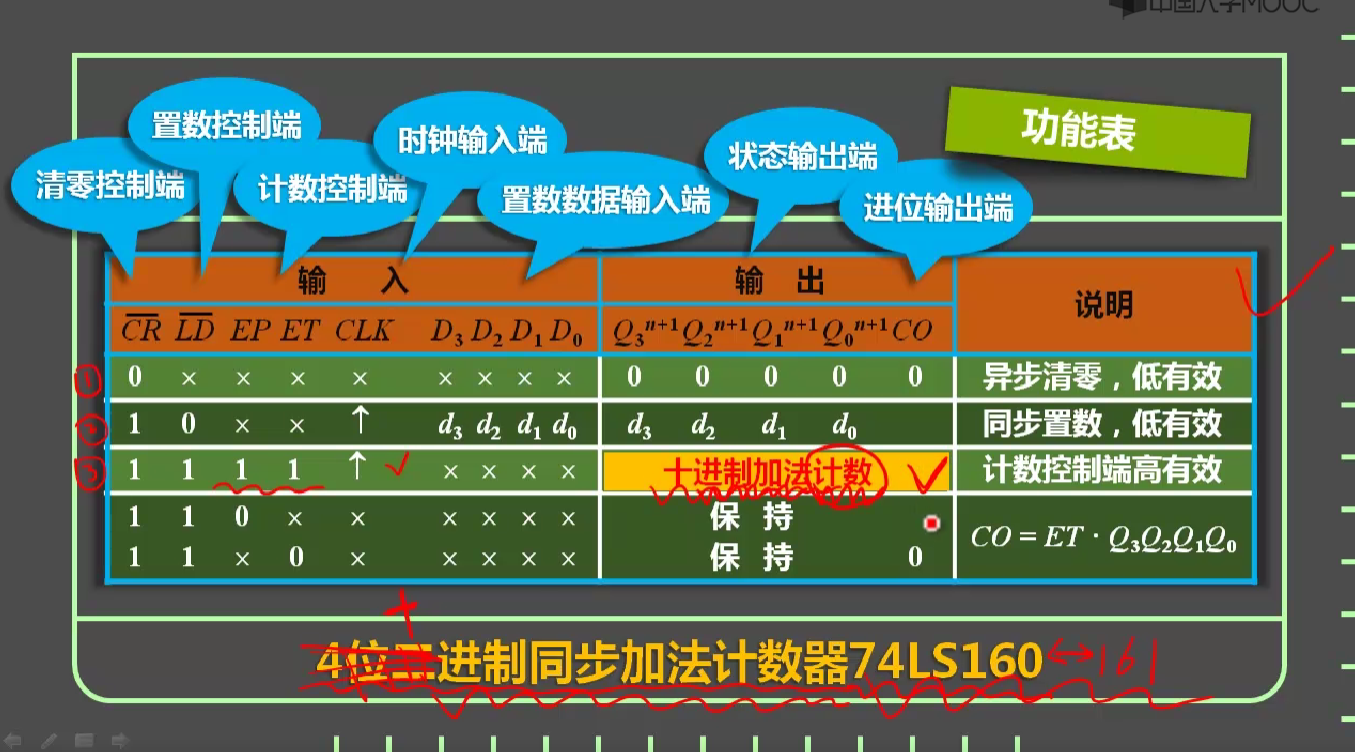

同步异步清零置数

异步计数器和同步计数器的具体介绍在书上的148页,关于同步和异步的区别在书上的150页。

这里直接概括:

异步:不用等clk,芯片的clk栏是x

同步:要等clk触发,芯片的clk栏是↑或者↓

例如异步清零就是不管clk是啥直接马上清零了,而同步置数就是要等clk上升沿到来时才会置数。因此如果要实现模6计数器(0~5),异步要检测6,同步要检测5。

清零:回到000

置数:可以不回到000(这个视频里有讲)

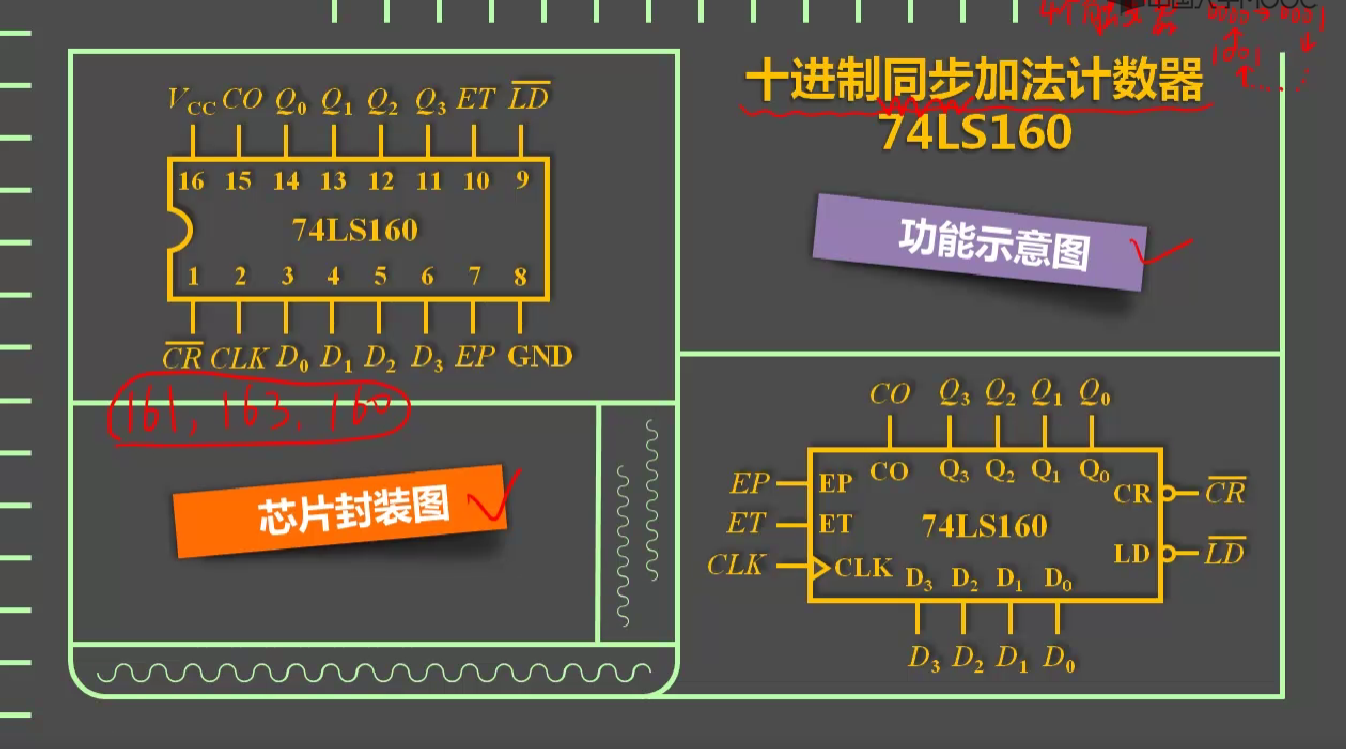

芯片

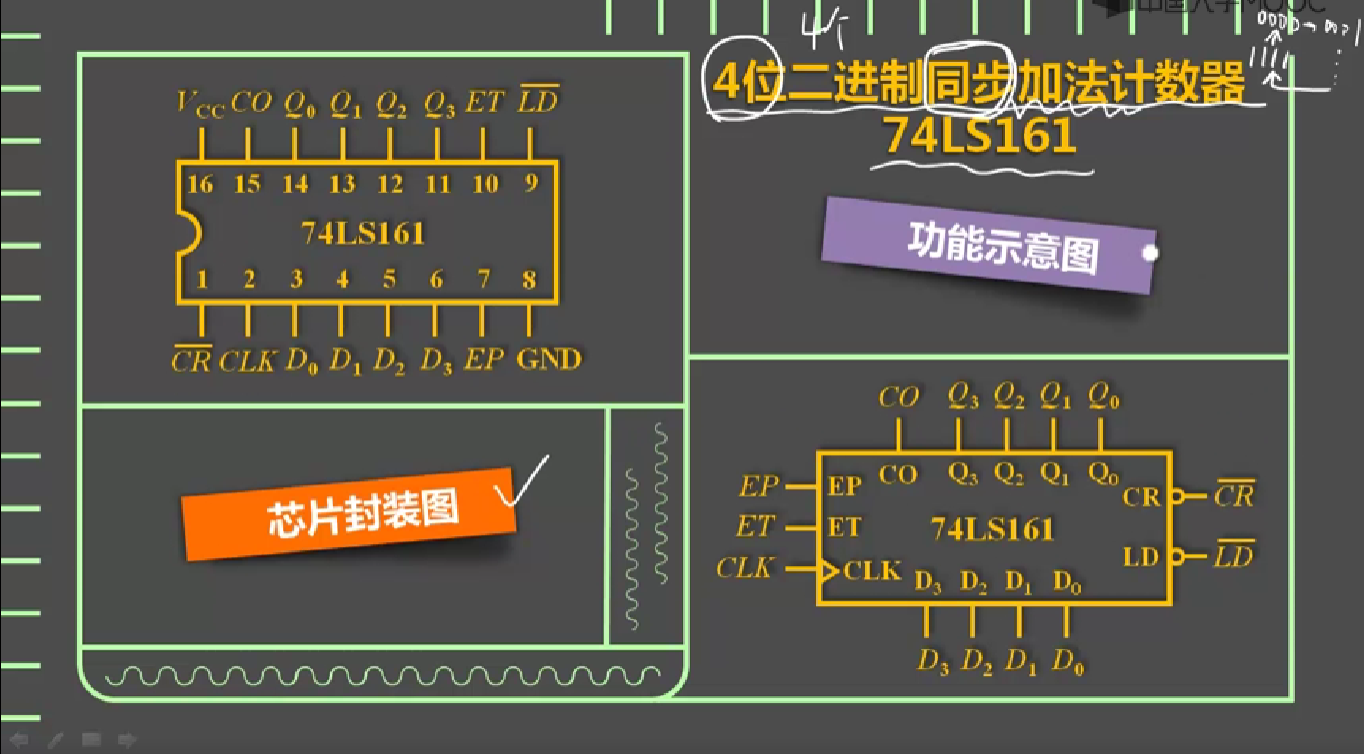

74161

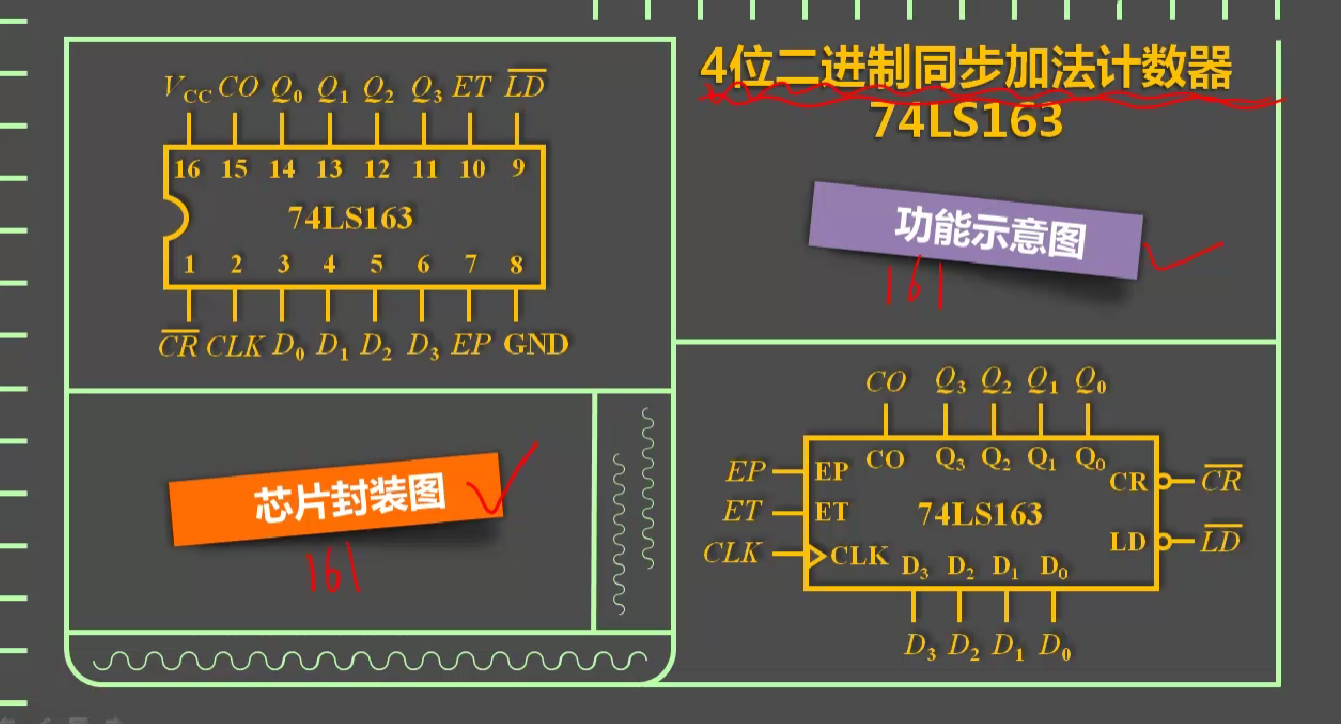

74163

74160

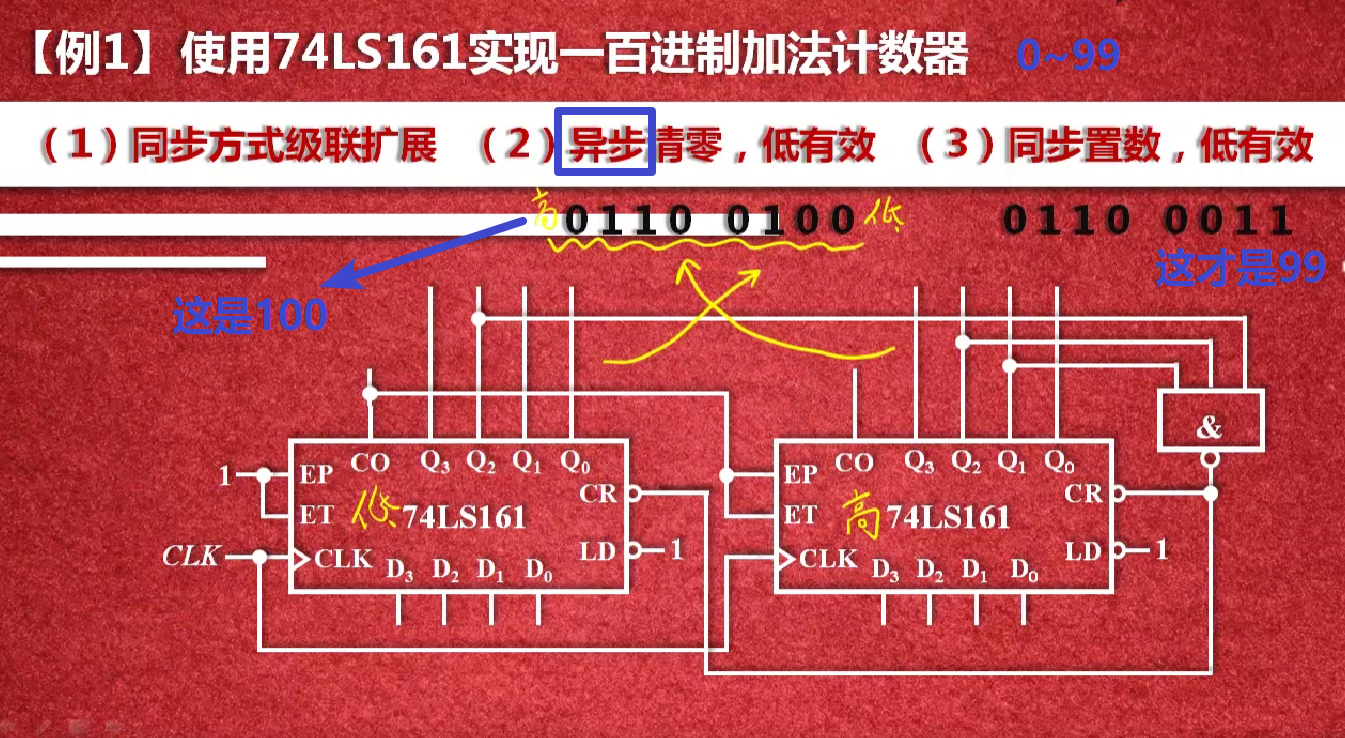

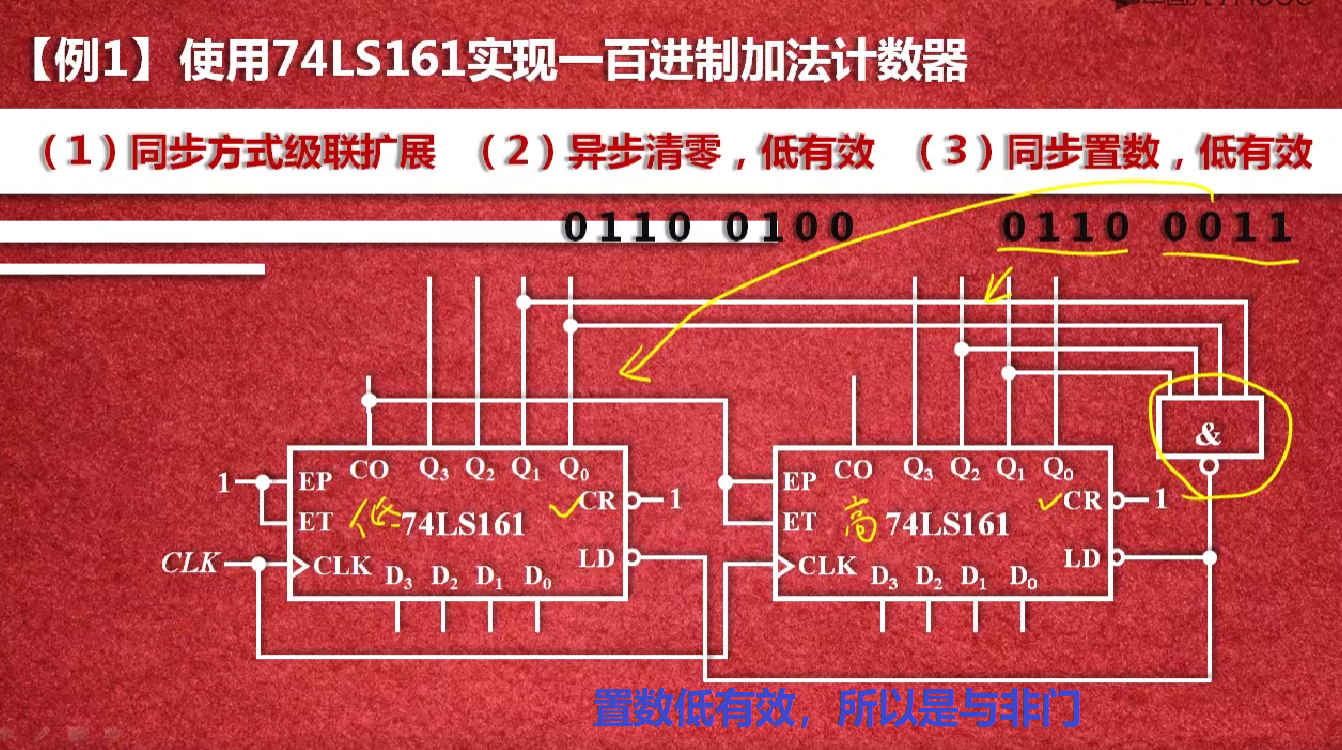

计数器的扩展

大模数→小模数

这个简单,你直接清零或置数就完事儿了。就是要注意是同步还是异步(例如模10,即0~9,同步要用输出9信号来清零,异步要用9的下一个信号来清零,你记着这个就行了)

小模数→大模数

这道题是卷子上的原题:

综合案例

我估计今年会考这个:

注意这是二进制计数器,不是BCD码

各种计数器

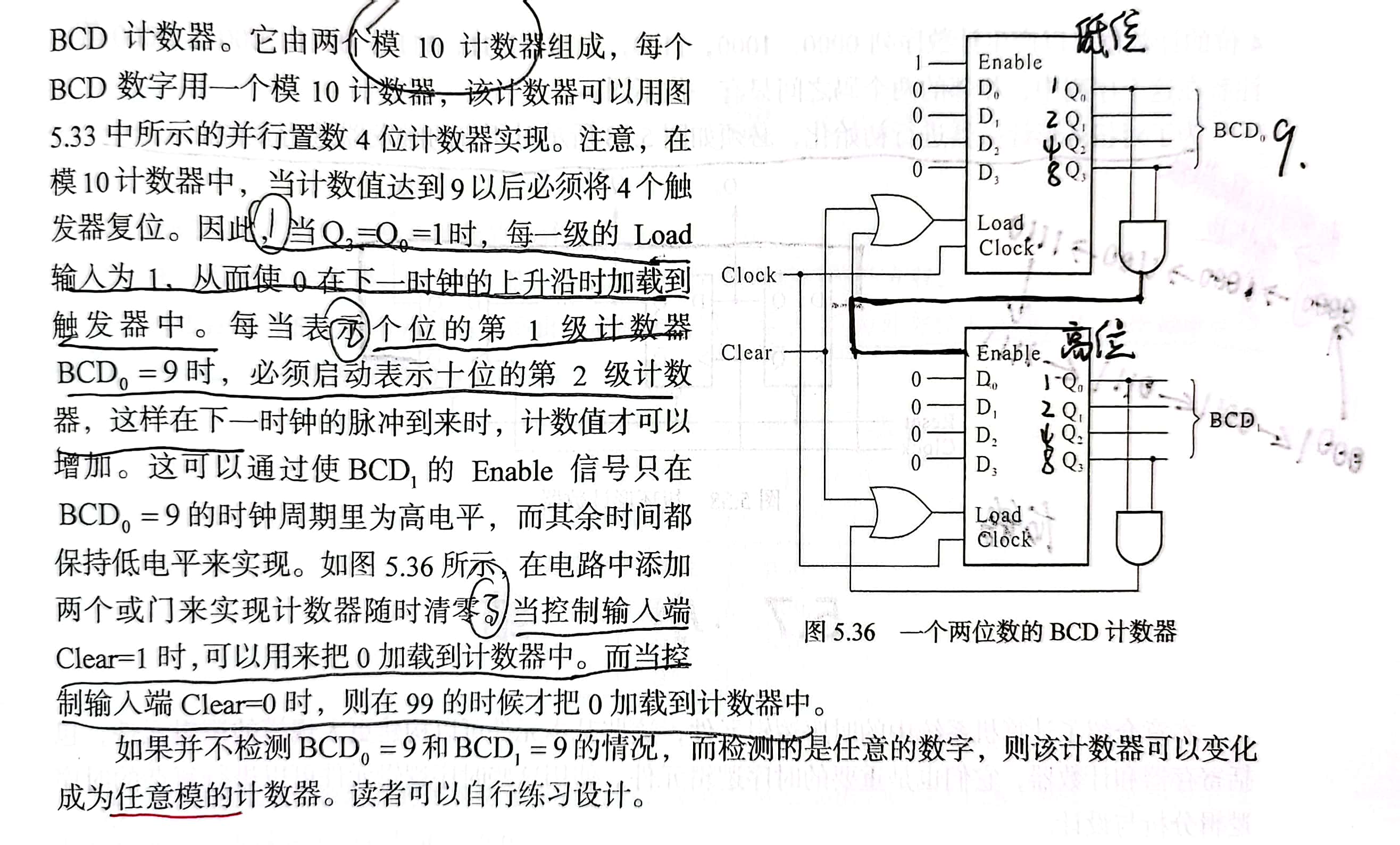

BCD计数器

环形计数器(寄存器型计数器)

扭环形计数器(寄存器型计数器)

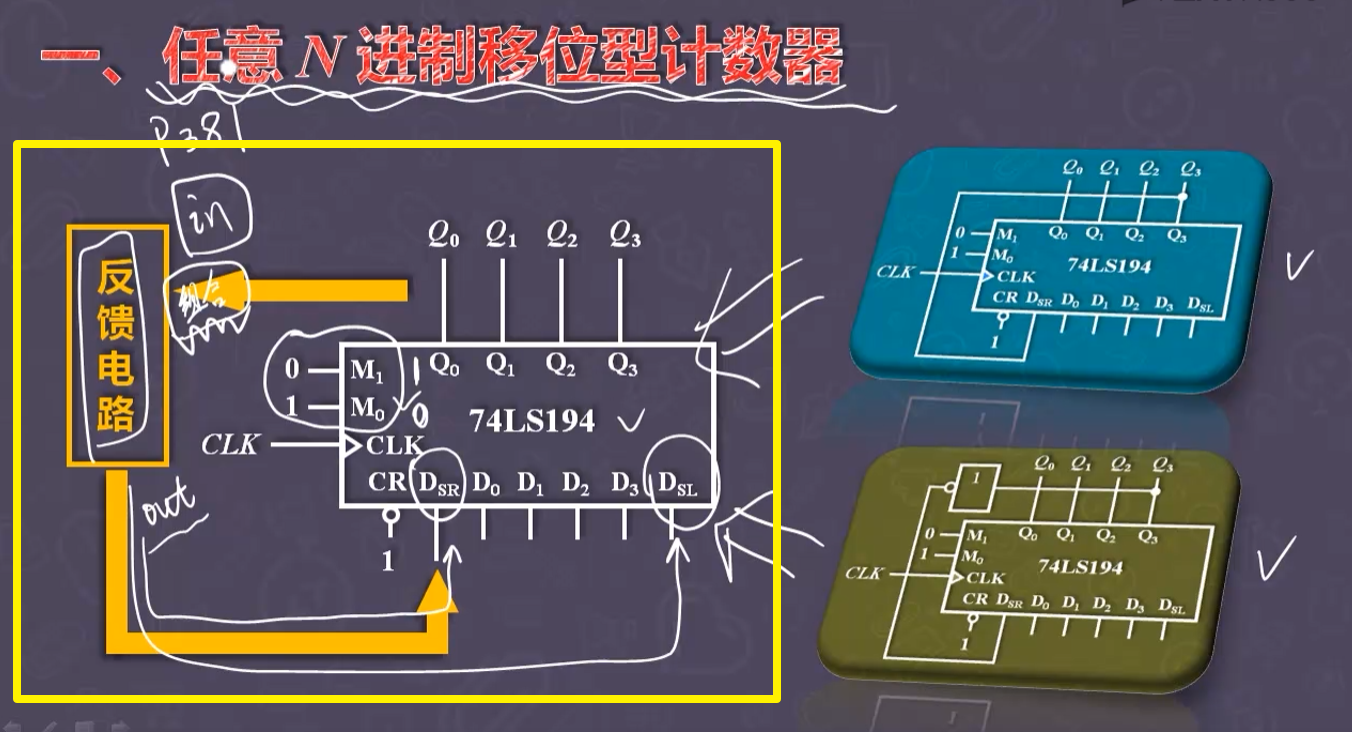

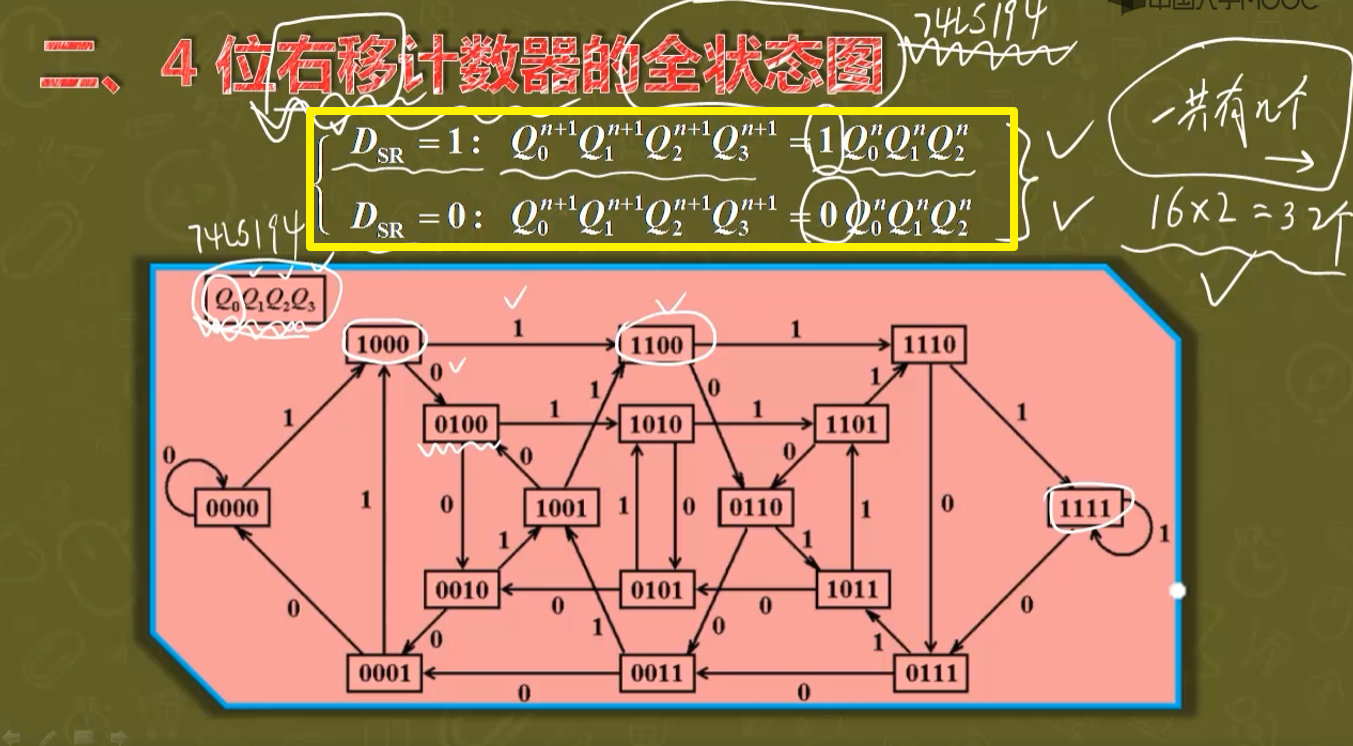

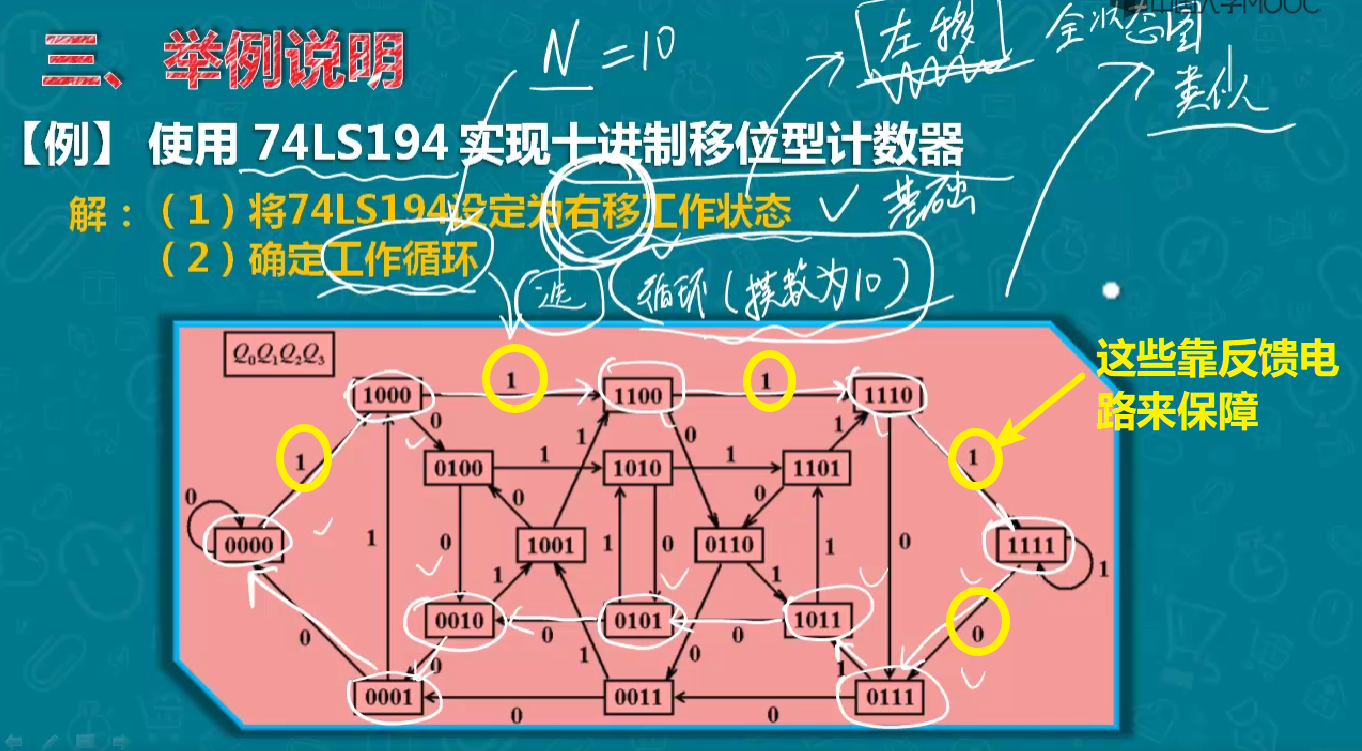

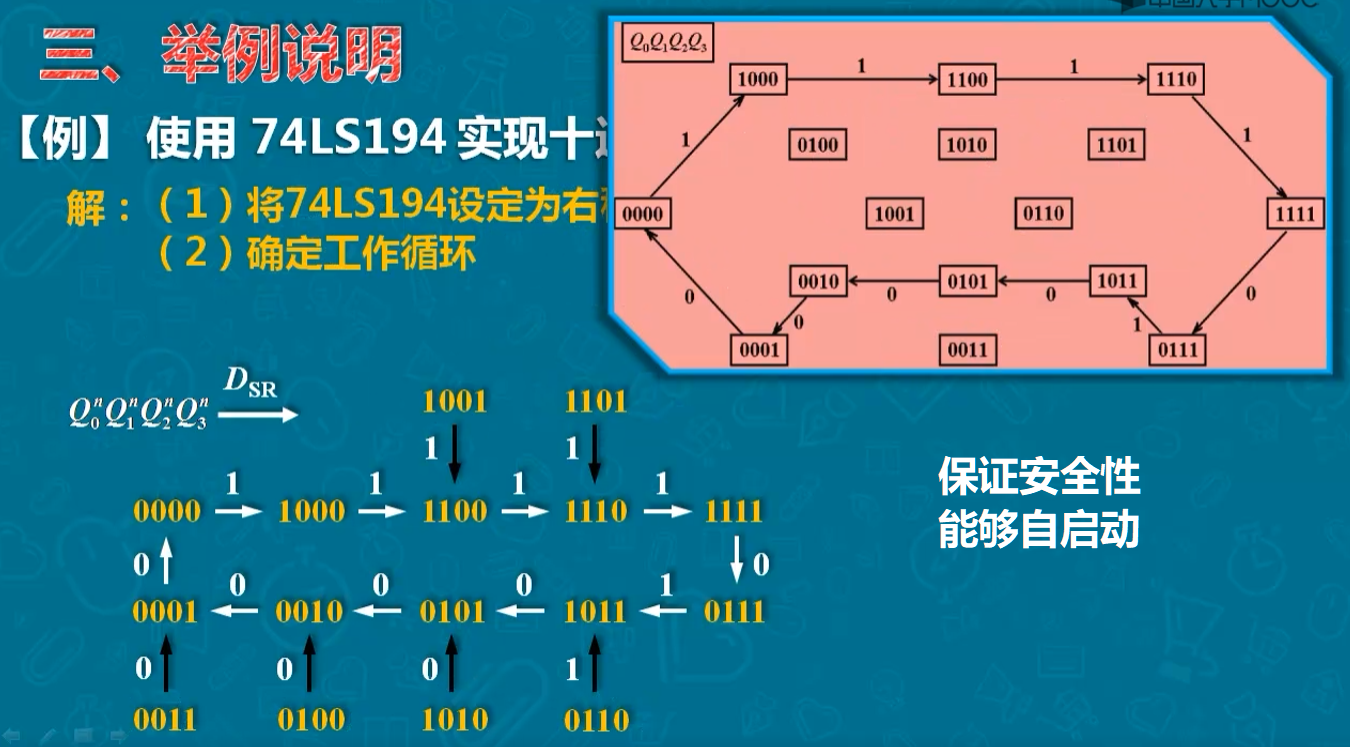

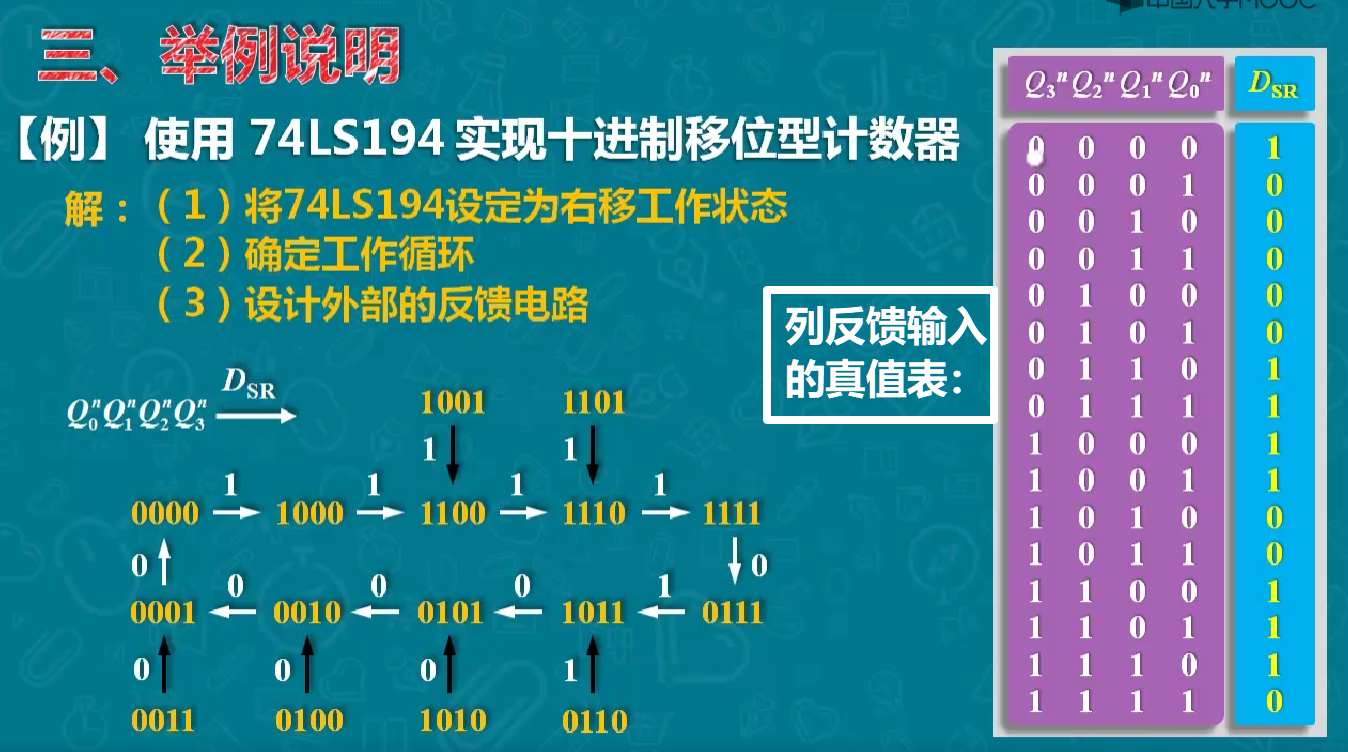

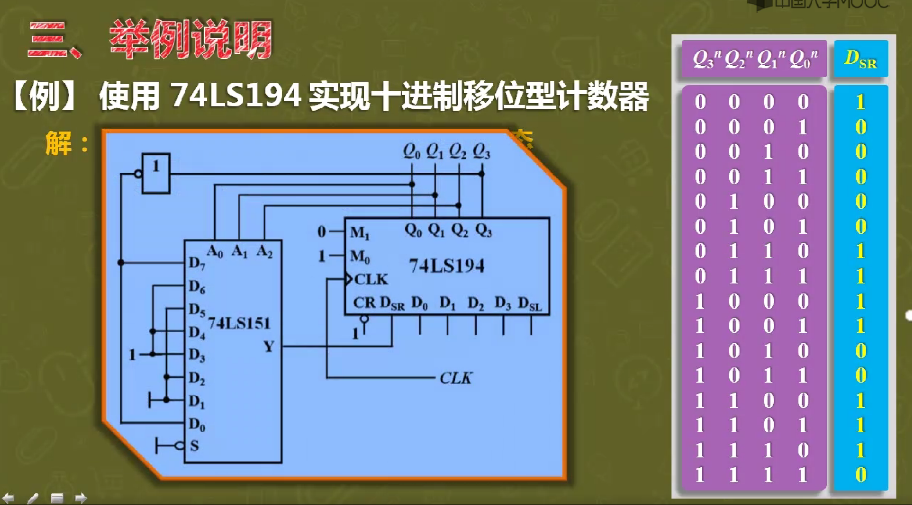

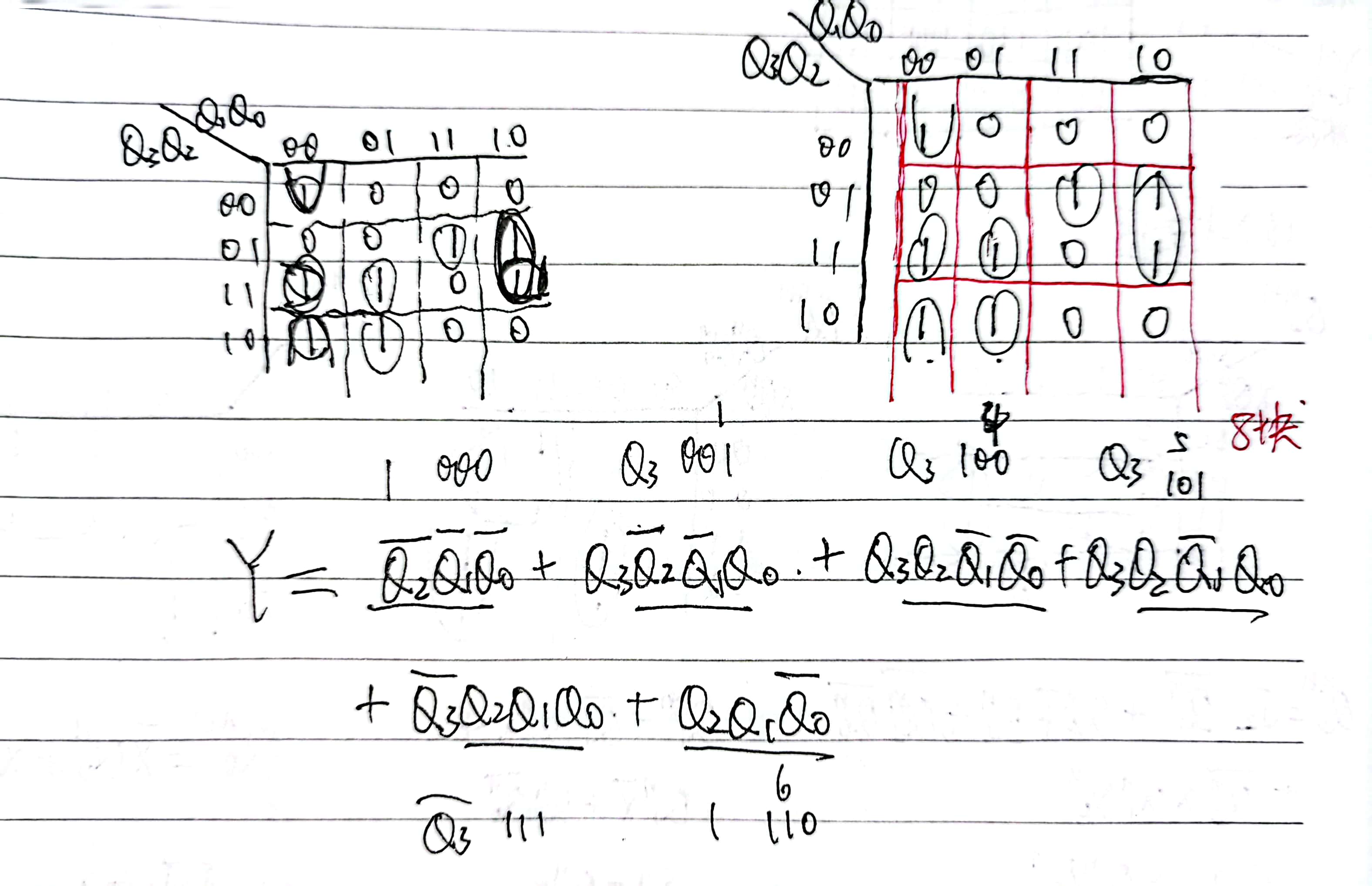

任意N进制移位型计数器(寄存器型计数器)

设计思路:

注意:他用八选一数据选择器搞的,他的真值表应该没错,但是电路图似乎不对:应该D0和D6接1,具体看下面

浙公网安备 33010602011771号

浙公网安备 33010602011771号