FPGA的模块

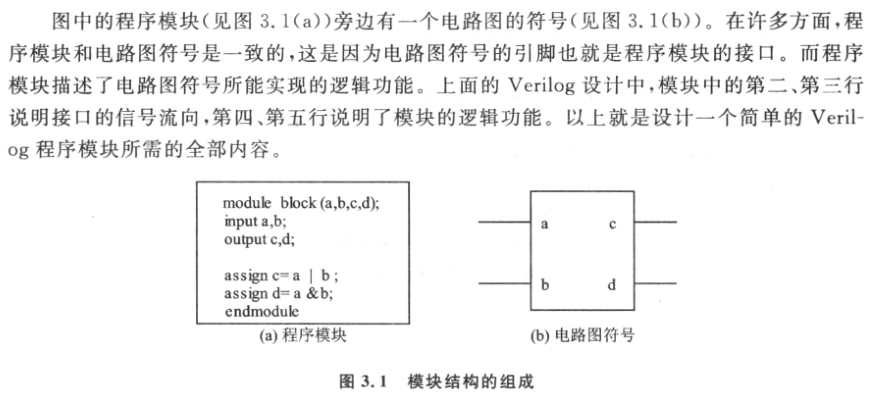

Verilog的基本设计单元是“模块”( block),一个模块是由两部分组成的。

一部分描述接口,另一部分描述逻辑功能即定义输入是如何影响输出的。

从这一例子可以看出, Verilog结构位于在 module和 endmodule声明语句之间,每个Verilog程序包括4个主要部分:端口定义、I/O说明、内部信号声明和功能定义。

module led (

input sys_clk,

input sys_rst_n,

output reg [2:0] led // 110 B, 101 R, 011 G 3个bit的变量,数据位宽3代表3个IO接口,最低位的IO是蓝灯...

);

reg [23:0] counter; // 24个bit的变量,用来存储时钟数目,计时用。不在led()内,不输出到IO。

//计数器对系统时钟计数,计时0.5秒

always @(posedge sys_clk or negedge sys_rst_n) begin

//posedge表示上升沿 ,negedge表示下降沿 ,条件触发。

if (!sys_rst_n)

//sys_rst_n 为复位状态,counter直接赋值为24个0【十进制的0】【变量是24位的】

counter <= 24'd0;

else if (counter < 24'd1200_0000) // 0.5s delay

counter <= counter + 1;

else

counter <= 24'd0;

//时间超过【24'd1200_0000】也要重新计数

end

//通过移位寄存器控制IO口的高低电平,从而改变LED的显示状态

always @(posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n)

led <= 3'b110; //复位的时候是蓝灯先亮

else if (counter == 24'd1200_0000) // 0.5s delay 时间到达的时候,改变灯的状态

led[2:0] <= {led[1:0],led[2]};

else

led <= led;

end

endmodule

程序解说:

https://www.cnblogs.com/tech-zyl/p/9879806.html

变量的几点:

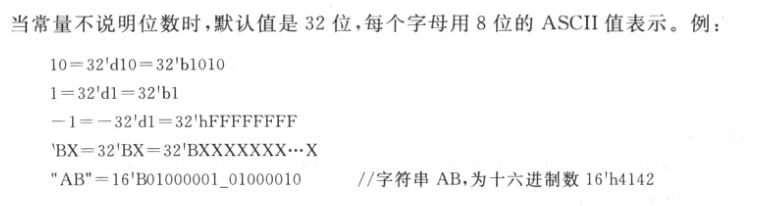

1、整数 【数据位宽 ,进制,数值】

2、x值【不确定】,z值【高阻态】

3、负数在最前加-号

4、数值可以用下划线增加阅读性

5、常量默认32位宽度。

https://bbs.elecfans.com/forum.php?mod=viewthread&page=1&tid=1117015

疑问

刚开始学习FPGA,还没从MCU的思想中走出来,总是觉得always中如果语句过多,会出现类似MCU中断中程序过多,超过中断时间导致程序混乱。大神们,always会出现这种现象吗?如果不会为什么不会呢?

解答

理论上不会,如果超过一个时钟的话,就是时序不满足了!这通过软件可以看出来,这就说明你的设计不科学了!

解答

always 不是中断,你这理解不对,always @ (posedge clk)是表示每个上升沿我要做的事!你写多少我都要做完,做不完就会出现时序问题了!这个综合结果可以看出来的!

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 10年+ .NET Coder 心语,封装的思维:从隐藏、稳定开始理解其本质意义

· .NET Core 中如何实现缓存的预热?

· 从 HTTP 原因短语缺失研究 HTTP/2 和 HTTP/3 的设计差异

· AI与.NET技术实操系列:向量存储与相似性搜索在 .NET 中的实现

· 基于Microsoft.Extensions.AI核心库实现RAG应用

· TypeScript + Deepseek 打造卜卦网站:技术与玄学的结合

· 阿里巴巴 QwQ-32B真的超越了 DeepSeek R-1吗?

· 【译】Visual Studio 中新的强大生产力特性

· 10年+ .NET Coder 心语 ── 封装的思维:从隐藏、稳定开始理解其本质意义

· 【设计模式】告别冗长if-else语句:使用策略模式优化代码结构