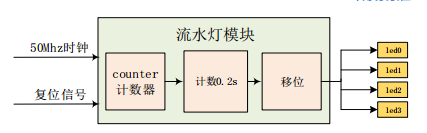

FPGA 流水灯实验

lesson 1 流水灯实验

1 module flow_led( 2 input sys_clk, //系统时钟50MHz 3 input rst_n, 4 5 output reg [3:0] led 6 7 ); 8 9 //reg define 10 /* 11 aim:解释为什么是24位的计数器 12 explain:因为系统时钟是50Mhz,所以计时周期是20ns,我们要实现延时0.2秒,则需要计时10^7个周期,10^7的二进制至少需要24位。 13 */ 14 reg [23:0] cnt; 15 16 17 //系统时钟,计数器计数,计时0.2s 18 always@(posedge sys_clk or negedge rst_n) 19 begin 20 if(!rst_n) 21 cnt <= 0; 22 else if(cnt < 24'd1000_0000)//计数满0.2S 23 cnt <= cnt + 1'b1; 24 else 25 cnt <= 24'd0; 26 end 27 28 //通过移位寄存器控制IO口的高低电平 29 always@(posedge sys_clk or negedge rst_n) 30 begin 31 if(!rst_n) 32 led <= 4'b0001; 33 else if(cnt == 24'd1000_0000) 34 led[3:0] <= {led[2:0],led[3]};//低三位拼接上高位,实现左移操作 35 else 36 led <= led; 37 38 end 39 40 endmodule

资料来源:新起点开发板

浙公网安备 33010602011771号

浙公网安备 33010602011771号