建立保持时间及违例解决方法 ------ 转载

转载自: 建立保持时间及违例解决方法 - 知乎 (zhihu.com)

建立保持时间概念

为什么要有建立保持时间?参考:为什么会有建立时间(setup time)和保持时间(hold time)要求 - 知乎 (zhihu.com)

答:简单来说,DFF可以由两个latch构成,每个latch是通过传输门组成的mux组成。如果不满足建立时间,mux反馈端口的左右两侧就会出现不相等情况。如果不满足保持时间,在clk关断mux之前,新的数据还是会进入dff冲毁数据。

- 建立时间(setup time):触发器在时钟沿到来之前,其数据的输入端的数据必须保持不变的时间;

- 建立时间决定了该触发器之间的组合逻辑的最大延迟maxdelays。

- 保持时间(hold time)触发器在时钟沿到来之后,其数据输入端的数据必须保持不变的时间;

- 关于保持时间的理解就是,在触发器D2的输入信号还处在保持时间的时候,如果触发器D1的输出已经通过组合逻辑到达D2的输入端的话,将会破坏D2本来应该保持的数据。

- 保持时间决定了该触发器之间的组合逻辑的最小延迟mindelays。

- Hold time violation的原因是前面输出变化太快,后端综合工具很容易自动解决这个问题(例如自动插入几个buffer)。

建立保持时间分析

参考:FPGA基础学习(5) -- 时序约束(实践篇) - 肉娃娃 - 博客园 (cnblogs.com)

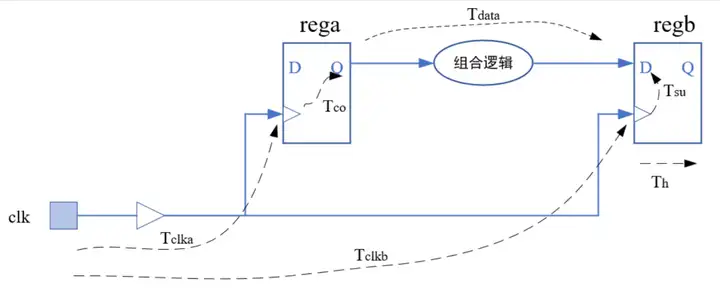

- 电路模型:

上图是典型的同步时序模型及其时序图,由发起寄存器(rega)、组合逻辑、捕获寄存器(regb)及其中间的走线组成。源时钟clk到达rega的时钟端口时,会有一定的延迟,从而形成clka。同理,时钟延迟到达regb的时钟端口,形成clkb。Tco为有效数据出现在发起寄存器Q端口所需时间。Tcomb为数据延迟,包括组合逻辑延迟和走线延迟。Tsu表示捕获寄存器建立时间要求。Th表示捕获寄存器保持时间要求。其中Tco、Tsu和Th是由FPGA的芯片工艺决定的。所以,我们所谓的时序约束,实际上就是对时钟延迟和Tcomb做一定的要求或者干预,其中Tcomb由组合逻辑(代码)及布局布线决定,这也决定了系统最高的工作频率。

- 裕量Time Slack:

时间裕量包括建立时间裕量和保持时间裕量(setup slack和hold slack)。从字面上理解,所谓“裕量”即富余的、多出的。什么意思呢?即保持最低要求的建立时间或保持时间所多出的时间,那么“裕量”越多就意味着时序约束越宽松呢。 - 如果Times Slack > 0 , 则电路能够正常被采样,否则不可以!

- 整个电路中,时钟频率由最差的一条时序路径决定!

- Setup Time公式:Tclka + Tco + Tcomb + Tsetupslack + Tsetup = Tcycle + Tclkb ,即Tsetupslack = Tcycle + (Tclkb-Tclka) - Tsetup - Tco - Tcomb。

其中Tclka和Tclkb是两个时钟偏斜,Tco是D->Q的传输延迟,Tcomb是组合逻辑延迟,Tcycle是时钟周期,Tsetup是建立时间,Tsetupslack是建立时间裕量。 - Hold Time公式:Tclka + Tco + Tcomb = Tclkb +Thold + Tholdslack,即Tholdslack = Tco + Tcomb - (Tclkb - Tclka) - Thold.

其中Tclka和Tclkb是两个时钟偏斜,Tco是D->Q的传输延迟,Tcomb是组合逻辑延迟,Thold是建立时间,Tholdslack是保持时间裕量。

通俗的讲,一个FPGA工程在综合实现后,是否满足时序约束,其实就是看所有的捕获寄存器是否能正确稳定捕获到发起寄存器发出的数据。如上图所示,也就是说到达捕获寄存器的数据输入端口D(regb/D)的数据要满足建立和保持时间要求,也就是说在Tsu之前,current data valid就要准备就绪,而在Th之后呢,current data valid还要多维持一段时间。换言之,在Tsu之前以及Th之后多出的这部分时间,我们就称之为“裕量”,裕量越大,时序越宽松。裕量的大小与时钟频率、代码设计以及布局布线有着紧密的联系。一个设计的时序报告中,裕量为负数时,表示时序约束出现违例,虽然个别违例不代表你的工程就有致命的问题,但是这是一个风险(时序报告是按照工艺、电压以及温度的上下限给出的结果)。当违例数较多,也就意味着设计在实际环境中出现问题的概率也会越大。

- 最大延迟和最小延迟:

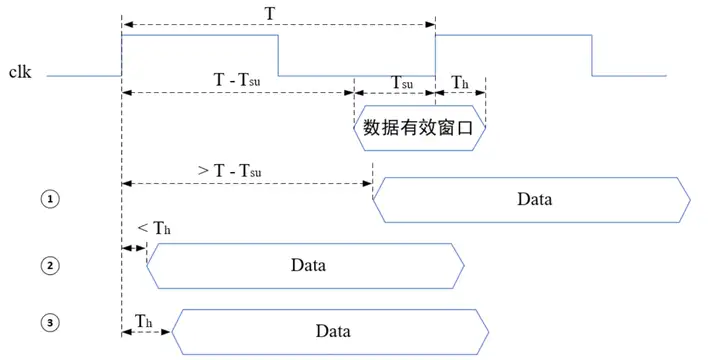

如下图所示,“数据有效窗口”表示捕获的数据满足建立时间和保持时间,在此窗口中要捕获的数据不能发生变化,否则将引起不稳定的结果。

我们来看1、2、3三种情况,在分析之前,首先要明确Data的持续时间长度一定是一个时钟周期(多周期打拍另说)。1:当延迟时间大于T-Tsu时,Data在建立时间区域内才到达regb,所以不满足建立时间要求,这就是说数据来的“太晚了”;2:当Data延迟了很小一段时间(<Th),Data在保持时间内就变化了,所以不满足保持时间,这就是说数据来的“太早了”。3:当Data延迟了Th,Data则满足建立时间要求又刚好满足保持时间要求,这就是说数据来的“正巧”。

综上所述,数据的最大延迟是T-Tsu,最小延迟是Th。

一般而言,在综合之后,我们需要特别关注的是建立时间的时序违例,因为可以通过增加布线长度来保证保持时间。大多数保持时间违例在实现之后自然会被优化掉。

Setup Time Violation的解决方案

- Setup时间公式:Tclka + Tco + Tcomb + Tslack + Tsetup = Tcycle + Tclkb,即Tslack = Tcycle + Tclkb - Tsetup -Tclka - Tco - Tcomb

其中Tclka和Tclkb是两个时钟偏斜,Tco是D->Q的传输延迟,Tcomb是组合逻辑延迟,Tcycle是时钟周期,Tsetup是建立时间,Tslack是建立时间裕量。

如果出现了Setup Time Violation,也就是说Tsetupslack为负数了,那么可以考虑: - 增大时钟周期Tcycle,即降低时钟频率

- 减小 D->Q的传输延迟Tco,即更换更快的器件,使用更先进的器件库

- 减小 Tcomb,即减小组合逻辑延时,主要是关键路径的处理。包括插入寄存器使其流水、重定时等。

- 增大时钟歪斜Tskew=Tclkb-Tclka。如果时钟歪斜 Tskew 为正,对setup是有利的,对hold是有害。

Hold Time Violation的解决方案

- Hold Time公式:Tclka + Tco + Tcomb = Tclkb +Thold + Tholdslack,即Tholdslack = Tco + Tcomb - (Tclkb - Tclka) - Thold.

其中Tclka和Tclkb是两个时钟偏斜,Tco是D->Q的传输延迟,Tcomb是组合逻辑延迟,Thold是建立时间,Tholdslack是保持时间裕量。

如果出现了Hold Time Violation,也就是说Tholdslack为负数了,那么可以考虑: - 增加 Tcomb 延迟,增大数据的延迟具体表现为插入 Buffer,Xilinx 还提到可以插入 LUT1 增加延迟等方式来修复;

- 增大 Tcomb,即增大组合逻辑延时,主要是关键路径的处理。可以增加Buffer,或者后端布局布线拉长布线以增加延时。

- 减小时钟歪斜Tskew=Tclkb-Tclka。如果时钟歪斜 Tskew 为正,对setup是有利的,对hold是有害。

浙公网安备 33010602011771号

浙公网安备 33010602011771号