Spyglass CDC工具使用(三)

最近一直在搞CDC (clock domain crossing) 方面的事情,现在就CDC的一些知识点进行总结。

做CDC检查使用的是Spyglass工具。以下内容转载自:Spyglass之CDC检查(3) - 代码先锋网 (codeleading.com)

文章目录

- Clock_info03a

- Clock_info05a/b

- Clock_info18

本篇文章主要介绍CDC检查第二个过程CDC_setup_check,有Clock_info03a, Clock_info05a/b以及Clock_info18检查项

Clock_info03a

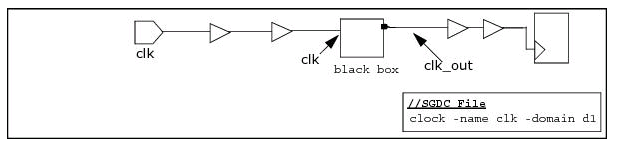

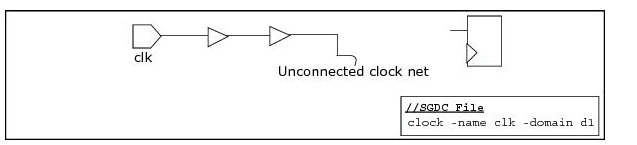

报告设计中未被约束的时钟引脚,以下几种情况会报违例。

- 时钟经过组合逻辑后被disable

- 约束文件中没有约束时钟引脚,且use_inferred_clocks参数被设置为No

- 时钟路径上有Blackbox,且Blackbox输出的时钟未约束

- 时钟在设计中没有传输

Clock_info05a/b

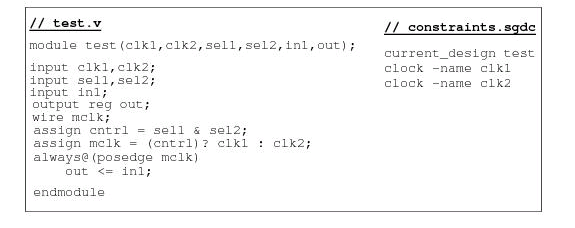

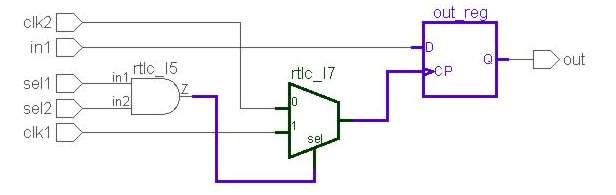

如果设计中有多个时钟经过选择器,则需要通过set_case_analysis命令来约束。

在上面的例子中,有clk1和clk2两个输入时钟,经过选择器后输出一个时钟。如果不对选择器进行约束,就会报违例,可将约束文件修改为:

clock -name clk1 clock -name clk2 set_case_analysis -name sel1 -value 0 set_case_analysis -name sel0 -value 0

Clock_info18

报告设计中未约束的引脚。

约束文件中一定要约束以下引脚:输入引脚(包括时钟,复位信号),输出引脚以及BLACKBOX的引脚。

- 对于顶层的输入输出引脚,可在约束文件中通过以下命令约束:input,output,clock,reset,set_case_analysis,abstract_port。

- 对于BLACKBOX的引脚可通过以下命令约束:clock,reset,abstract_port,assume_path以及signal_in_domain。

以上命令如何使用,可查阅spyglass help文档仔细阅读。

浙公网安备 33010602011771号

浙公网安备 33010602011771号