chipyard——自定义配置生成和前仿

一,生成配置

前面用rocket-chip仓库做了生成和前仿,为了方便扩展外设,这里转到chipyard仓库。

首先我们生成一个之前用的配置:

为删SimDTM(我的测试框架不需要),先在rocket的subsystem/config下创建一个class:

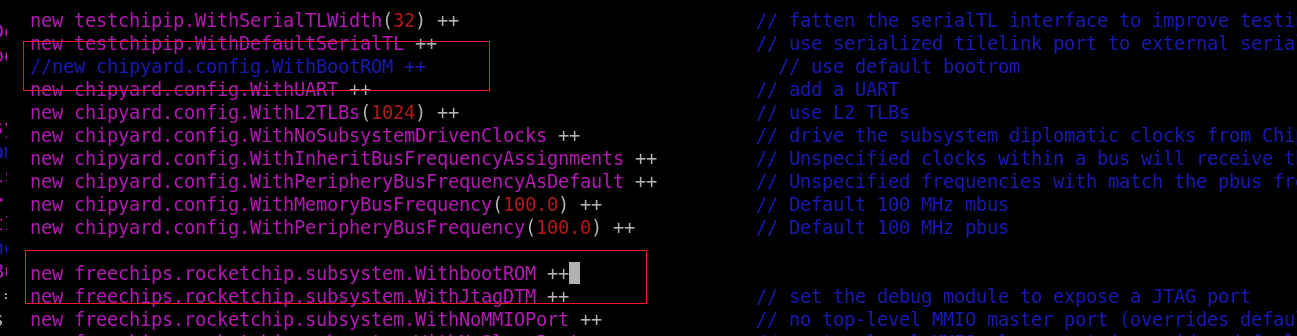

然后在chipyard顶层创建config:

make CONFIG=MyConfig创建设计

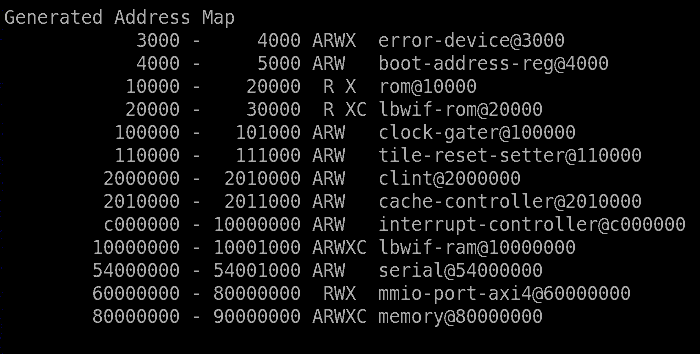

发现少了Simmmio接口(这也正常,最终的soc该接口都表现为各种外设),bootrom里固化的值不对

在rocket/subsystem下写一个新的bootrom config:

在/generators/chipyard/src/main/scala/config/AbstractConfig.scala 下替换成原本的rocket bootrom

在vcs目录下执行:

make verilog CONFIG=MyConfig

修改后可以看到TLROM里的内容正常了:

不过这样顶层的mmio接口没了,为了方便dump仿真波形也许还需要暴露出一个mmio接口在testharness里接Simmem。

二,扩展外设

之前分享过如何集成新外设,这里我们加入一些常见的外设,看看fragments/PeripheralFragments.scala中目前支持什么外设:

address 0x10012000的GPIO

address 0x5400000L的UART

address 0x10040000的spi

这三种外设的IO相关接口也都写好了,我们除了在顶层添加以外无需修改Chiptop和Testharness:

下面写一个新的配置来集成这些外设:

值得注意的是在abstractConfig中已经有了UART,因此我们不用加了

可以在顶层看到IO:

三,前仿

前面说到,我所搭建的VCS测试框架本质是依靠hex仿真结束后向mmio地址空间写一个magic word来确保程序执行完毕,因此我们最好在Chiptop上也暴露一片地址空间的mmio接口,在testharness中同样连接到SimAXImem上,这样理论上chipyard生成的soc也可以用我们的测试框架来做指令集前仿。

注意到config内有两个这样的配置:

一个暴露出memport接口,一个暴露出mmioport接口,写一个如下config来看看接口特性:

只不过接口命名和rocket仓库的不一样了,注意在测试框架中修改。

加上外设后:

前仿需要的文件有:

harness.v(包含测试模块的顶层),top.v(soc顶层),harness.mems.v(包含用于仿真的行为级mem),top.mems.v(soc内部用的mem),analog.v(提供恒定输出的仿真模块,输给soc外设接口的),IOcell.v(soc的IO单元),SPIFlashMemCtrl.sv和SimSPIFlashModel.sv是harness内仿真spi相关单元,SimSerial.v也是仿真模块,在我们的仿真逻辑中暂且不用,SimUART.v接soc uart的仿真模块,此外testdriver.v是官方用于仿真的顶层bench,我们自己写了testbench就不用这个了(我对官方的仿真逻辑暂时还没理解)。

修改filelist.f:

修改top.v,首先是readmemh,testharness内有三块mem(mem_ext,mem_0_ext,mem_1_ext),三者的例化关系是:

mem_ext——mem_inTestHarness——TLRAM_inTestHarness——SerialRAM_inTestHarness——TestHarness(暂不清楚是干什么的)

mem_0_ext——mem_0_inTestHarness——AXI4RAM_inTestHarness——SimAXIMem_inTestHarness——TestHarnsee (用于mmio的mem)

mem_1_exit —— mem_1_inTestHarness——AXI4RAM_1_inTestHarness——SimAXIMem_1_inTestHarness——TestHarness (用于sram的mem)

在behav.ram内这三块ram被分成了spilt_ram,不好进行赋值,但接口和rocket生成的行为级sram是相同的,我们在这里对其进行替换,换成一整块sram,将rocket内生成的mem_ext替换到chipyard mem_1_ext。将mem_0_ext替换到mem_0_ext

最后只需要将原先的mem_ext改为mem_1_ext即可

magic word信号的获取,在hex最后向mmio地址空间写一个数据,我们在axi总线上wait相应的数据,以此判断仿真是否结束:

值得注意的是官方写了很多仿真模块,我暂时还没有去看如何运用,在目前的仿真框架下需要对这些仿真模块做一些修改,否则仿真会报错,经过修改最终成功测试hex:

浙公网安备 33010602011771号

浙公网安备 33010602011771号