Rocket——外设扩展

之前曾分享过如何基于cake pattern在chipyard中添加自定义MMIO外设和ROCC加速器,那么如何在Rocket上添加GPIO,SPI,UART,I2C这些常规外设呢?用chipyard和rocket-chip哪个更方便呢?是时候做个总结了。

一,Rocket-chip 扩展外设

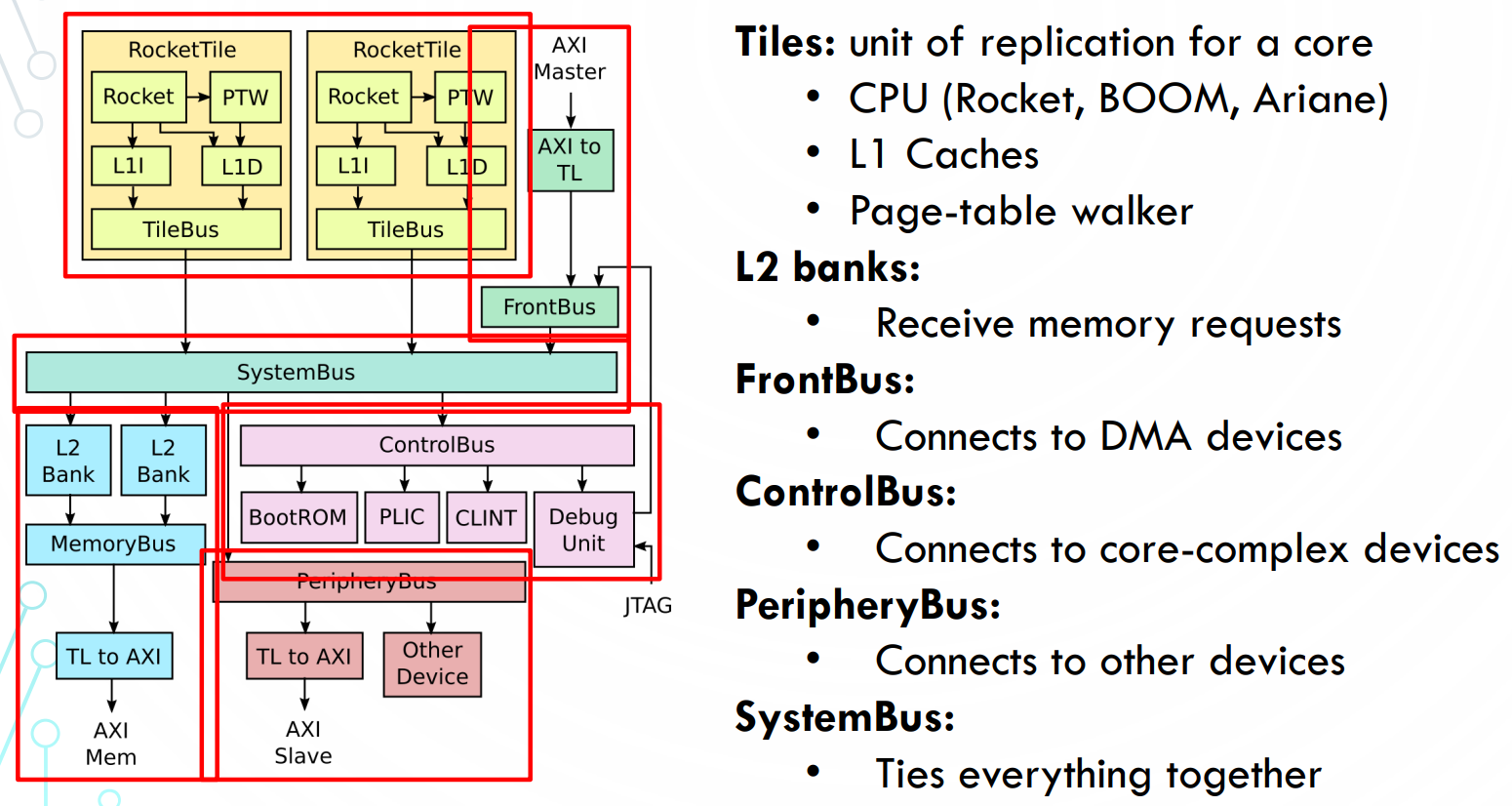

1,首先简单介绍下rocket架构

- Tile:一个单核系统,内部包含Rocket core,PTW,L1D,L1l,也可以包含自定义ROCC模块

- L2bank:接收一级缓存数据和指令,介于一级缓存和主存之间

- systembus:tilelink系统总线

- memorybus:连接多个L2bank和TL2AXI接口

- controlbus:用于连接bootrom,plic等控制模块

- peripheryBus:连接其他通用外设

- frontbus:用于连接DMA设备

rocket仓库下没有自带外设,需要重新写外设config在顶层继承。那么rocket中如何扩展外设呢?

2,rocket扩展外设

参照sifive/freedom: Source files for SiFive's Freedom platforms (github.com)

ucb-bar/chipyard at a3684d01dd57b871dc8f98e8f51e1907339bc179 (github.com)

搭建sifive+rocket-chip的外设扩展平台(即简化版chipyard,毕竟chipyard很多东西不需要,且更新频繁)

二,利用chipyard扩展外设

可以看到chipyard/generator中包含rocket-chip和sifive-blocks,在/root/chipyard/generators/chipyard/src/main/scala/config/fragment中有外设模块接口

在RocketConfigs.scala中有对应的config:

sifive支持的外设有:

1,以集成GPIO为例

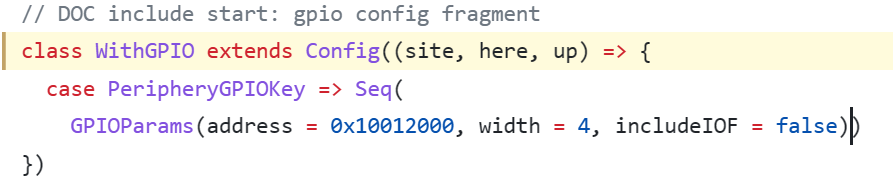

To integrate one of these devices in your SoC, you will need to define a custom config fragment with the approriate address for the device using the Rocket Chip parameter system.

(1)首先在chipyard/generators/chipyard/src/main/scala/config/fragments/PeripheralFragments.scala添加对应外设的地址映射配置项:

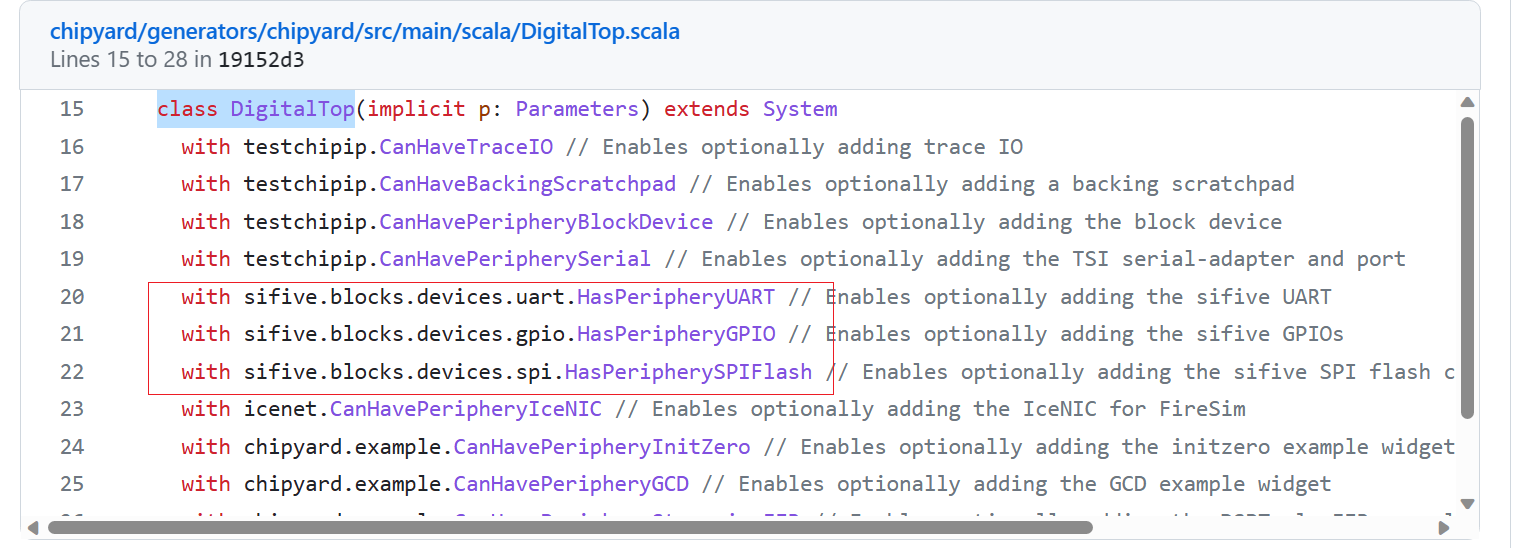

(2)在chipyard/generators/chipyard/src/main/scala/DigitalTop.scala下class DigitalTop添加外设配置项

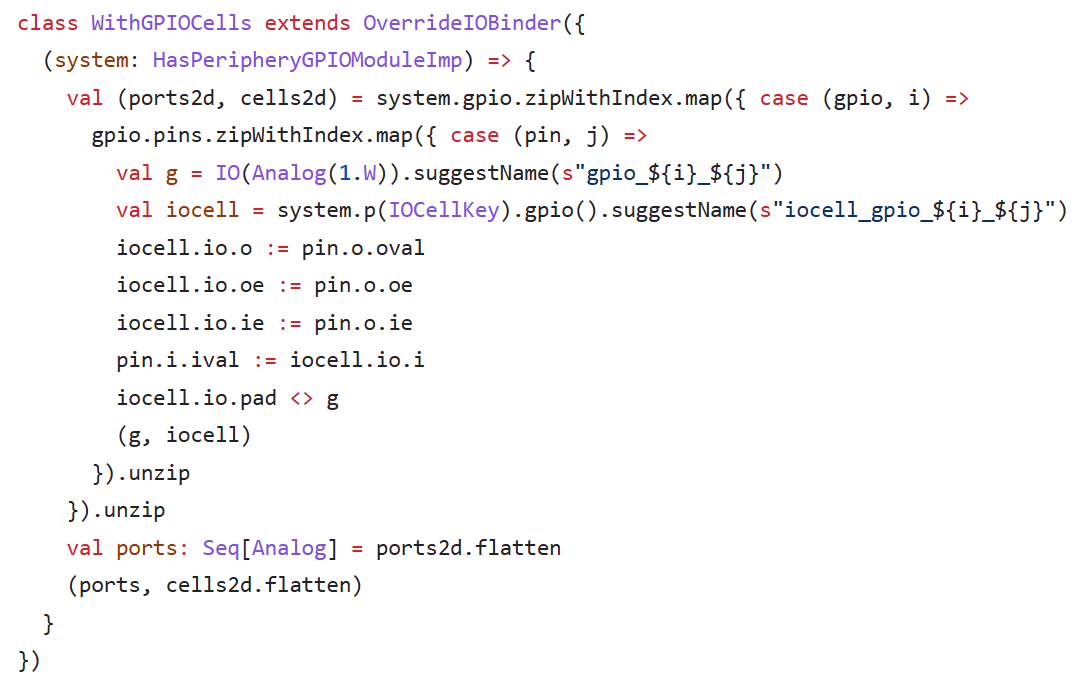

(3)在IOBinders and HarnessBinders创建IO接口

The

IOBinderfunctions are responsible for instantiating IO cells and IOPorts in theChipToplayer.For example, the

WithUARTIOCellsIOBinder will, for anySystemthat might have UART ports (HasPeripheryUARTModuleImp, generate ports within theChipTop(ports) as well as IOCells with the appropriate type and direction (cells2d). This function returns a the list of generated ports, and the list of generated IOCells. The list of generated ports is passed to theHarnessBinderssuch that they can be connected toTestHarnessdevices.

The

HarnessBinderfunctions determine what modules to bind to the IOs of aChipTopin theTestHarness. TheHarnessBinderinterface is designed to be reused across various simulation/implementation modes,用于决定哪些接口连接到testharness

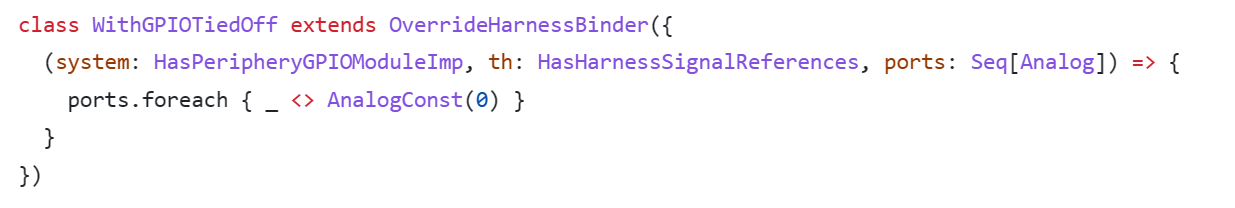

This example instantiates a top-level module with include GPIO ports, and then ties-off the GPIO port inputs to 0 (false.B).这里让top接口的gpio信号在testharness中都接0

(4)最后创建对应的config配置用于编译

浙公网安备 33010602011771号

浙公网安备 33010602011771号