后端基础——虚拟时钟

导言:根据定义,虚拟时钟是没有时钟源的时钟,也就是说虚拟时钟是被定义的,但未与任何引脚(pin)/端口(port)关联的时钟。虚拟时钟用作设置input delay/output delay的参考(reference)。

STA有四种时序路径,分别是:in2reg,reg2reg,reg2out和in2out,其中三种都与input或output port相关,而工具并不知道input port和output port外部延时,所以需要对其加以约束。

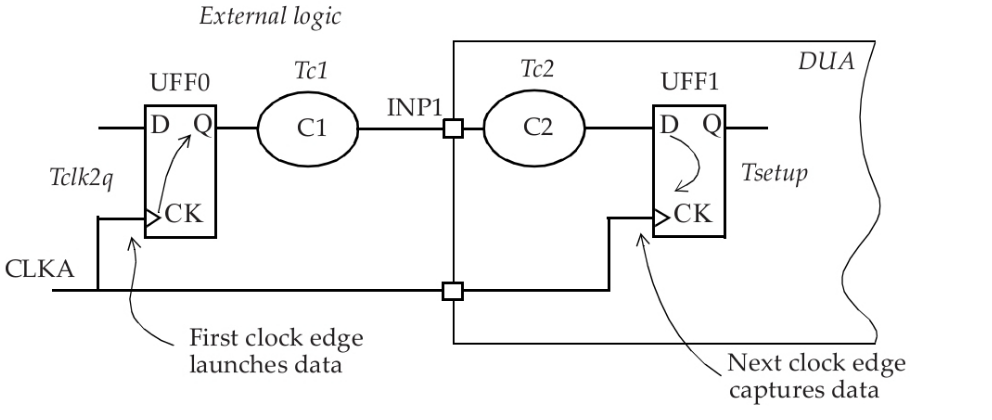

后端时序分析时,我们把四种时序路径都当做reg2reg来分析,以in2reg为例,如下图,我们在block外假设一个虚拟的寄存器UFF0。

现在INP1 to UFF1的path就变成了UFF0 to UFF1了,只需要设置好外部延迟即可,设置方式如下:

set_input_delay -max (Tclk2q+Tc1) [get_ports INP1] -clock [get_clocks $CLK]

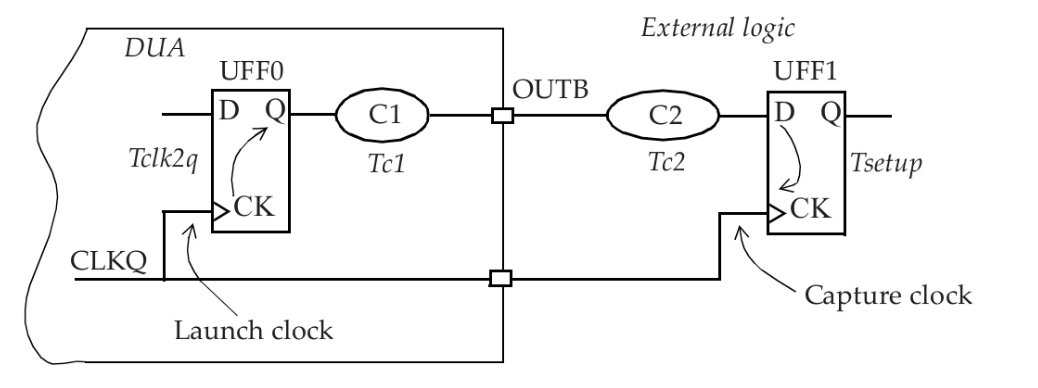

同理,如果是reg2out,就可以在output port后假定一个虚拟寄存器:

set_output_delay -max (Tc2 + Tsetup) [get_ports OUTB] -clock [get_clocks $CLK]

通常RTL设计要求对时序收敛留下足够裕量,综合阶段可根据设计工艺需求,设置IO的input/output为时钟周期的40%-60%。但是,芯片timing sign-off阶段会偶尔遇到IO时序少量违例,比如,输入reg的hold违例、输出reg的setup违例,本质原因是EDA时序分析工具会在输出输入外部假定一个理想化的不带clock propagation time的寄存器做时序分析,在CTS后,实际的clk会带有clock latency。如果设置input / output delay的参考是实际的clk,则data path上由于增加了X个ns的clock latency,而发生了时序违例。正是因为设置output_delay参考的clock path上没有clock latency。同样,data path上由于增加了X个ns的clock latency,而使得input2reg路径增加了1.5ns的余量。这是因为设置input_delay参考的clock path上没有clock latency。

由此会导致output port约束变得更悲观。同理,会导致input port约束变得更乐观。

为此,我们需要生成一个没有相应时钟pin/port的vclk,然后分别设置clk和vclk各自的clock latency。使得input/output的参考clk为vclk,便可修复时序违例,只不过这个值就需要人工计算,或者使用经验值了。

参考:

静态时序分析—虚拟时钟(virtual clock)与I/O延时约束_拾陆楼的博客-CSDN博客

clock latency 总结_半夏之夜的博客-CSDN博客

在接口时序约束中为什么设置虚拟时钟(virtual clock)? - 知乎 (zhihu.com)

虚拟时钟(Virtual clock)_虚拟时钟的作用_杰出的胡兵的博客-CSDN博客