后端基础——pad

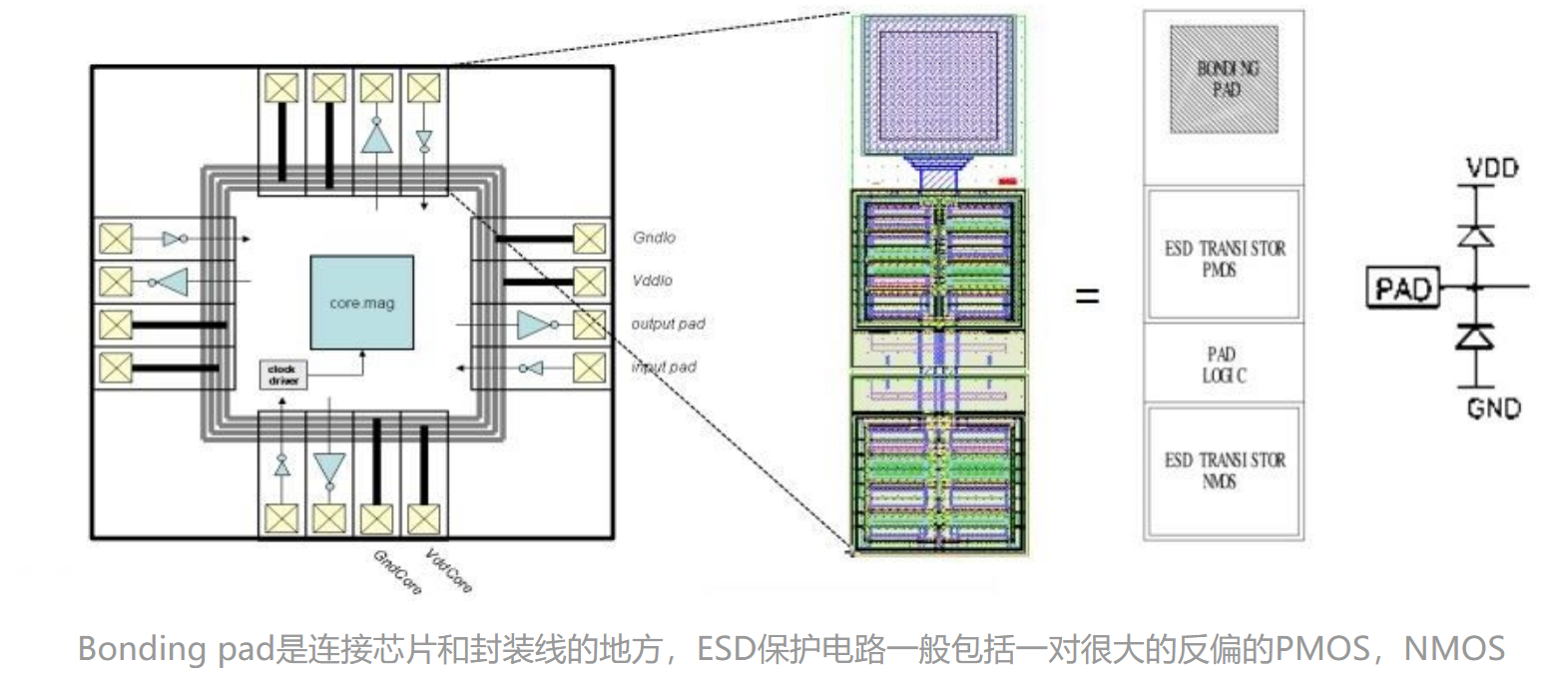

IO pad =pad+电路

IO总的来说由两部分组成,一个是PAD,一个是电路。电路又分为pre 和 post。

PAD的作用是为了封装的时候连接金线。因此,为了防止金线短路,要求PAD之间要有最小距离,具体数值要看你的封装形式。

电路的作用有几方面:ESD保护,level shifter,施密特触发器等等。还有提供电源环路。

二者合在一起构一个IO(也就是I/O pad),有的时候PAD和电路是分开,stagger就是这种情况,在IO limiter的情况下,为了节省面积,将PAD分成两排甚至三排交错的排列,但是电路必须是在一条直线上的(因为电源环路的需求)。

一个基本的pad library,应该可以提供如下几种pad:

- 给pad供电的pad,例如:PAD_VDD, PAD_VSS;

- 给core供电的pad,例如:VDD, VSS; (如果存在多个VDD domain, 还有AVDD, AVSS,之类的pad)

- 模拟信号的pad,例如ANIN (analog的pad一般就是一块铁片,有的vendor推荐用户可以自己基于要求自己再加上一定的ESD保护电路)

- 数字信号的pad,一般有input和output的区别,里面还有包括level shifter,buffers之类的数字电路

一般来说,pad ring会设计成一个方形或者矩形,这样给pad 供电的PAD_VDD, PAD_VSS可以比较均匀的分布在pad ring里面。当然,有时候遇到电路里面有高压的模块,可能不能share整个pad ring,那么pad ring就可能只有方形的三面,也是合理的。

相邻的pad之间需要隔开还是可以紧密挨着,主要是取决于最后封装时候的要求。举个例子,比如每个pad 的宽度是50um,但是封装引脚的最小距离是80um,那么相邻的pad之间就需要加filler(一种特定的cell,里面的PAD_VDD, PAD_VSS是连续的)同时,每个转角处还有专门的Corner cell,也是保证了pad ring里面ESD相关的信号的连续性。

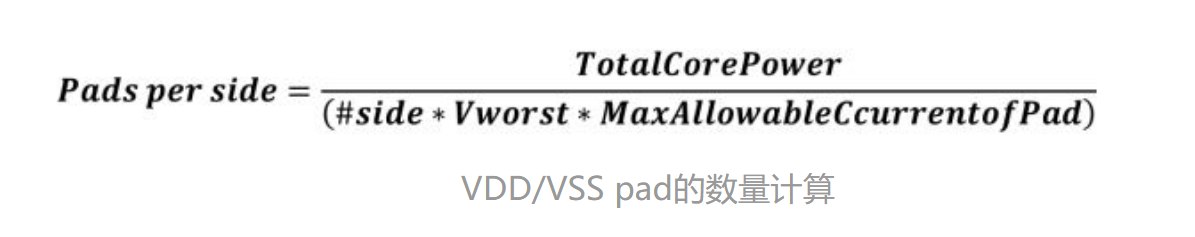

在可能的前提下,尽量多放power pad(可以减小bonding wire的弹跳效应),并让power pad均匀分布。然后是确定所需的电源pad的数量。用下面的公式粗略估计一下,比如总的电流是120mA,然后pad ring的四条边都加上VDD和VSS的pad,每个vdd pad的最大电流是30mA,如果Vworst和core power里面的电源电压一样大,那么每边一个pad就足够了。如果这两个电压值不一样,则应该增加vdd pad的数量。

浙公网安备 33010602011771号

浙公网安备 33010602011771号