手把手带你了解80C51(持续更新)

前言:

我自己学习51单片机呢,也已经有一段时间了,趁着今天有空,把一些重要的知识归纳起来,以便以后回顾。

一、MCS-51的基本结构:

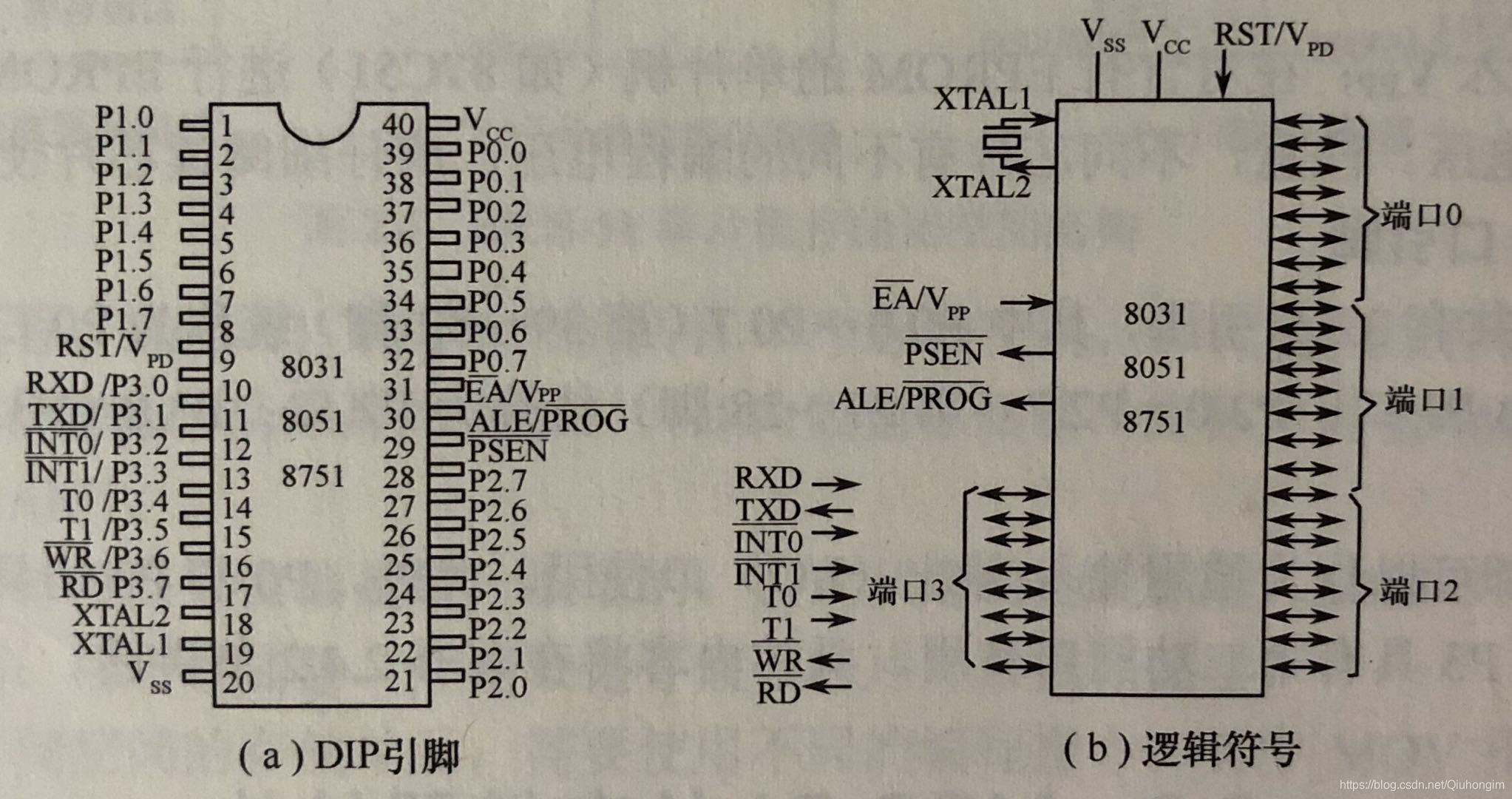

(1)、外部结构:

MCS-51系列单片机一般采用40只引脚的双列直插封装(DIP),以80c51为例,如下图:

80C51的引脚按功能划分可分为3类:

1、电源及晶振引脚;

(1)电源引脚:Vcc(第40脚):接+5V电源引脚 Vss(第20脚):接地引脚

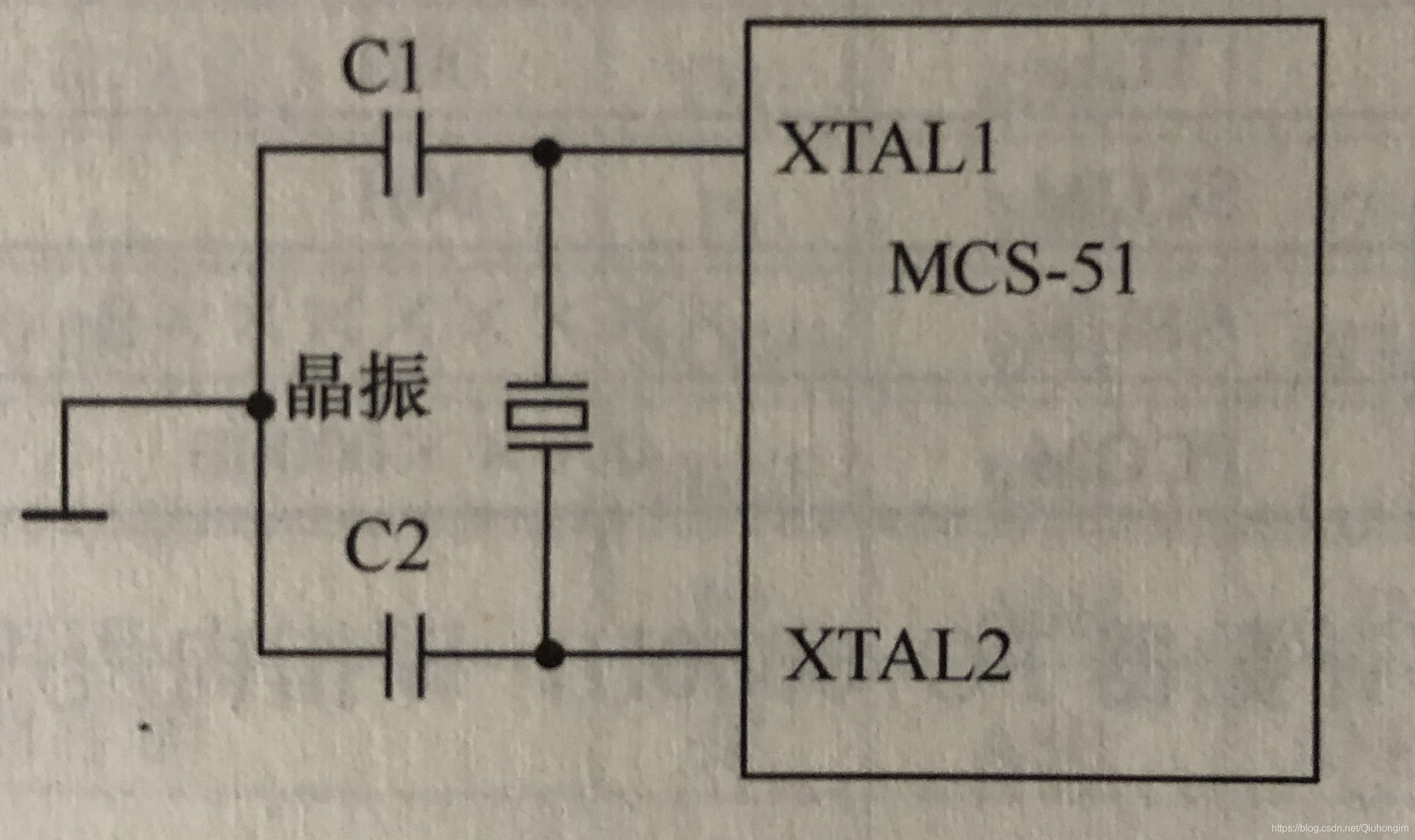

(2)外接晶振引脚:XTAL1(第19脚)、XTAL2(第18脚),逻辑方向为:XTAL2-->XTAL1,外接晶振电路原理图如下:

注意:C1、C2一般取30pF左右,作用是帮助振荡器起振,晶体的振荡频率范围在1.2~13MHz。晶体的振荡频率越高,系统的时钟频率就越高,单片机运行速度与就越快。在通常情况下,MCS-51的时钟频率为6~12MHz。

2、控制引脚:

(1)RST/Vpd(第9脚):

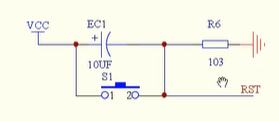

(a)复位端RST:若该引脚上输入满足复位时间要求的高电平(该时间等于系统时钟振荡周期建立时间再加2个机器周期),单片机复位。常用的复位电路如下:

(b)备用电源端Vpd:当主电源Vcc发生故障,降低到某一规定的低电平时,可将外接的+5V电源作为备用电源,为单片机片内的ARM供电,保证片内的RAM信息不丢失,从而保证单片机恢复电压后正常工作。

(2)ALE/PROG(第30引脚):

(a)地址锁存使能输出ALE:当单片机访问外部存储器时,外部存储器的16位地址信号由P0口输出低8位,P2口输出高8位,ALE可作为低8位地址锁存控制信号。当不用做外部存储器地址锁存控制信号时,引脚以时钟脉冲频率的1/6固定输出正脉冲。

(b)编程脉冲输入端PROG:对含有EPROM的单片机,在进行片内EPROM编程时需要由此输入编程脉冲

(3)PSEN(第29引脚):输出访问片外程序存储器读选通信号。CPU在从片外ROM取指令期间,该引脚将在每个机器周期内产生两次负跳变脉冲,用作片外ROM芯片的使能信号。

(4)EA/Vpp(第31脚):外部ROM允许访问/编程电源输入

(a)外部ROM允许访问EA:当EA= 1时,CPU从片内ROM开始读取指令。当程序计数器PC的值超过4KB地址范围时,将自动执行片外ROM的指令。但EA=0时,CPU仅访问片内ROM

(b)编程电源输入Vpp:在对含有EPROM的单片机进行EPROM编程时,此引脚应接芯片的编程电压。(具体的编程电压参考芯片说明手册)

3、并行I/O引脚:

P0~P3口都可作为准双向IO口,但P0口需要外接上拉电阻。

在扩展片外存储器时,8位数据总线由P0口组成,16位地址总线由P0口和P2口组成,其中P0口作为低8位地址总线,P2口作为高8八位地址总线,P3口和PSEN、EA、ALE、RESET则组成控制总线

(2)、内部结构:

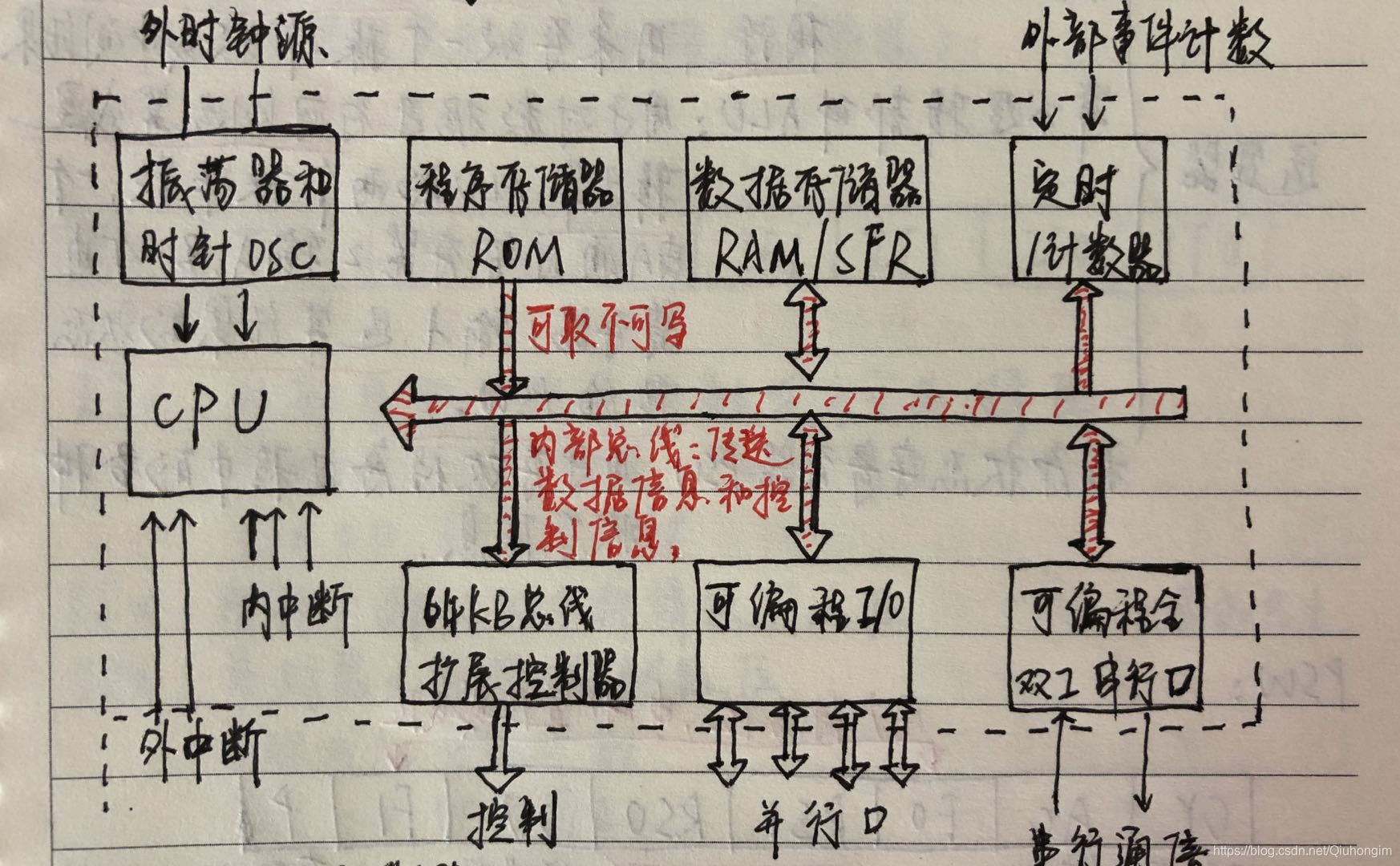

MCS-51基本结构如下:

CPU按功能可分为:控制器和运算器

运算器:

程序计数器PC:16位寄存器,存放下一条指令的地址,当指令取出,PC加1

指令寄存器IR:8位寄存器,暂存待执行的指令,等待译码

指令译码器ID:对指令进行译码,转换成所需的电信号

数据指针DPTR:专业地址指针寄存器,包括DPH和DPL寄存器,其中DPH表示高八位,DPL表示低八位。

控制器:

累加器ACC:8位寄存器,简称A,通过暂存器与ALU(算术逻辑部件)相连,用来存放一个操作数或中间结果

算术逻辑部件(ALU):用来对数据进行四则运算或逻辑运算,ALU的两个操作数,一个由A通过暂存器2输入,另一个由暂存器1输入,运算结果的状态传给PSW(程序状态字寄存器)

程序状态字寄存器(PSW):用来存放程序过程中的各种状态信息

CPU的工作过程:

取指令-->指令译码-->执行指令-->修改指令计数器-->取指令······

二、特殊功能寄存器:

89C51单片机ARM上共有21个特殊寄存器,我只写下一些常用的寄存器。

右边第一位为最低位

PSW(程序状态字寄存器)

| CY | AC | F0 | RS1 | RS0 | OV | F1 | P |

CY:进位标志,进行加减运算,操作结果最高为有进位或借位时,CY由硬件1,否则清零

AC:辅助进位标志,进行加减运算,操作结果的低4位数向高4位产生进位或借位时,由硬件置1,否则清0,也可用于BCD码调整时的判断位

F0、F1:用户标志位,由用户置位或复位

P:奇偶判断标志位,自动追踪A中含"1个数的奇偶性

RS1、RS0:工作寄存组选择方式位

| 工作寄存组 | RS1 | RS0 |

| 0 | 0 | 0 |

| 1 | 0 | 1 |

| 2 | 1 | 0 |

| 3 | 1 | 1 |

TCON(定时、计数控制寄存器)

88H 可位寻址

| TF1 | TR1 | TF0 | TR0 | IE1 | IT1 | IE0 | IT0 |

ITX:外部中断X的中断方式选择位,1 --> 边沿触发有效,0 --> 低电平有效

IEX:外部中断X的中断请求标志位

TRX:定时器X运行控制位,1 --> 开始计时, 0 --> 计时停止

TFX:定时器X溢出标志位。中断执行时由硬件自动清零

TMOD(定时、计数方式控制寄存器)

89H 不可寻址

| GATE | C/T | M1 | M0 | CATE | C/T | M1 | M0 |

CATE:门控位 0 --> TRX=1,TX启动;1 --> TRX=1, INTX=1,TX启动

C/T:定时和外部事件计数方式选择位;0,定时器方式,内部脉冲;1,外部事件计数器方式,外部脉冲

M1、M0工作方式选择位:

| M1 | M0 | 工作方式 | 功能说明 |

| 0 | 0 | 0 | 13位定时/计数器 |

| 0 | 1 | 1 | 16位定时/计数器 |

| 1 | 0 | 2 | 8位自动重装定时/计数器 |

| 1 | 1 | 3 | 3种定时/计数器 |

初值:a = 2^n - t(fosc/12) 计数值:N = 2^n - a

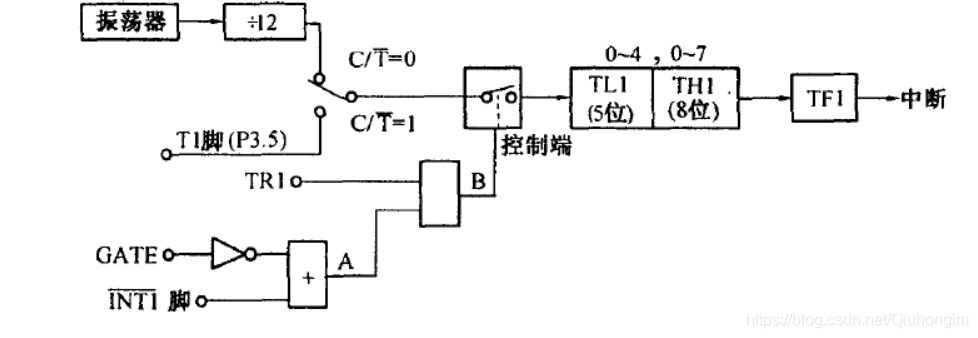

方式0和方式1逻辑结构图(以T1为例):

注意:

1、方式0和方式1的逻辑结构是一样的,区别在于TLX的有效为不同。方式0是低5位有效,高3位补0,方式1全有效。

2、使用方式0时,求出的初值,转换成二进制后,要在低五位后再添3个0,这时的二进制数才是THX和TLX要装进的

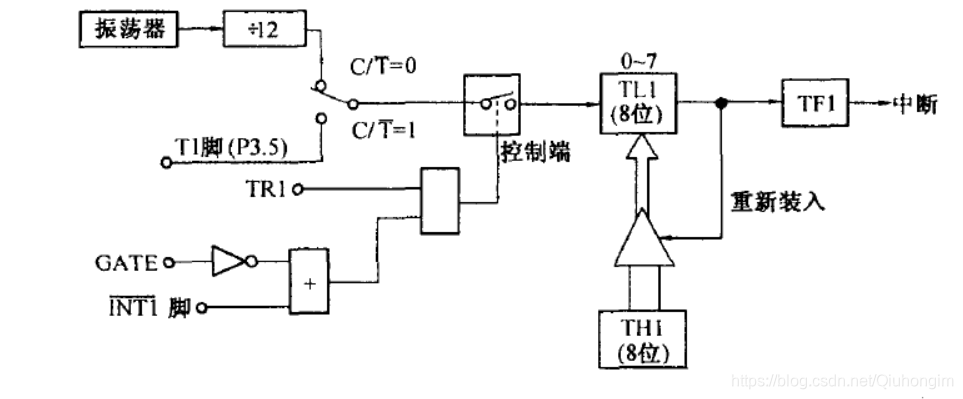

方式2逻辑结构图(以T1为例):

方式3逻辑结构图:

3种组合关系:

TH0+TF1+TR1组成的带中断功能的8位定时器

TL0+TR0+TF0组成的带中断功能的8位定时/计数器

TI组成的无中断功能的定时/计数器

特别说明:

当TH和TL溢出后会使TF置1,进而判断是否执行中断

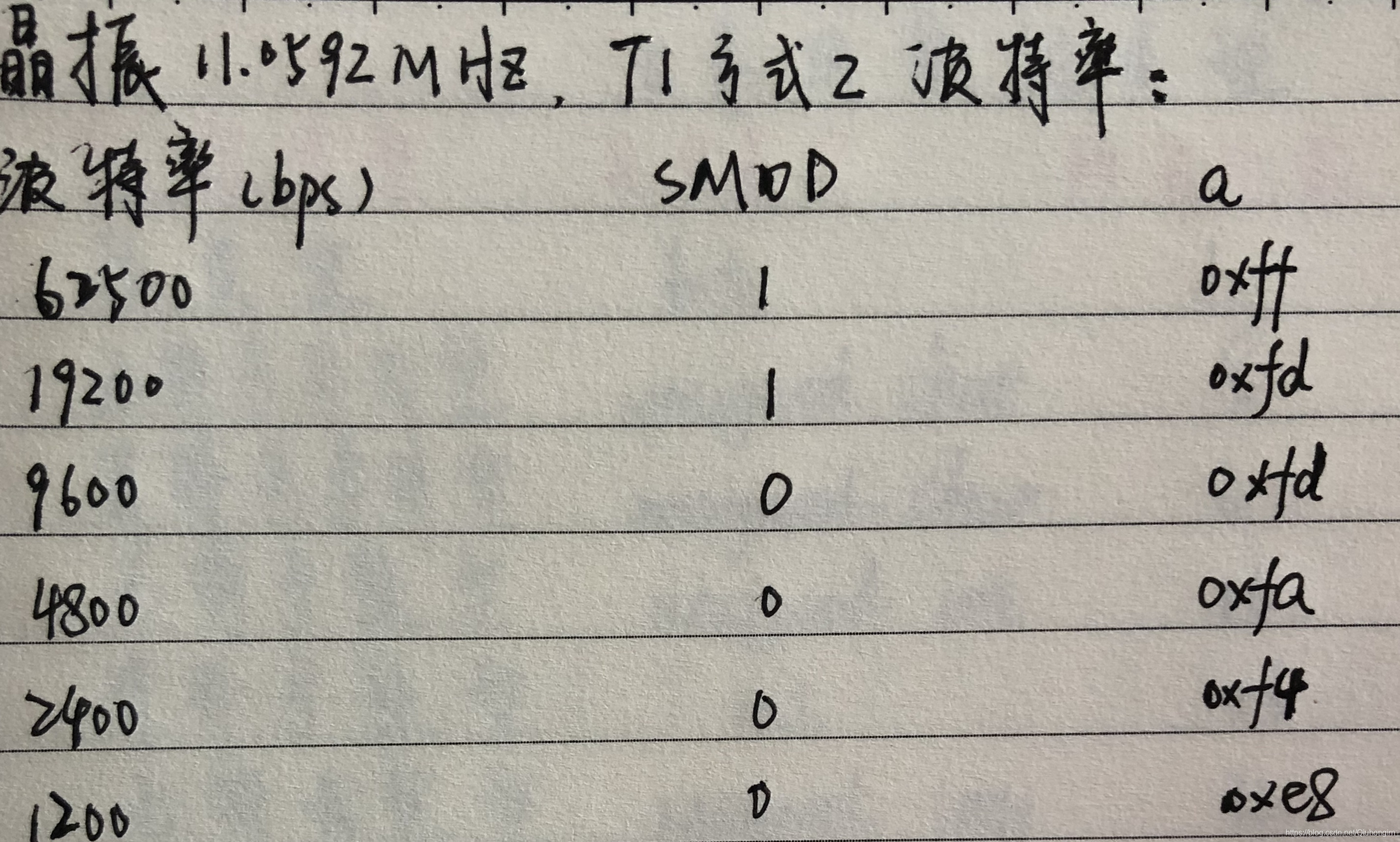

T1可作为波特率发生器使用

当T0为工作方式3时,T1只可使用公式0,1,2,这是因为T0为工作方式3时会占用T1的资源。

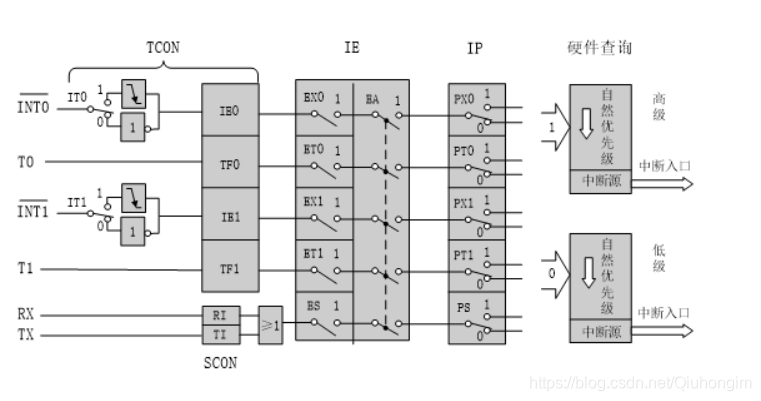

IE(中断允许寄存器)

A8H 可位寻址

| EA | ES | ET1 | EX1 | ET0 | EX0 |

EXX:外部中断X允许位,1 --> 允许中断,0 --> 停止中断

ETX:定时/计数器TX的溢出中断允许标志位,1 --> 允许中断,0 --> 禁止中断

ES:串行口中断允许位,1 --> 允许中断,0 --> 禁止中断

EA:中断允许总控制位,1 --> CPU开放中断,0 --> CPU屏蔽所以的中断申请

IP(中断优先级寄存器)

B8H 可位寻址

| PS | PT1 | PX1 | PT0 | PX0 |

PS:串行口中断优先级控制位

PTX:定时/计数器TX中断优先级控制位

PXX:外部中断X中断优先级控制位

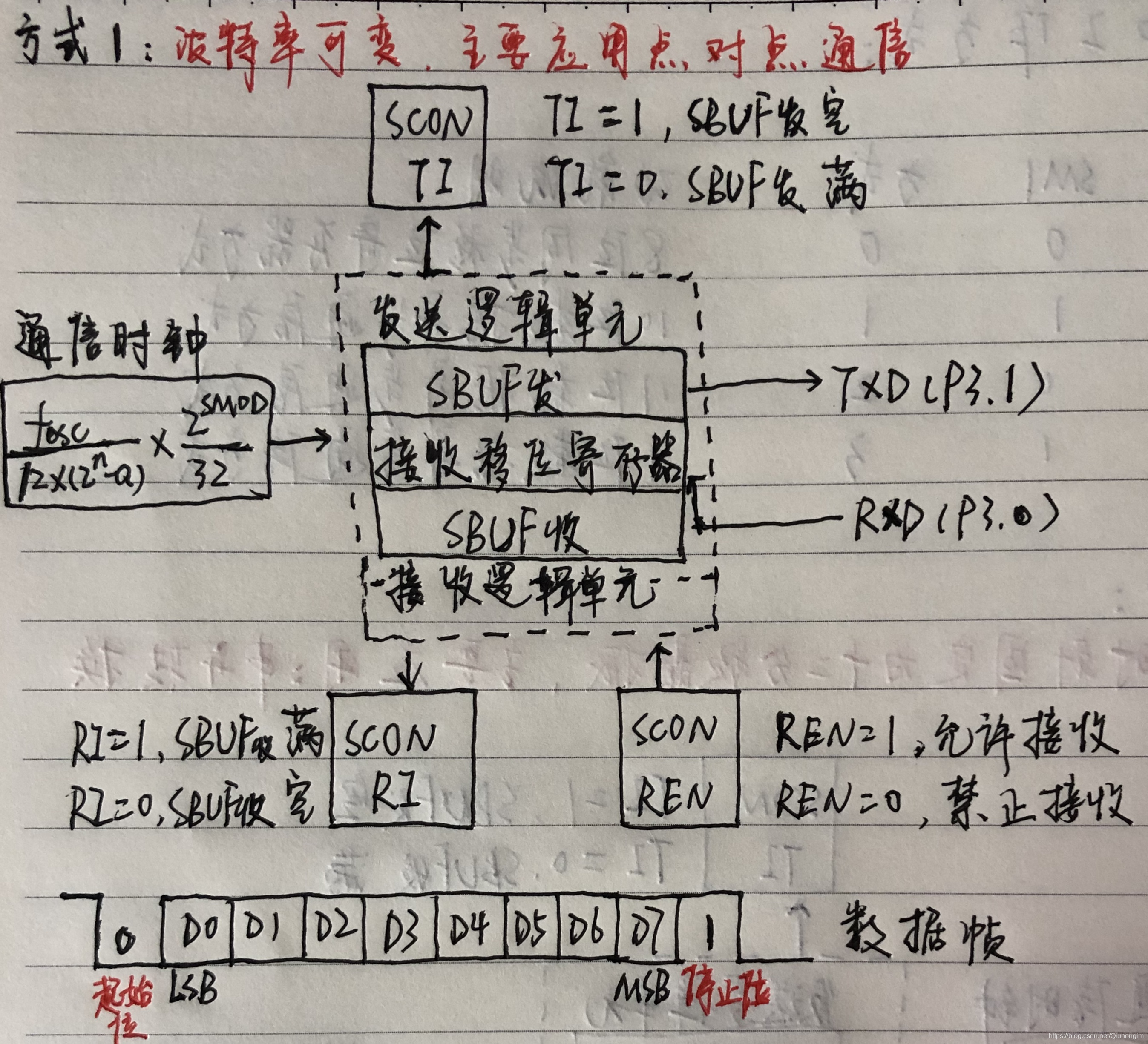

SCON(串行口控制寄存器)

98H 可位寻址

| SM0 | SM1 | SM2 | REN | TB8 | RB8 | TI | RI |

TI、RI:串行通信中断请求标志,发送、接收TI、RI置1,需要软件清0

RB8:接收数据第九位

TB8:发送数据第九位

REN:允许接收控制位,1 --> 允许接收, 0 --> 禁止接收

SM2:多机通信控制位,1 --> 多机通信, 0 --> 点对点通信

SM1、SM0:串行通信工作方式定义位

| SM0 | SM1 | 方式 | 功能说明 |

| 0 | 0 | 0 | 8位同步移位寄存器方式 |

| 0 | 1 | 1 | 10位数据异步通信方式 |

| 1 | 0 | 2 | 11位数据异步通信方式 |

| 1 | 1 | 3 | 11位数据异步通信方式 |

PCON(电源控制寄存器)

| SMOD | GF1 | GF0 | PD | TDL |

SMOD:波特率选择位,1 --> 在原基础上加倍, 0 --> 保持原有数值

GF1、GF0:通有标志位

PD:掉电控制位

TDL:空闲控制位

三、中断系统: