基于Lattice Crosslink PCIe DMA框架(一种通用PCIe DMA框架,基于Lattice、安路 FPGA平台已实现验证)

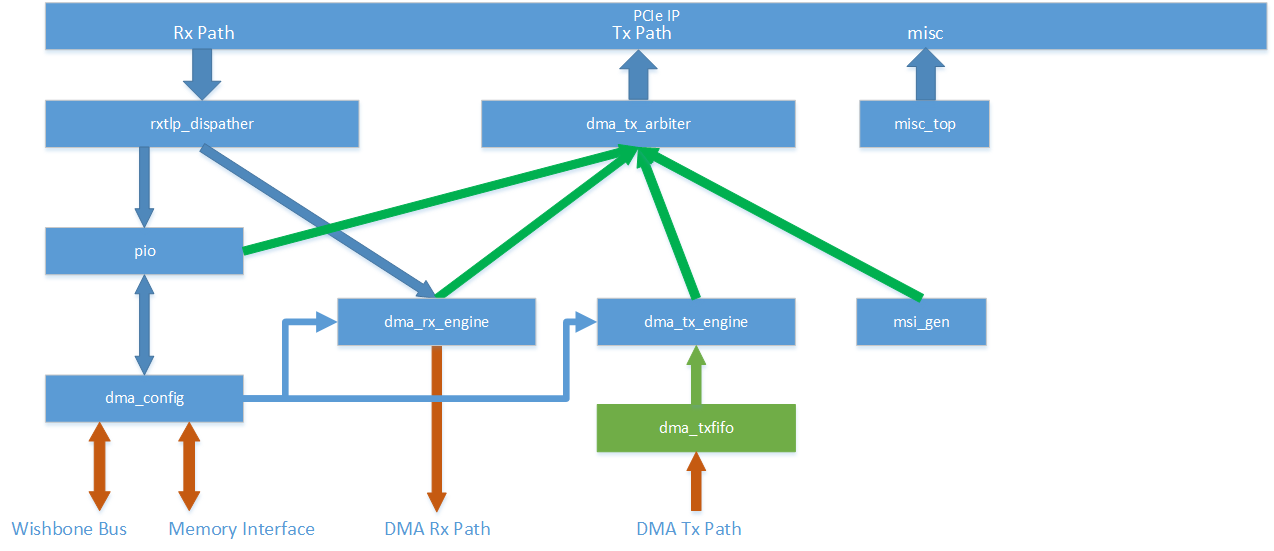

上图所示为一种通用的PCIe DMA框架图,对于FPGA来讲,PCIe核本身一般是硬核,PCIe核内部负责的是PCIe协议层的东西,对外的接口一般是通过AXI Stream或者类似的接口出来,协议的内容为TLP包的内容,因此在实现基于PCIe的DMA是需要直接和TLP报文打交道,当然如果使用厂家提供的DMA IP是不用关心TLP的,厂家一般会把TLP的报文格式封装起来,对外只留AXI协议的访问接口。好处是可以直接拿来用,满足大部分引用场景;但是也就了解不了其中的原理了。

比较通用的DMA一般是会做成链式DMA,Altera提供的DMA较早的器件上都是提供了一个Channing DMA的源码的实例,实际使用过程中还是有些bug存在的。Xilinx厂家生成的一个很简单的PIO访问的例子,不能满足大部分应用场景。还有一些开源的DMA,个人看过在Xilinx平台上实现的开源PCIe DMA “epee”,代码很高,不过没有相关文档,需要看代码,感兴趣的读者可以搜索去看一下。

链式DMA的应用场景是在主机单次配置的数据需要保存在主机DDR中的多个不连续的位置时用到,此时的效率最高,可以支持的场景更多。不过大部分的应用场景其实也用不到链式DMA;上图所示为一个Simple模式的DMA,即通过简单的配置地址、长度、开始位就可以开启DMA传输,已经在Lattice Crosslink 系列及安路的PH100平台上验证,效率也很好,在大数据量传输的时候效率可以达到80%。实现上述DMA的初衷也是上述两个厂家不能提供有效好用的DMA,提供的Demo太过粗糙,于是笔者在结合以前使用经验及开源代码的理解基础上实现了上述DMA框架,分享给大家。

另外分享一个相关的连接:http://xillybus.com/tutorials/pci-express-tlp-pcie-primer-tutorial-guide-1/

感兴趣的可以加Q交流:QQ:314097602

************************************************************************************************

作者:huakaimanlin

出处:https://www.cnblogs.com/huakaimanlin/

版权所有,如需转载请声明出处

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· TypeScript + Deepseek 打造卜卦网站:技术与玄学的结合

· Manus的开源复刻OpenManus初探

· .NET Core 中如何实现缓存的预热?

· 阿里巴巴 QwQ-32B真的超越了 DeepSeek R-1吗?

· 如何调用 DeepSeek 的自然语言处理 API 接口并集成到在线客服系统