ODDR使用注意

最近项目用到了千兆以太网,PHY通过ZYNQ的PL管脚进入FPGA后,直接连到PS端的MAC,PL端使用ODDR保证MAC发送的Tx信号到PHY的接收时序,

PHY用的是TI的DP83867,没注意这货在GMII的模式下不能调整clock和Data的相位关系,结果FPGA保证了沿对齐,PHY也是沿对齐去采集,导致不同批次的硬件表现不一致!!!血的教训啊。

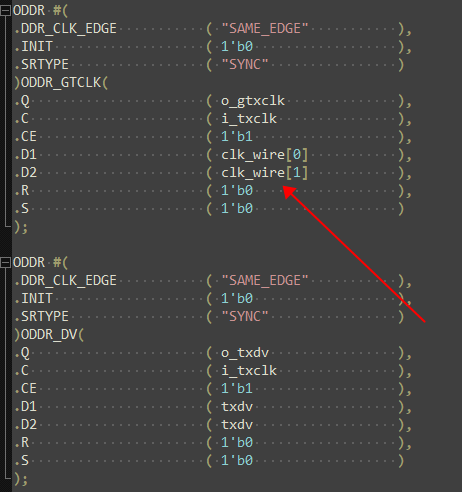

记录下ODDR的输出模式:

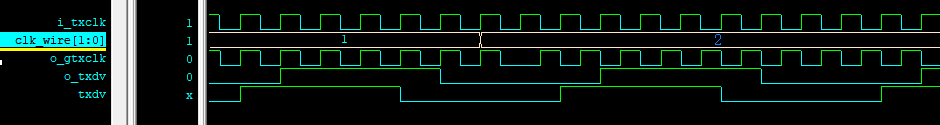

clk_wire和输出的关系对应如下仿真波形:

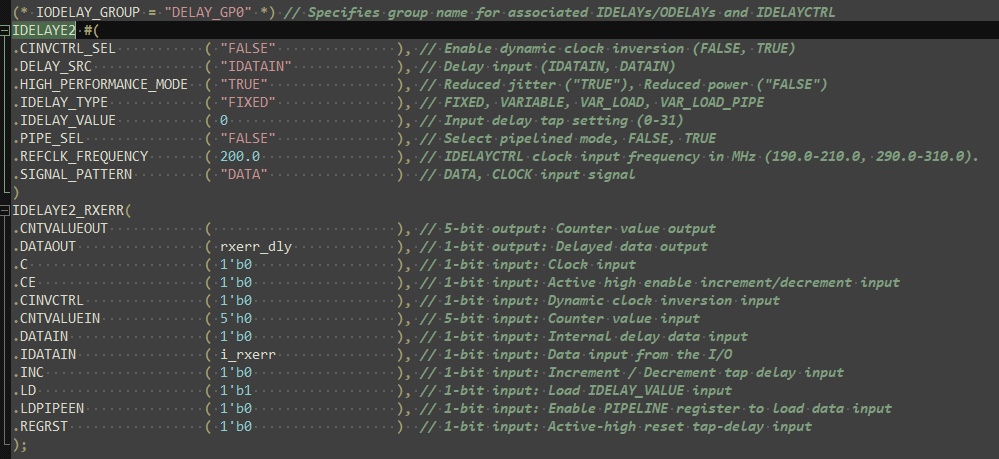

2. 对于PHY输出的RX_CLK、RX_DV、RX_ERR、RX_D信号,FPGA内部需要查看时钟即数据的延迟路径进行分析。本例中使用iodelay只对RX_DV、RX_ERR、RX_D进行了约束,以满足PHY输出时序的要求(DP83867在GMII模式下不支持PHY设置延迟)。

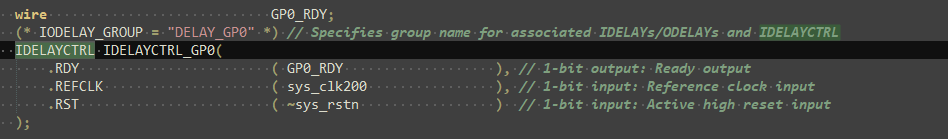

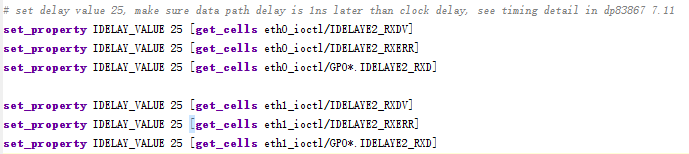

iodelay使用时需要使用IDELAYCTRL、IDELAYE2,其中IDELAYCTRL在一个工程中不能有多个实例,项目中用到了两个网口,因此将IDELAYCTRL放在了顶层模块中,在各个网络模块中使用IDELAYE2进行延迟。在xdc中进行延迟值的设置,分别如下:

************************************************************************************************

作者:huakaimanlin

出处:https://www.cnblogs.com/huakaimanlin/

版权所有,如需转载请声明出处