MPSOC之调试fsbl

最近新做的MPSOC板子回来了,硬件测完上电一跑傻眼了,连最基本的fsbl跑起来都没有任何打印,串口也量了硬件是通的。。。

好一通折腾发现可以在SDK下进行单步调试,但是到某个位置后就死循环了,而且默认是进入汇编的界面,更是看不懂了。Google+Xilinx官网搜索了半天后发现了不少有用的信息,参考如下链接,首先在SDK下设置好后可以进入C调试界面了,然后定位在了psu_ddr_phybringup_data这个函数中,之所以串口都没有打印,是因为串口打印的初始化也在这个函数之后了。

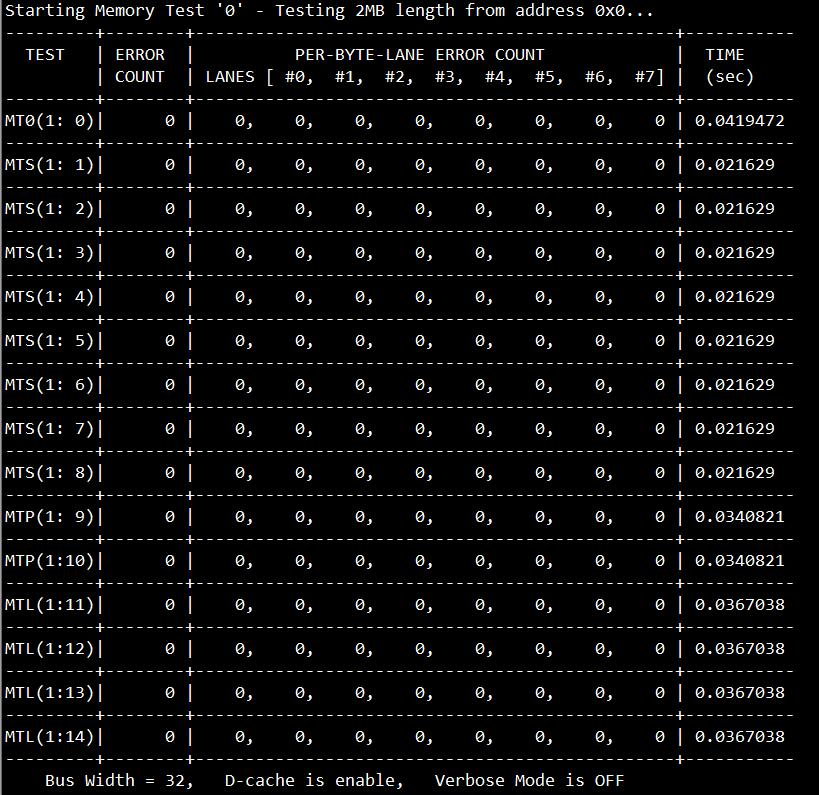

最后发现还是在最容易出问题的DDR部分出问题了,MPSOC设计的是4片DDR4拼接成的64bit。于是降频,降到DDR4最低的1600MHz,反复确认参数,终于可以初始化通过了,以为问题解决了,结果软件拿到后在uboot阶段莫名其妙的不固定位置的就打印异常了,还以为软件那个地方没搞好。后来还是怀疑DDR的稳定性,发现在SDK工具里有专门的Zynq MP DRAM tests工程,这个测试工程功能很强大,会比较全面的测试DDR访问错误率。已测试发现确实是DDR不稳定。都已经降到最低频率了不能再继续降频了。尝试32bit模式,不进行硬件调整的情况下还是效果差不多。分析半天觉得拆掉两片DDR4的颗粒会改善负载,拆掉后效果立竿见影,32位终于稳定了!!!

fsbl的调试方法详见如下两个链接吧。

测试工程中详细打印了哪个lane出问题,lane0~lane7对应到具体byte,进一步对应到颗粒。

更新:

发现DDR4在设置界面里只能选择1600T这些选项,但是实际上可以运行在低于1600M的速率,需要将始终频率设置低后,根据页面提示修改相应参数即可。

参考链接:

https://forums.xilinx.com/t5/%E5%B5%8C%E5%85%A5%E5%BC%8F-%E7%A1%AC%E4%BB%B6%E7%B3%BB%E7%BB%9F%E5%BC%80%E5%8F%91/%E5%85%B3%E4%BA%8EMPSOC%E5%90%AF%E5%8A%A8%E6%97%B6%E5%8D%A1%E5%9C%A8fsbl%E7%9A%84%E9%97%AE%E9%A2%98/td-p/1144183

https://forums.xilinx.com/t5/%E5%B5%8C%E5%85%A5%E5%BC%8F-%E5%B7%A5%E5%85%B7-%E8%BD%AF%E4%BB%B6%E5%BC%80%E5%8F%91/MPSoC%E5%90%AF%E5%8A%A8%E5%8D%A1%E5%9C%A8psu-ddr-phybringup-data/td-p/1143754