4.7 Controller Memory Buffer

4.7 Controller Memory Buffer

The Controller Memory Buffer (CMB) is a region of general purpose read/write memory on the controller that may be used for a variety of purposes. The controller indicates which purposes the memory may be used for by setting support flags in the CMBSZ register.

Submission Queues in host memory require the controller to perform a PCI Express read from host memory in order to fetch the queue entries. Submission Queues in controller memory enable host software to directly write the entire Submission Queue Entry to the controller's internal memory space, avoiding one read from the controller to the host. This approach reduces latency in command execution and improves efficiency in a PCI Express fabric topology that may include multiple switches. Similarly, PRP Lists or SGLs require separate fetches across the PCI Express fabric, which may be avoided by writing the PRP or SGL to the Controller Memory Buffer. Completion Queues in the Controller Memory Buffer may be used for peer to peer or other applications. For writes of small amounts of data, it may be advantageous to have the host write the data and/or metadata to the Controller Memory Buffer rather than have the controller fetch it from host memory.

The contents of the Controller Memory Buffer are initially undefined. Host software should initialize any memory before it is referenced (e.g., a Completion Queue shall be initialized by host software in order for the Phase Tag to be used correctly).

A controller memory based queue is used in the same manner as a host memory based queue – the difference is the memory address used is located within the controller’s own memory rather than in the host memory. The Admin or I/O Queues may be placed in the Controller Memory Buffer. For a particular queue, all memory associated with it shall reside in either the Controller Memory Buffer or host memory. For all queues in the Controller Memory Buffer, the queue shall be physically contiguous.

The controller may support PRPs and SGLs in the Controller Memory Buffer. For a particular PRP List or SGL associated with a single command, all memory associated with the PRP List or SGLs shall reside in either the Controller Memory Buffer or host memory. The PRPs and SGLs for a command may only be placed in the Controller Memory Buffer if the associated command is present in a Submission Queue in the Controller Memory Buffer.

The controller may support data and metadata in the Controller Memory Buffer. All data or metadata associated with a particular command shall be located in either the Controller Memory Buffer or host memory.

If the requirements for the Controller Memory Buffer use are violated by the host, the controller shall fail the associated command with Invalid Use of Controller Memory Buffer status.

The address region allocated for the CMB shall be 4 KB aligned. It is recommended that a controller allocate the CMB on an 8 KB boundary. The controller shall support burst transactions up to the maximum payload size, support byte enables, and arbitrary byte alignment. The host shall ensure that all writes to the CMB that are needed for a command have been sent before updating the SQ Tail doorbell register. The Memory Write Request to the SQ Tail doorbell register shall not have the Relaxed Ordering bit set, to ensure that it arrives at the controller after all writes to the CMB.

4.7控制器内存缓冲区

控制器内存缓冲区(CMB)是控制器上的通用读/写存储器区域,可用于多种目的。控制器通过在CMBSZ寄存器中设置支持标志来指示存储器可用于的目的。

主机内存中的提交队列要求控制器执行从主机内存中读取PCI Express的操作,以获取队列条目。控制器内存中的提交队列使主机软件可以将整个提交队列条目直接写入控制器的内部存储器空间,避免从控制器向主机进行一次读取。此方法减少了命令执行的延迟,并提高了可能包含多个交换机的PCI Express结构拓扑的效率。同样,PRP列表或SGL需要在整个PCI Express结构中进行单独的提取,这可以通过将PRP或SGL写入控制器内存缓冲区来避免。控制器内存缓冲区中的完成队列可用于对等或其他应用程序。对于少量数据的写入,使主机将数据和/或元数据写入控制器内存缓冲区而不是由控制器从主机存储器中获取数据和/或元数据可能是有利的。

控制器内存缓冲区的内容最初是不确定的。主机软件应在引用任何内存之前对其进行初始化(例如,主机队列应初始化完成队列,以便正确使用阶段标签)。

基于控制器内存的队列的使用方式与基于主机内存的队列的使用方式相同–区别在于所使用的内存地址位于控制器自身的内存中,而不是位于主机内存中。管理员或I / O队列可以放置在控制器内存缓冲区中。对于特定队列,与其相关的所有内存都应驻留在控制器内存缓冲区或主机内存中。对于控制器内存缓冲区中的所有队列,该队列在物理上应是连续的。

控制器可以在控制器内存缓冲区中支持PRP和SGL。对于与单个命令关联的特定PRP列表或SGL,与PRP列表或SGL关联的所有内存均应驻留在控制器内存缓冲区或主机内存中。如果相关的命令存在于控制器内存缓冲区的提交队列中,则命令的PRP和SGL只能放置在控制器内存缓冲区中。

控制器可以在控制器内存缓冲区中支持数据和元数据。与特定命令关联的所有数据或元数据应位于控制器存储器缓冲区或主机存储器中。

如果主机违反了控制器内存缓冲区的使用要求,则控制器应使关联的命令失败,并显示“控制器内存缓冲区的使用无效”状态。

为CMB分配的地址区域应对齐4 KB。建议控制器在8 KB边界上分配CMB。控制器应支持最大最大有效载荷大小的突发事务,支持字节使能和任意字节对齐。主机应确保在更新SQ尾门铃寄存器之前已发送命令所需的所有对CMB的写入。对SQ尾门铃寄存器的存储器写请求不应设置放松顺序位,以确保在所有对CMB的写操作后它到达控制器。

4.8 Namespace List

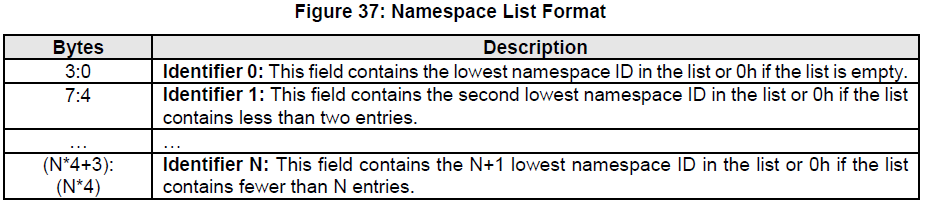

A Namespace List, defined in Figure 37, is an ordered list of namespace IDs. Unused entries are zero filled.

4.8命名空间列表

图37中定义的名称空间列表是名称空间ID的有序列表。 未使用的条目填充为零。

4.9 Controller List

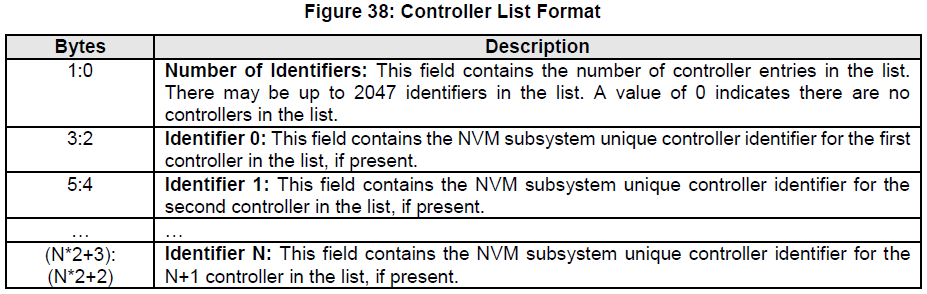

A Controller List, defined in Figure 38, is an ordered list of ascending controller IDs. The controller identifier is defined in bytes 79:78 of the Identify data structure in Figure 109. Unused entries are zero-filled.

4.9控制器清单

图38中定义的控制器列表是升序控制器ID的有序列表。 控制器标识符在图109的“标识”数据结构的字节79:78中定义。未使用的条目填充为零。

4.10 Fused Operations

Fused operations enable a more complex command by “fusing” together two simpler commands. This feature is optional; support for this feature is indicated in the Identify Controller data structure in Figure 109. In a fused operation, the requirements are:

The commands shall be executed in sequence as an atomic unit. The controller shall behave as if no other operations have been executed between these two commands.

The operation ends at the point an error is encountered in either command. If the first command in the sequence failed, then the second command shall be aborted. If the second command in the sequence failed, then the completion status of the first command is sequence specific.

The LBA range, if used, shall be the same for the two commands. If the LBA ranges do not match, the commands should be aborted with status of Invalid Field in Command.

The commands shall be inserted next to each other in the same Submission Queue. If the first command is in the last slot in the Submission Queue, then the second command shall be the first slot in the Submission Queue as part of wrapping around. The Submission Queue Tail doorbell pointer update shall indicate both commands as part of one doorbell update.

If the host desires to abort the fused operation, the host shall submit an Abort command separately for each of the commands.

A completion queue entry is posted by the controller for each of the commands.

Whether a command is part of a fused operation is indicated in the Fused Operation field of Command Dword 0 in Figure 10. The Fused Operation field also indicates whether this is the first or second command in the operation.

4.10融合操作

融合操作通过将两个更简单的命令“融合”在一起,从而实现了更复杂的命令。此功能是可选的。在图109的“识别控制器”数据结构中指示了对此功能的支持。在融合操作中,要求是:

这些命令应按原子单位顺序执行。控制器的行为就像在这两个命令之间没有执行其他操作一样。

操作在任一命令中遇到错误的地方结束。如果序列中的第一条命令失败,则第二条命令应中止。如果序列中的第二条命令失败,则第一条命令的完成状态是特定于序列的。

如果使用LBA范围,则两个命令的LBA范围应相同。如果LBA范围不匹配,则应中止命令,并且命令中的Invalid Field状态无效。

命令应在同一提交队列中彼此相邻插入。如果第一个命令在“提交队列”的最后一个时隙中,则第二个命令应是“提交队列”中的第一个时隙,作为环绕的一部分。提交队列尾部门铃指针更新应将两个命令指示为一个门铃更新的一部分。

如果主机希望中止融合操作,则主机应分别为每个命令提交中止命令。

控制器为每个命令发布完成队列条目。

在图10的Command Dword 0的Fused Operation字段中指示命令是否为融合操作的一部分。FusedOperation字段还指示这是该操作中的第一条命令还是第二条命令。