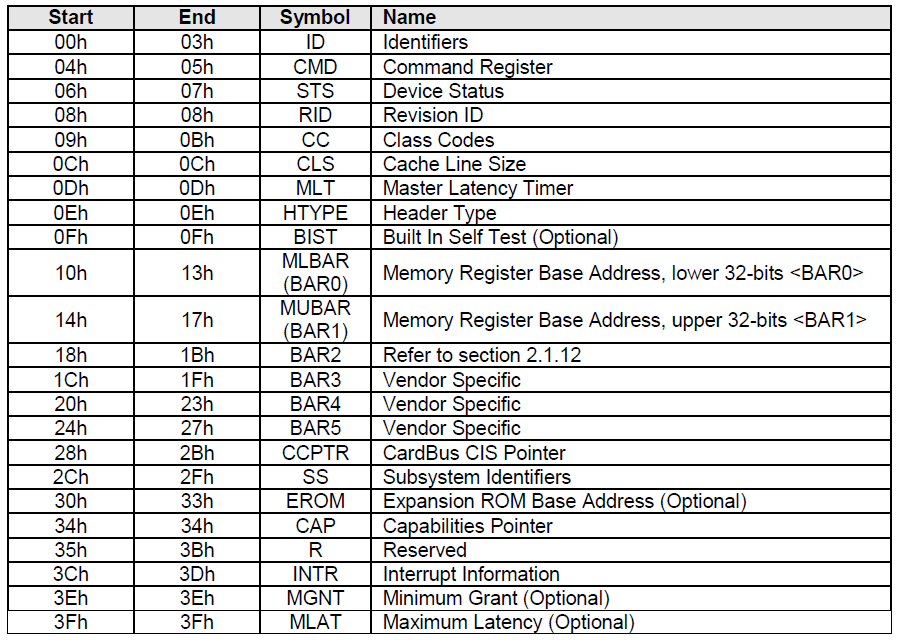

2.1 PCI Header

NOTE: NVM Express implementations that reside behind PCI compliant bridges, such as PCI Express Endpoints, are restricted to having 32-bit assigned base address registers due to limitations on the maximum address that may be specified in the bridge for non-prefetchable memory. See the PCI Bridge 1.2 specification for more information on this restriction.

注意:由于在桥接器中为不可预取内存指定的最大地址的限制,驻留在PCI兼容桥(例如PCI Express端点)后面的NVM Express实施仅限于具有32位分配的基地址寄存器。 有关此限制的更多信息,请参见PCI Bridge 1.2规范。

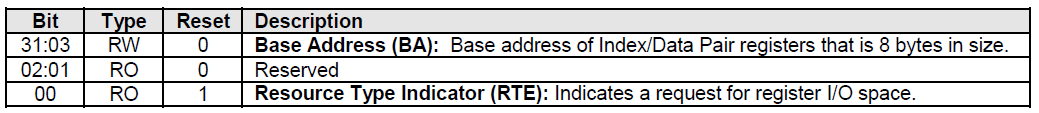

2.1.12 Offset 18h: BAR2 – Index/Data Pair Register Base Address or Vendor Specific (Optional)

If this register is configured as I/O space, then this register specifies the Index/Data Pair base address and is configured as shown in the table below. These registers are used to access the memory registers defined in section 3 using I/O based accesses.

2.1.12偏移量18h:BAR2 –索引/数据对寄存器基地址或特定于供应商的(可选)

如果该寄存器被配置为I / O空间,则该寄存器指定索引/数据对基地址,并如下表所示进行配置。 这些寄存器用于通过基于I / O的访问来访问第3节中定义的存储寄存器。

If this register is configured as memory space (Resource Type Indicator is cleared to ‘0’), then the BAR2 register is vendor specific. Vendor specific space may also be allocated at the end of the memory registers defined in section 3.

如果将此寄存器配置为内存空间(资源类型指示符被清除为“ 0”),则BAR2寄存器是特定于供应商的。 供应商特定空间也可以分配在第3节中定义的存储寄存器的末尾。

2.1.13 Offset 1Ch – 20h: BAR3 – Vendor Specific

The BAR3 register is vendor specific. Vendor specific space may also be allocated at the end of the memory registers defined in section 3.

2.1.14 Offset 20h – 23h: BAR4 – Vendor Specific

The BAR4 register is vendor specific. Vendor specific space may also be allocated at the end of the memory registers defined in section 3.

2.1.15 Offset 24h – 27h: BAR5 – Vendor Specific

The BAR5 register is vendor specific. Vendor specific space may also be allocated at the end of the memory registers defined in section 3.