2 System Bus (PCI Express) Registers

This section describes the PCI Express register values when the PCI Express is the system bus used. Other system buses may be used in an implementation. If a system bus is used that is not a derivative of PCI, then this section is not applicable.

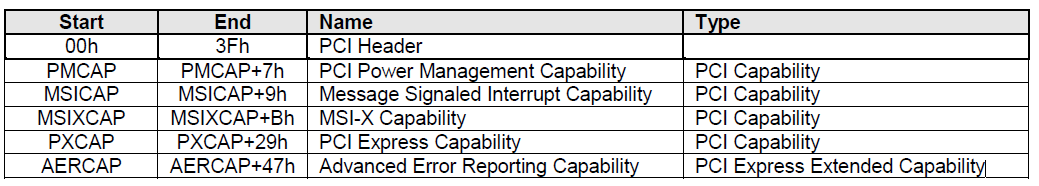

This section details how the PCI Header, PCI Capabilities, and PCI Express Extended Capabilities should be constructed for an NVM Express controller. The fields shown are duplicated from the appropriate PCI or PCI Express specifications. The PCI documents are the normative specifications for these registers and this section details additional requirements for an NVM Express controller.

本节介绍当PCI Express是所使用的系统总线时的PCI Express寄存器值。 在实现中可以使用其他系统总线。 如果使用的系统总线不是PCI的衍生产品,则本节不适用。

本节详细介绍应如何为NVM Express控制器构造PCI标头,PCI功能和PCI Express扩展功能。 显示的字段与相应的PCI或PCI Express规范重复。 PCI文档是这些寄存器的规范规范,本节详细介绍了NVM Express控制器的其他要求。

MSI-X is the recommended interrupt mechanism to use. However, some systems do not support MSI-X, thus devices should support both the MSI Capability and the MSI-X Capability.

It is recommended that implementations support the Advanced Error Reporting Capability to enable more robust error handling.

建议使用MSI-X中断机制。 但是,某些系统不支持MSI-X,因此设备应同时支持MSI功能和MSI-X功能。

建议实现支持高级错误报告功能,以实现更强大的错误处理。