时钟分频

在设计项目的时候,系统时钟通常只有一个,而在工程应用中经常用到各种频率的时钟,这时候就要对系统时钟进行分频或者倍频以满足工程需求。

1、时钟分频两种方法:

1) PLL IP核:频率之间是否成整数比均可,可分频可倍频

2) Verilog 编写代码:频率之间得成整数比,仅可分频

在作为时钟使用的时候,通常采用PLL IP核的方式。

2、Verilog编写代码分频:偶分频、奇分频

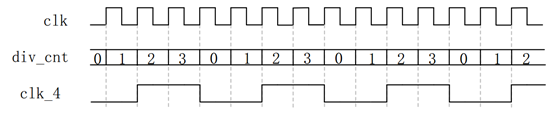

1)偶分频:在时钟的上升沿进行计数,如下图所示为4分频的波形,计数器计数值为0~N-1,分频时钟在N/2-1的时候拉高,在N-1的时候拉低。

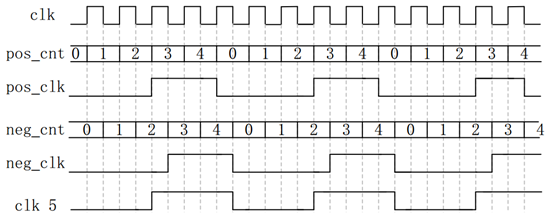

2)奇分频:在时钟的上升沿和下降沿分别采用计数器进行计数到N-1,得到上升沿的计数和下降沿的计数。如下图所示为5分频的波形,上升沿/下降沿时钟在计数器的N/2(取整数)的时候拉高,在N-1的时候拉低,最后将上升沿分频的时钟和下降沿分频的时钟进行相或,得到奇分频时钟。

浙公网安备 33010602011771号

浙公网安备 33010602011771号