8.2 DRAM和SRAM

计算机组成

8 存储层次结构

8.2 DRAM和SRAM

SRAM比较快,DRAM比较慢;SRAM比较贵,DRAM比较便宜。记住这些结论是很容易的,但是比是什么更重要的是为什么。那在这一节我们就从电路的级别来探索DRAM和SRAM为什么会具有他们这样各自的特点。

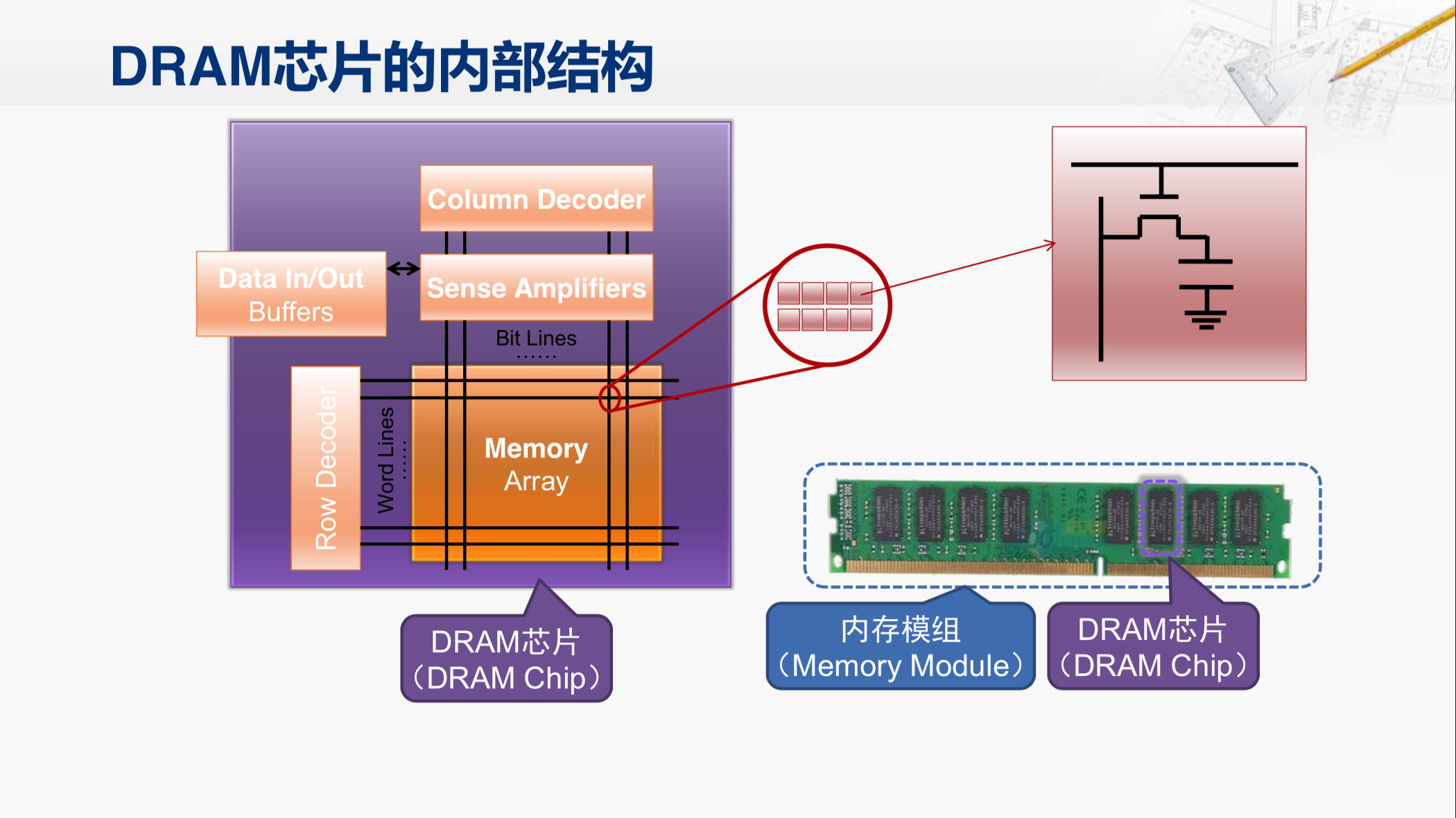

右下角就是我们平常在计算机当中使用的内存条,规范的说法我们应该叫它内存模组。而一个内存模组实际上就是由一块小电路板再加上若干的DRAM芯片构成。在这个内存模组上一共有八个DRAM芯片。然后我们来看DRAM芯片内部的结构。DRAM芯片内部核心的结构就是左边这个存储阵列,由若干行和若干列构成。如果从外部给入行地址,再给入列地址,那么就可以由此选中一个存储单元。而在一个存储单元当中往往包含着若干个比特,常见的有4bit或者8bit。每一个比特都采用了右上角这样一个电路的结构,这个结构我们称为DRAM的一个基本存储单元。

这个基本单元就通过这个电容来保存了一个比特的信息。那在DRAM芯片当中还有一些地址译码的逻辑,根据外部送入的行地址生成行选择信号,再根据外部送入的列地址生成列选择信号。通过这样的行列选择信号就可以选中对应的存储单元。其实也就是将这样的电容联通到外部的输入输出线,如果是写入就是由外部的数据线驱动对电容进行充电或者放电的操作,从而完成写入1或者0。如果是读操作,则是由电容对外部的数据信号线进行驱动,从而完成读出0或者1。

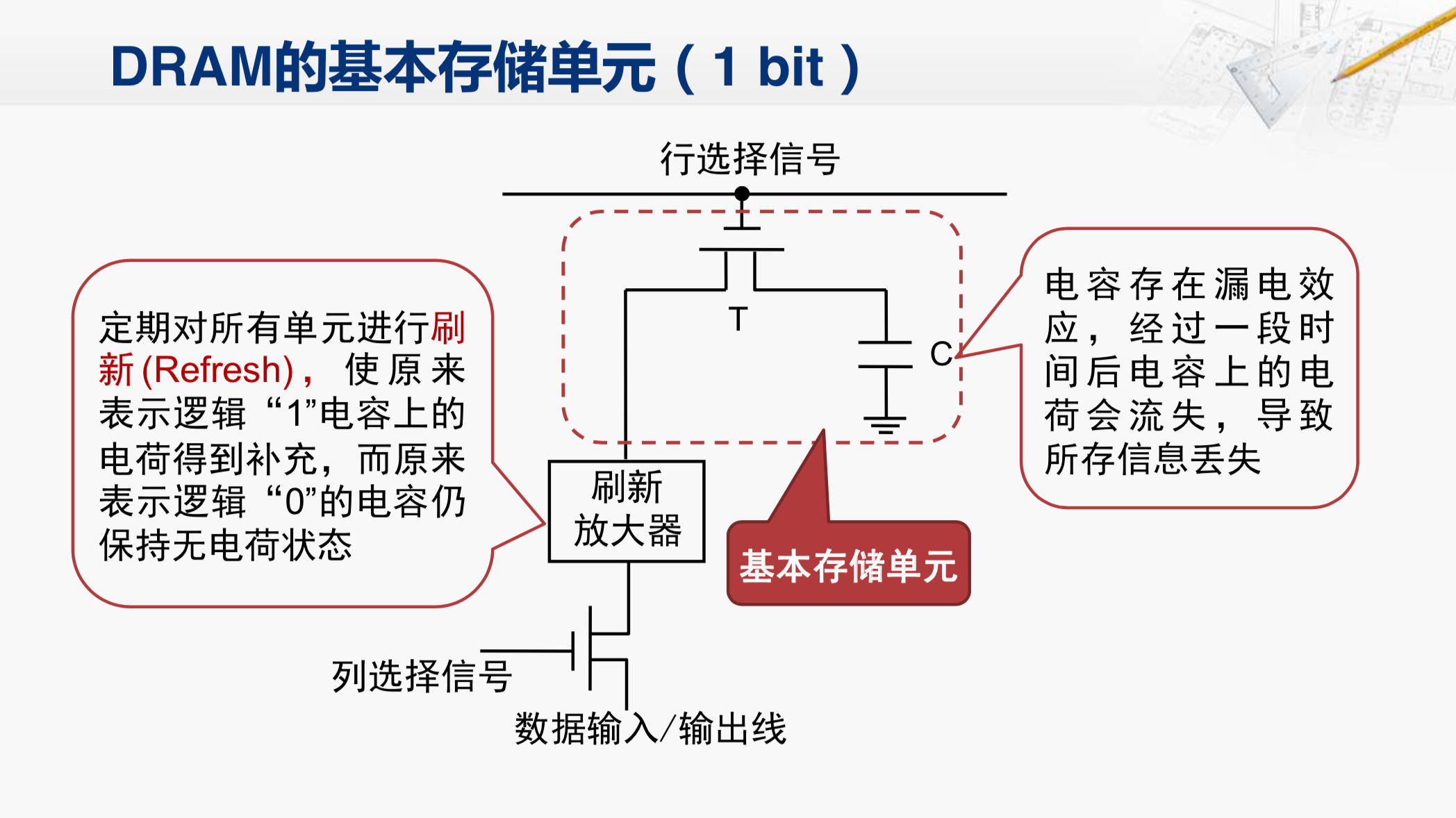

这个电路结构非常简单,但是我们要注意电容是存在漏电效应的。如果经过一段时间电容上的电荷流失过多,我们就会丢失它所存的信息。因此,为了保证DRAM存储的信息的正确性,我们就需要定期对所有的单元进行刷新。如果这个电容保存的数据信息是1,那么应该补充这个电容的电荷;而如果它原先保存的是数据0,那么也需要通过刷新让它保持无电荷的状态。

这就是DRAM的基本结构和运行的原理。

那现在的PC机当中大多是采用DRAM作为主存储器也就是内存。当然DRAM也有很多种不同的实现,比如SDRAM,这个S是同步的缩写,它是在DRAM的基本结构基础上对输入输出接口进行时钟同步,从而提高了读写的效率。而现在更为常用的内存,则是在SDARAM的基础上又进行了进一步的改进,比如说这些年有DDR1、DDR2、DDR3,这些不同的内存标准都是在SDRAM的基础上进行的改进和升级。

总体来说由于每个DRAM的基本存储单元非常的简单。所以,它能够做到很高的集成度,而且功耗也比较低。我们可以用较低的成本制造出大容量的DRAM芯片。当然它的缺点也跟它的这个结构有关,因为给予了电容充放电的方式。所以,DRAM的读写速度还是比较慢的,而且它还需要定时刷新,这进一步影响了DRAM读写性能。那么与DRAM相对的,我们还有一种常用的存储单元是SRAM。

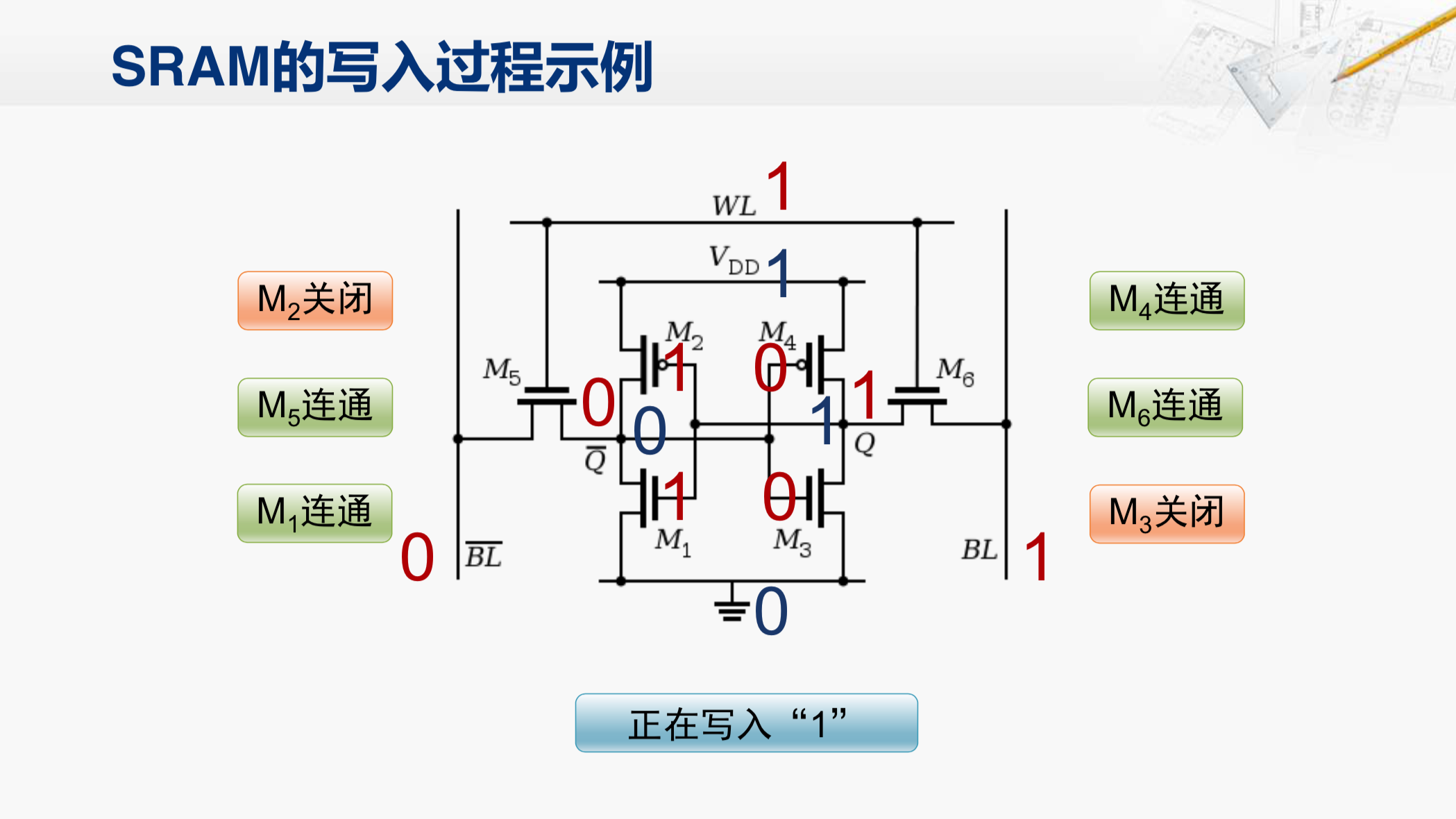

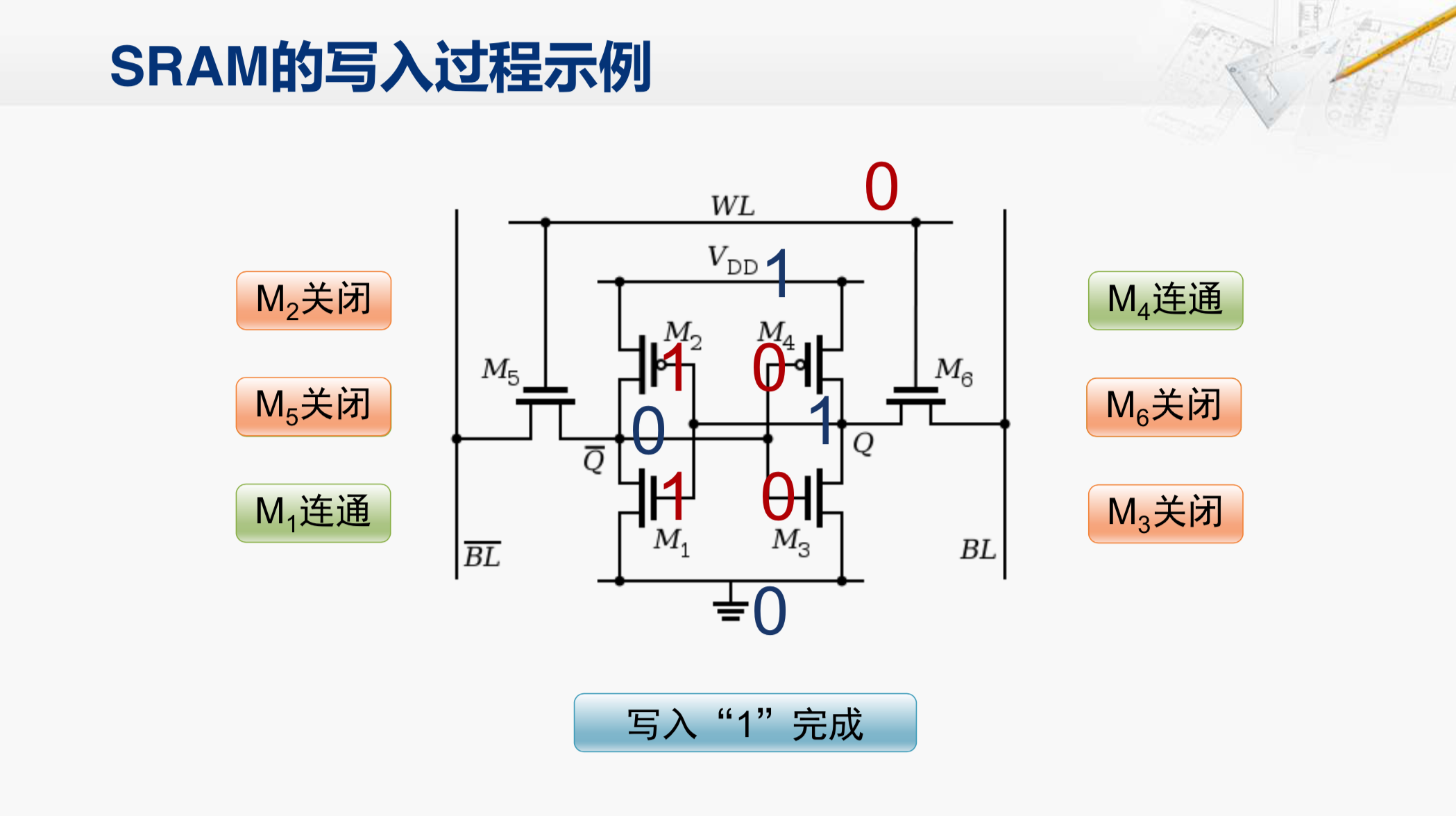

我们先来看看SRAM的基本结构。这个结构一共有六个晶体管构成,我们分别用\(M_1\)~\(M_6\)进行标记。这六个晶体管合在一起才可以保存一个比特,显然比DRAM的一个基本存储单元要复杂得多。这个基本存储单元对外有三个接口信号,其中BL和BLbar是用于传送读写数据信息的,而WL信号则是用于控制外部是否可以访问这个基本存储单元。那么就通过读写的实例来看一看SRAM是如何工作的。

我们以写入数据1为例来进行分析。首先这个存储单元中连接的电源和地分别代表着一和零,只要SRAM处于通电状态,这两个信号的值都会保持稳定。那如果要写入1,就得将BL的信号的值置为1,而与之相对则需要将BL bar信号置为零,这样就准备好了要写入的数据。然后我们需要访问这个SRAM单元,就得把wl信号置为1,一旦wl信号为1,那它所连接的M5和M6这两个晶体管的gate端就都为1。那通过这个图标我们就可以看出M6是一个NMOS晶体管,NMOS晶体管的gate端连接为一时,这个晶体管应该是连通还是关闭呢?这一点我们以前已经学习过,你还记得吗?那当然对于NMOS来说,如果gate端为一,它应该是处于连通状态。因此,BL信号上的值就会通过M6传递进来。那么来看一看这根信号控制了哪些晶体管的gate端。首先它是连到了M2晶体管的gate端,那么看M2是一个什么类型的晶体管呢?它是一个PMOS管,PMOS管的gate端如果为1,那就应该处于关闭的状态,因为M2是关闭的,所以从电源这(\(V_{DD}\))连过来的1不会被传导出来,所以这根信号线上的值到底是什么,我们还得来看下面这个晶体管也就是M1。而M1的gate端和M2的gate端连接的是同一个信号,所以现在也是1,M1是一个NMOS,所以它处于连通状。所以,这根信号上的值就应该是零。那么还应该注意到这根信号线同时连接到了M5的这跟晶体管,而M5的gate端也是由WL信号控制的,所以M5也是处于联通状态,它会将BL bar信号的0传导进来。那么我们刚才分析了从地传过来的也是零,这样就没有冲突,这根信号就可以稳定地维持为0。

那么我们现在来看这根信号又控制了哪些晶体管的gate端。首先是M4,M4是一个PMOS管,它的gate端为0的时候,它就处于连通状态,那来自电源的这个1会被传导进来。与此同时M3的gate端也是0,那这根NMOS晶体管就会处于关闭状态。所以这根信号与地是不连通的,这样从M3和M4的控制来看,这跟信号也应该是1,这和由BL信号传递进来的这个1也是没有冲突的。这样由外部的BL和BL bar输入的信号就驱动了这个SRAM存储单元的晶体管达到了一个稳定的状态。

因为晶体管的工作速度很快。所以,这个SRAM的写入的过程也非常快,当这几个晶体管状态达到稳定之后我们就可以结束这次写的过程了。视频讲解

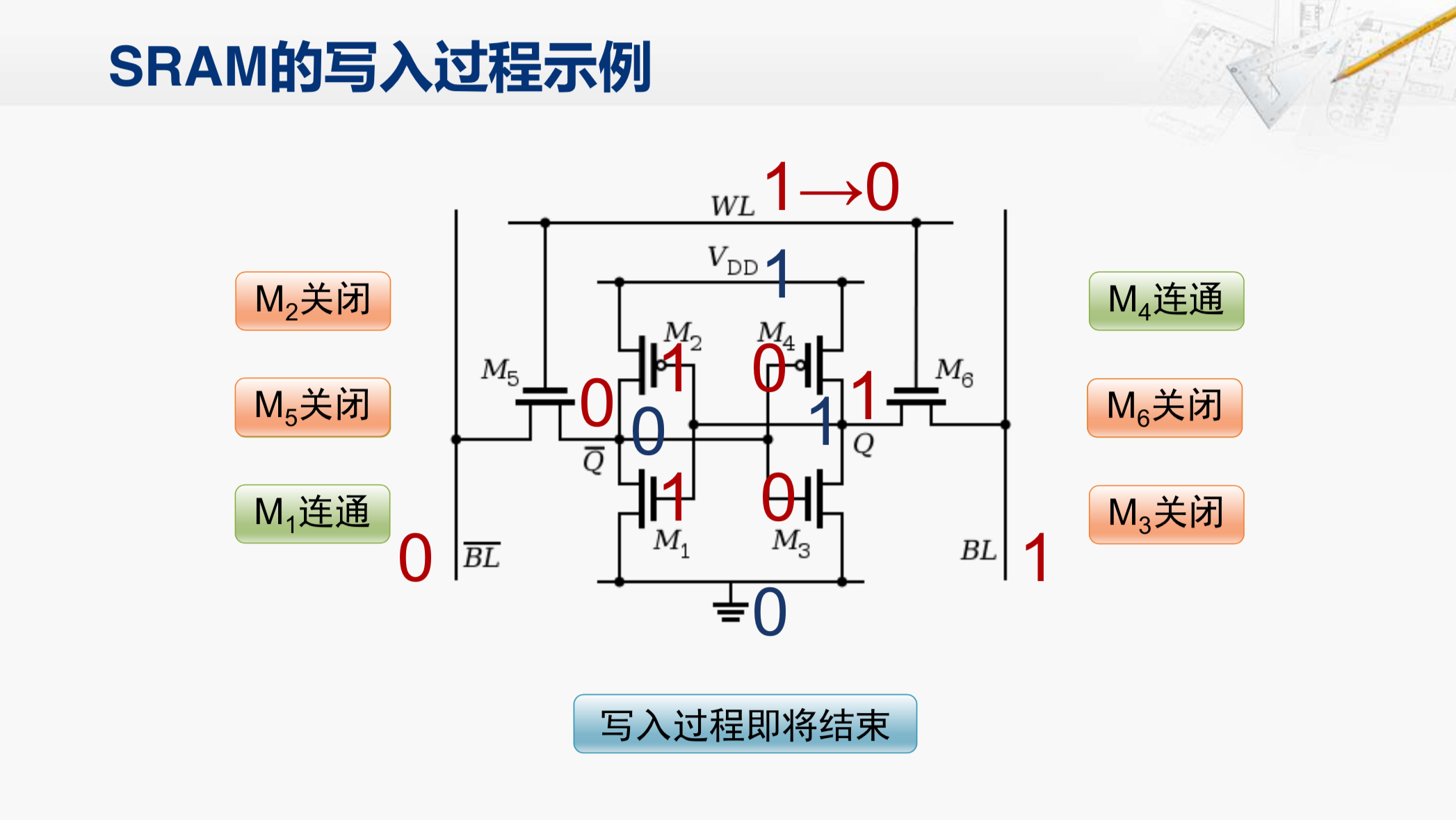

现在我们可以将WL信号由1变为0,从而将M5和M6这两个晶体管关闭。然后就可以撤销BL和BL bar上的信号了。

那在外部的信号撤销之后,因为M5和M6这两个晶体管都关闭了。所以,并不是由外部的BL信号驱动M2和M1这两个晶体管的gate端。但是我们注意在刚才写入的过程中,因为M4晶体管处于连通状态,所以电源所传导的这个1会始终驱动这根信号,保持M2和M1的gate端为1。而只要M2和M1的gate端为1,那么由地传过来的这个0就会保持稳定,而这个0又会反过来驱动M4和M3保持刚才的状态,从而让这个1也保持稳定。

在这四个晶体管的相互作用下,这个SRAM单元就稳定地保持住了刚才写入的这个数据1。那现在只要WL信号保持为零,这个SRAM 存储单元当中就会始终存储的这个数据1。当然前提是要保持通电的状态,如果断电,电源的这个1消失了,那SRAM当中保存的这个数据也就会丢失。

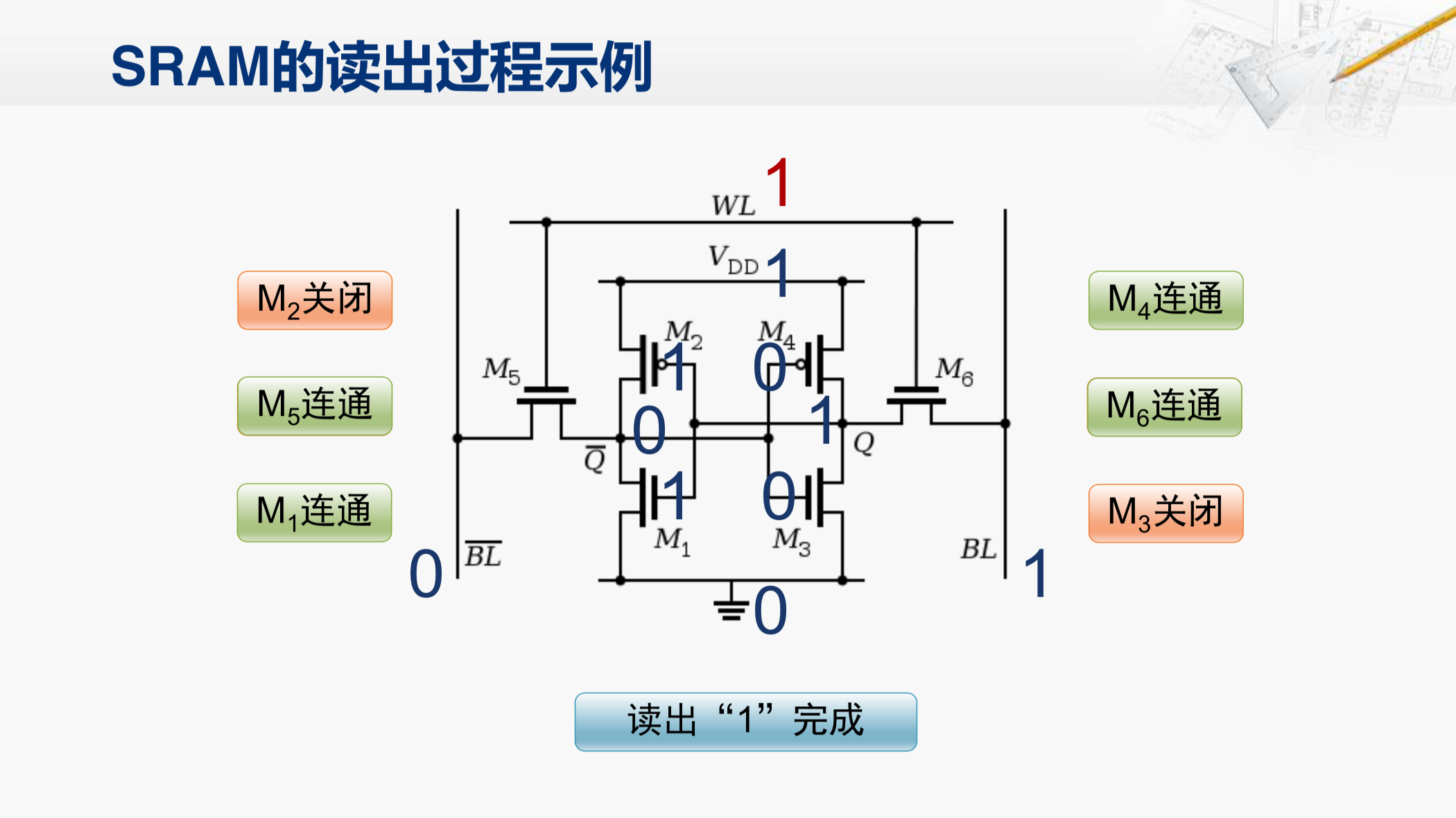

在这个基础上我们再来看SRAM的读出过程。这还是刚才那个SRAM单元,里面已经保持了一个数据1。现在外部就来读取这个单元,这还是需要把WL信号置为1,那这样M5和M6这两个晶体管都会处于连通的状态。而此时外部并不驱动BL和BL bar这两根信号,因此它们将会分别通过M5和M6这两个晶体管被这个SRAM的存储单元所驱动,BL bar的信号将会被驱动为0,而BL的信号将会被驱动为1,这样外部在接受到这两根信号之后就可以判断出读出的是一个数据1。

这就是一个SRAM基本单元的结构和工作原理。

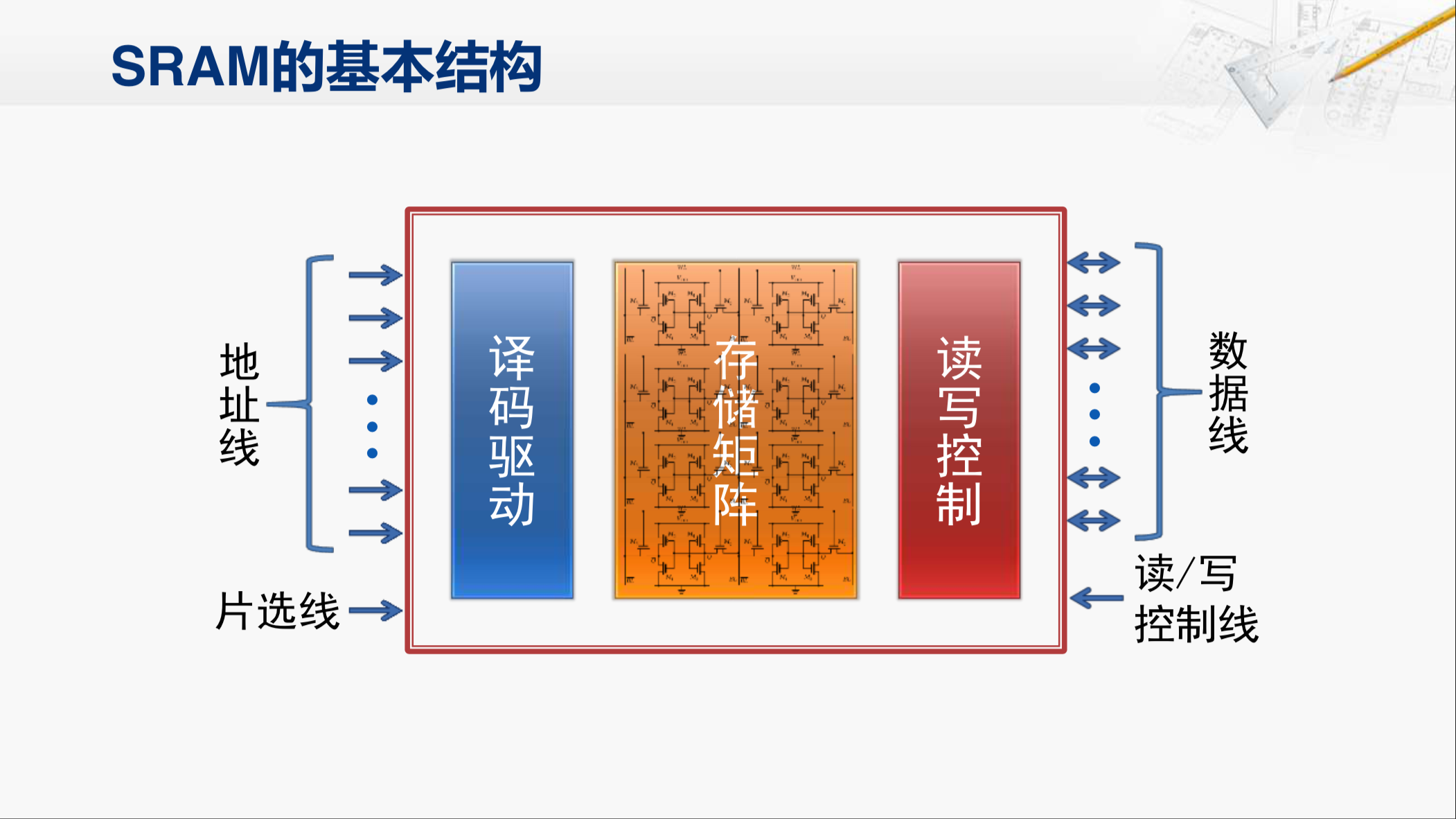

那如果我们将很多个这样的基本单元组合起来就可以构成一个存储矩阵。从外部可以输入若干个地址线,通过再增加一些地址译码的驱动电路,就可以根据地址信号线的值选中存储矩阵当中指定的若干个SRAM的基本存储单元。由SRAM构成的存储器和DRAM芯片不太一样,它不需要分成行地址和列地址分别选择,而且相对来说SRAM的设计是比较灵活的,一个地址所对应的存储单元的数量也许是8个比特,10个比特,也可以是32个比特,40个比特,64个比特等等都可以。那通过地址线选中的一组存储单元之后,我们还要确定到底是需要读还是写,所以外部还需要有读写控制信号,并且有相应的读写控制电路。而且这些读写控制电路还会将外部传来的数据线连接到SRAM的存储单元上,如果现在是写,这样来自外部数据线的信号去驱动存储单元;而如果是读,则将存储单元当中的信号驱动外部的数据线。这样的电路一般就称为一个SRAM的存储器。通常这个SRAM存储器还会有片选信号,以标明当前是否需要对这个SRAM存储器进行读或者写的操作。

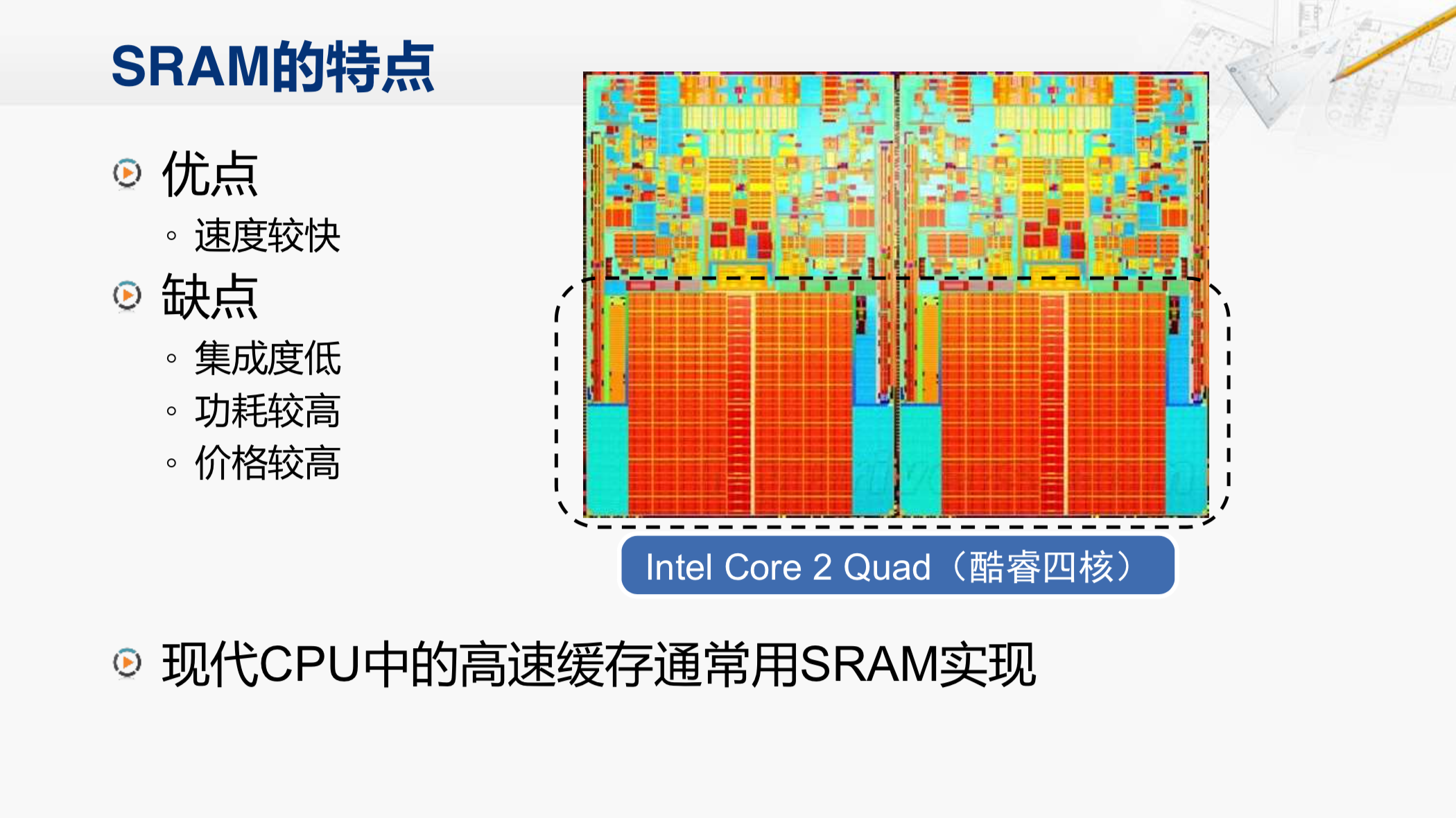

由此看来因为晶体管的开关速度远比电容充放电的速度要快。所以,相对于DRAM,SRAM有速度快的优势。但是我们也看到SRAM中要存储一个比特就需要用六个晶体管,晶体管数量多就会造成芯片的面积大,从而带来集成度低和价格较高的问题。同时每个晶体管都是要耗电的,晶体管越多功耗也就会越高,这些都是SRAM的缺点。

现在CPU当中的高速缓存一般都是用SRAM来实现的。比如右边这就是一颗四核CPU的版图,在这个芯片当中这些大面积的看起来非常规整的电路实际上都是SRAM。所以,仅从制造成本上来看这些作为高速缓存SRAM往往要占到整个CPU的一半或者更多。而且由于高速缓存大多和CPU采用相等或者接近的时钟频率。所以,它们的功耗也非常高,这都是在使用SRAM实现高速缓存时需要注意的问题。

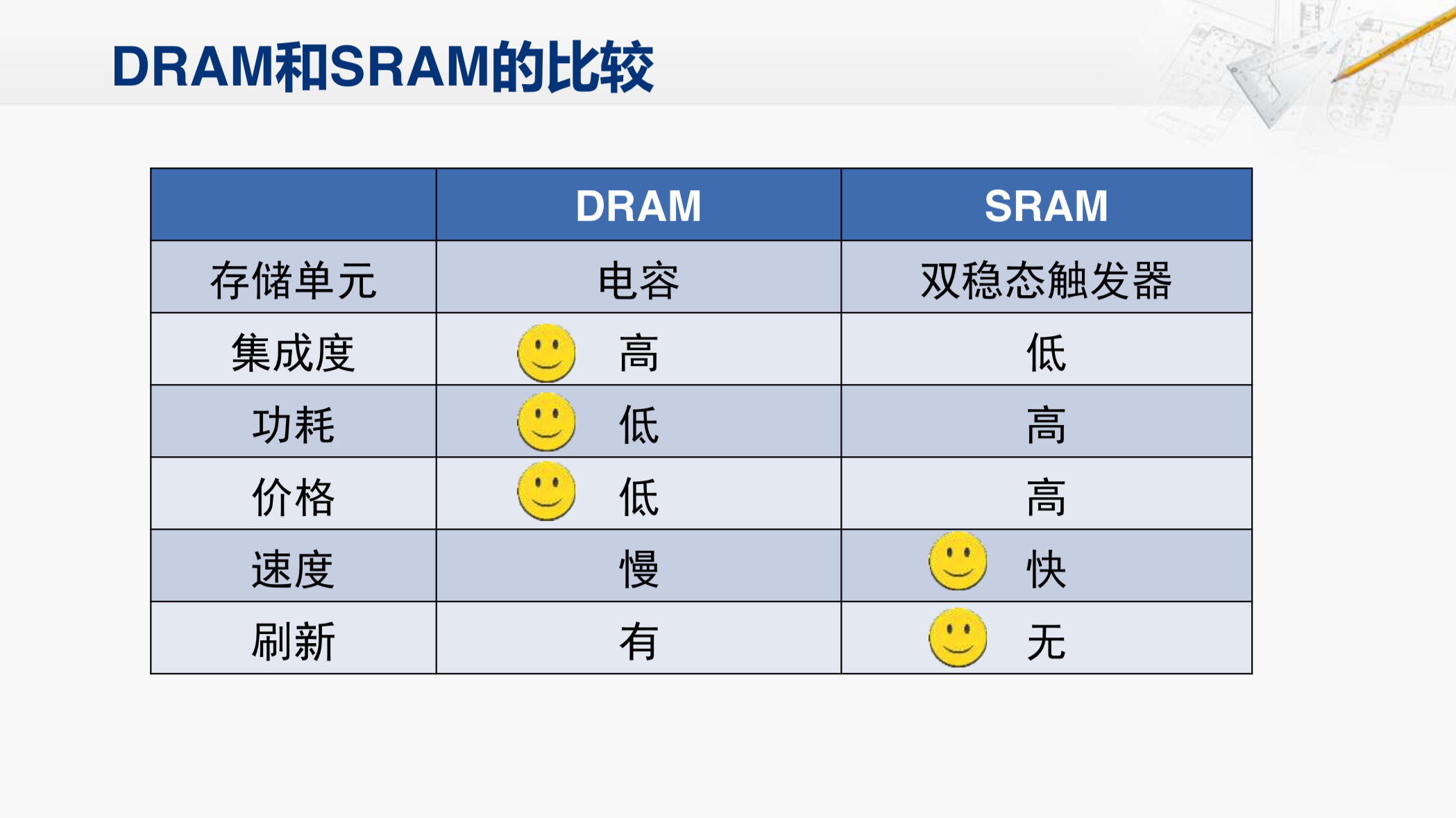

那么综合比较来看DRAM的主要优势在于集成度高,功耗低,价格低;而SRAM的优势则于速度快,而且不像DRAM需要经常进行刷新。所以,我们需要根据它们不同的特点,用在不同的场合上。

现在我们已经掌握了DRAM和SRAM的内部结构以及其工作原理,那我们也就知道了他们的那些特点是如何产生的。这对我们理解存储体系是如何构成的有着非常重要的帮助。

浙公网安备 33010602011771号

浙公网安备 33010602011771号