第23课 - 模块独立编译的支持

1.问题背景

一般而言,在一个大型项目中,不同工程师负责不同模块的开发;那么问题就来了,我们怎么知道自己编写的这部分代码有没有问题,怎样进行编译?在编译环境中如何支持模块的独立编译?

-

在大型项目中的代码文件成千上万,完整编译的时间较长;

-

编写模块代码时,可通过编译检查语法错误;

-

为了提高开发效率,需要支持指定模块的独立编译。

2.解决方案

1、将模块名(module)作为目标名(伪目标)建立规则;

2、目标(module)对应的依赖为 build build/module;

3、规则中的命令进入对应的模块文件夹进行编译;

4、编译结果存放于 build 文件夹下。

关键技术点:

如何获取 make 命令行中指定编译的模块名?

- 通过预定义变量:$(MAKECMDGOALS),命令行中指定的目标名(make 的命令行参数)

下来我们来看看具体的 makefile 是怎样写的,将上节博客中的 pro-rule.mk 改成下面这样:

模块的独立编译:

.PHONY : all compile link clean rebuild $(MODULES) DIR_PROJECT := $(realpath .) DIR_BUILD_SUB := $(addprefix $(DIR_BUILD)/, $(MODULES)) MODULE_LIB := $(addsuffix .a, $(MODULES)) MODULE_LIB := $(addprefix $(DIR_BUILD)/, $(MODULE_LIB)) APP := $(addprefix $(DIR_BUILD)/, $(APP)) all : compile $(APP) @echo "Success! Target ==> $(APP)" compile : $(DIR_BUILD) $(DIR_BUILD_SUB) @echo "Begin to compile ..." @set -e; \ for dir in $(MODULES); \ do \ cd $$dir && \ $(MAKE) all \ DEBUG:=$(DEBUG) \ DIR_BUILD:=$(addprefix $(DIR_PROJECT)/, $(DIR_BUILD)) \ DIR_COMMON_INC:=$(addprefix $(DIR_PROJECT)/, $(DIR_COMMON_INC)) \ CMD_CFG:=$(addprefix $(DIR_PROJECT)/, $(CMD_CFG)) \ MOD_CFG:=$(addprefix $(DIR_PROJECT)/, $(MOD_CFG)) \ MOD_RULE:=$(addprefix $(DIR_PROJECT)/, $(MOD_RULE)) && \ cd .. ; \ done @echo "Compile Success!" link $(APP) : $(MODULE_LIB) @echo "Begin to link ..." $(CC) -o $(APP) -Xlinker "-(" $^ -Xlinker "-)" $(LFLAGS) @echo "Link Success!" $(DIR_BUILD) $(DIR_BUILD_SUB) : $(MKDIR) $@ clean : @echo "Begin to clean ..." $(RM) $(DIR_BUILD) @echo "Clean Success!" rebuild : clean all $(MODULES) : $(DIR_BUILD) $(DIR_BUILD)/$(MAKECMDGOALS) @echo "Begin to compile $@" @set -e; \ for dir in $(MODULES); \ do \ cd $@ && \ $(MAKE) all \ DEBUG:=$(DEBUG) \ DIR_BUILD:=$(addprefix $(DIR_PROJECT)/, $(DIR_BUILD)) \ DIR_COMMON_INC:=$(addprefix $(DIR_PROJECT)/, $(DIR_COMMON_INC)) \ CMD_CFG:=$(addprefix $(DIR_PROJECT)/, $(CMD_CFG)) \ MOD_CFG:=$(addprefix $(DIR_PROJECT)/, $(MOD_CFG)) \ MOD_RULE:=$(addprefix $(DIR_PROJECT)/, $(MOD_RULE)) && \ cd .. ; \ done @echo "Compile Success!"

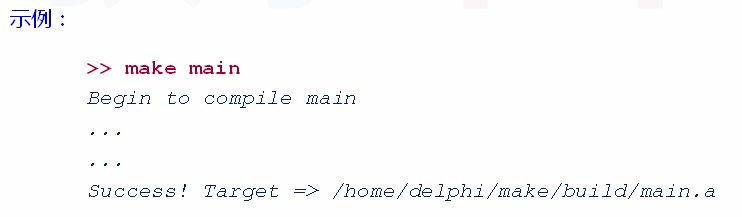

运行结果:

我们看到 common 模块已经正确编译了,而且生成相应的 common.a 文件了。我们再继续编译别的两个模块,再通过链接的命令看看可执行程序 app.out 是否可以生成。

我们看到可执行程序 app.out 已经正确生成了。那么我们看到刚才的模块编写是直接复制之前的代码,凡是涉及到复制粘贴的代码,我们得看看是否可以封装成类似于函数的形式。

makefile中的代码复用:

-

当不同规则中的命令大量重复时,可考虑自定义函数

-

makefile 中的自定义函数是代码复用的一种方式

具体思路:

1、将编译模块的命令作为自定义函数的具体实现;

2、函数参数为模块名,函数调用后编译参数指定的模块;

3、在不同的规则中调用该函数。如下

下面我们看看改变后的 makefile 是怎样的,将前面的 pro-rule.mk 改成下面这样:

.PHONY : all compile link clean rebuild $(MODULES) DIR_PROJECT := $(realpath .) DIR_BUILD_SUB := $(addprefix $(DIR_BUILD)/, $(MODULES)) MODULE_LIB := $(addsuffix .a, $(MODULES)) MODULE_LIB := $(addprefix $(DIR_BUILD)/, $(MODULE_LIB)) APP := $(addprefix $(DIR_BUILD)/, $(APP)) define makemodule cd ${1} && \ $(MAKE) all \ DEBUG:=$(DEBUG) \ DIR_BUILD:=$(addprefix $(DIR_PROJECT)/, $(DIR_BUILD)) \ DIR_COMMON_INC:=$(addprefix $(DIR_PROJECT)/, $(DIR_COMMON_INC)) \ CMD_CFG:=$(addprefix $(DIR_PROJECT)/, $(CMD_CFG)) \ MOD_CFG:=$(addprefix $(DIR_PROJECT)/, $(MOD_CFG)) \ MOD_RULE:=$(addprefix $(DIR_PROJECT)/, $(MOD_RULE)) && \ cd .. ; endef all : compile $(APP) @echo "Success! Target ==> $(APP)" compile : $(DIR_BUILD) $(DIR_BUILD_SUB) @echo "Begin to compile ..." @set -e; \ for dir in $(MODULES); \ do \ $(call makemodule, $$dir) \ done @echo "Compile Success!" link $(APP) : $(MODULE_LIB) @echo "Begin to link ..." $(CC) -o $(APP) -Xlinker "-(" $^ -Xlinker "-)" $(LFLAGS) @echo "Link Success!" $(DIR_BUILD) $(DIR_BUILD_SUB) : $(MKDIR) $@ clean : @echo "Begin to clean ..." $(RM) $(DIR_BUILD) @echo "Clean Success!" rebuild : clean all $(MODULES) : $(DIR_BUILD) $(DIR_BUILD)/$(MAKECMDGOALS) @echo "Begin to compile $@" @set -e; \ $(call makemodule, $@)

运行结果:

我们看到 makefile 的代码已经是相当简洁了,通过对单独模块 makefile 的编写。

3.总结

1、编写模块代码时可通过模块独立编译快速检查语法错误;

2、自动变量只能在规则的命令中使用,不能在依赖中使用;

3、makefile 中的自定义函数是代码复用的一种方式;

4、当不同规则中的命令大量重复时,可考虑自定义函数。

浙公网安备 33010602011771号

浙公网安备 33010602011771号