计算机组成原理知识点

第一章

电子计算机分为电子模拟计算机(应用范围较小)和电子数字计算机(还有数模混合),数字计算机的主要特点是按位运算,并且不连续地跳动计算。平常说的计算机都是电子数字计算机。

电子数字计算机分为专用计算机和通用计算机。

运算器+控制器等于一个cpu

第一台计算机1946年美国宾夕法尼亚大学。

冯诺依曼型计算机的设计思想是存储程序并按地址顺序执行。

运算器又被称为ALU(算数逻辑运算部件),主要是算术运算和逻辑运算。

存储器是存储数据和程序(指令)的。

计算机软件分为系统程序和应用程序

根据不同使用环境要求,操作系统分为批处理操作系统,分时操作系统,网络操作系统,实时操作系统。

编程语言的发展

-

手编程序,机器语言程序,手工编译二进制编码

-

汇编程序,符号语言程序,汇编程序汇编

-

高级程序,算法语言/高级语言,机器编译程序/解释程序

第二章

计算机中的数据分为符号数据和数值数据。

数值第一位为0表示是正数,为1表示为负数。

正数的原码反码补码都是一样的;负数原码除符号位外其余位取反得到反码,反码加一得到补码。

移码不管正负都是在补码的基础上将符号位取反,其它位不变。

0的补码是唯一的。移码也是唯一的。

01表示上溢(正溢),10表示下溢(负溢)。

双符号位正数符号位是两个0,负数符号位是两个1。

第三章

程序的局部性可以从两个角度进行分析:

-

时间局部性:最近被访问的信息可能还要被访问

-

空间局部性:最近被访问的信息邻近地址的信息也可能被访问

容量等于2的地址线条数乘以数据线(位)。

SRAM相比DRAM速度快,容量小,存储密度低。

cache是一种高速缓冲存储器,为了解决cpu和主存之间速度不匹配的一种重要技术,原理基于程序运行中具有的空间局部性和时间局部性特征。

cache介于cpu和主存之间的小容量存储器,存取速度比主存快,容量小。由SRAM组成。

cpu和cache之间数据交换是以字为单位的,而cache和主存之间是以块为单位。

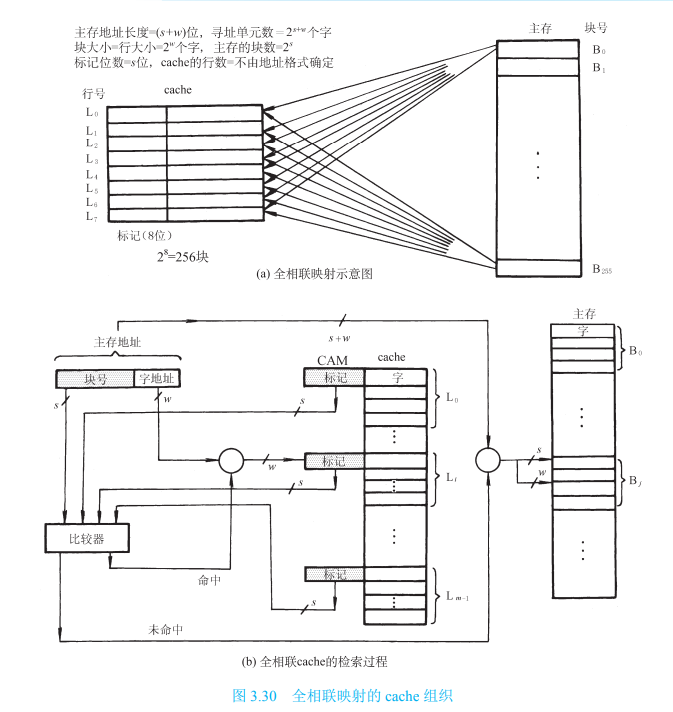

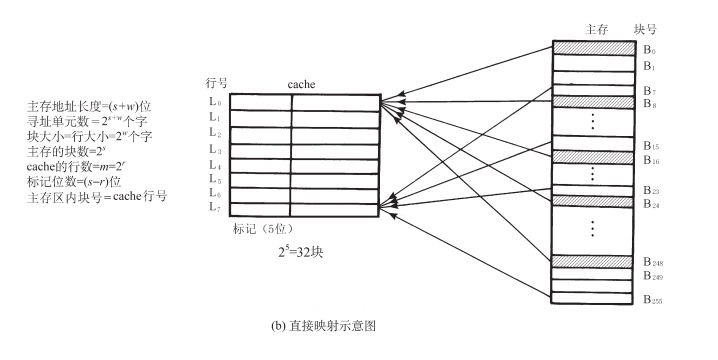

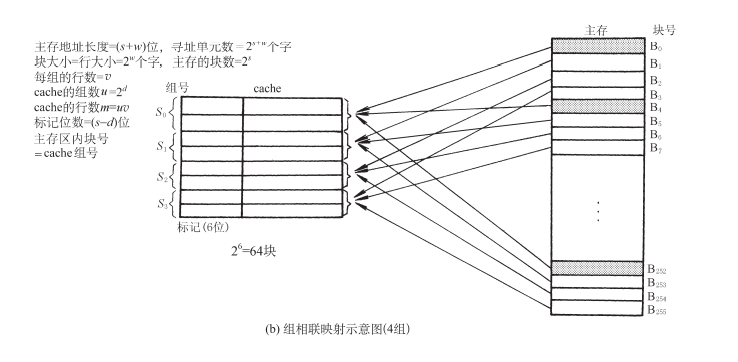

cache和主存的地址映射方式:全相联映射方式,直接映射方式,组相联映射方式。

cache的替换策略:最不经常使用算法(LFU)-将一段时间内被访问次数最少的那行数据替换(使用次数最少的);近期最少使用算法(LRU)-将近期内长久未被访问的行替换(从后到前使用最晚的);随机替换。

一条指令的指令周期包括两个或两个以上的cpu周期(cpu周期又叫机器周期),一个cpu周期包括多个T周期(时钟周期)。

存储字长是指(存放在一个存储单元中的二进制代码位数)。

存储周期是指(存储器进行连续读或写操作所允许的最短间隔时间)。

计算机的存储器采用分级存储体系的主要目的是(解决存储容量、价格和存取速度之间的矛盾)。

半导体静态存储器SRAM的存储原理是(依靠双稳态电路)。

# 题目

某计算机字长是32位,它的存储容量是64KB,按字编址,它的寻址范围是(16K)。

# 解释

按字编址,每个存储单元一个字节。因为该计算机的字长是32位,每个存储单元1个字节,1字节等于8位,所以相当于4个字节。又因为他的存储器容量是64KB,则说明有64K个字节,64/4=16。

第六章

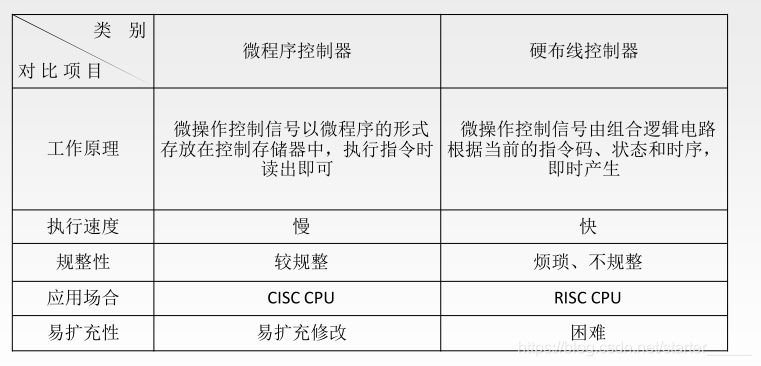

机器指令、微程序和微指令的关系:一条机器指令对应一个微程序,这个微程序是由若干条微指令构成的。

在微指令编码中,编码效率最低的是直接编码方式。

微程序放在(控制存储器)部件中。

程序控制类指令的功能是(改变程序执行的顺序)。

将微程序存储在EPROM中的控制器是(静态微程序 )控制器。

在控制器的控制信号中,相容的信号是( 可以同时出现)的信号。

微程序控制器比硬连线控制器更加灵活。

(间接寻址)可以缩短指令中某个地址段的位数。

- 水平型微指令:微程序短、执行速度快;微指令长,编写程序麻烦(特点:一次可以完成多个操作)

- 垂直型微指令:微指令短,便于编写程序;微程序长,执行速度慢(特点:采用微操作码)

执行( 微指令)是控制部件通过控制线向执行部件发出各种控制命令。

微指令中的微地址表示(后继微指令地址)。

由编译程序将多条指令组合成一条指令,这种技术称做(超长指令字技术)。

(超标量技术)是在每个时钟周期内同时并发多条指令。

计算机的并行处理技术主要有三种形式,包括时间并行、空间并行 和 时间空间并行。

在一个有四个过程段的浮点加法器流水线中,假设四个过程段的时间分别是T1 = 60ns﹑T2 = 50ns﹑T3 = 90ns﹑T4 = 80ns。则加法器流水线的时钟周期至少为(90ns )。如果采用同样的逻辑电路,但不是流水线方式,则浮点加法所需的时间为( 280ns)。

考题

计算机运算溢出检测机制,采用双符号位,00表示正号,11表示负号。如果进位将会导致符号位不一致,从而检测出溢出。结果的符号位为01时,称为上溢;为10时,称为下溢。

冯诺依曼的工作方式:按地址访问并按顺序执行

主存储器和CPU之间增加cacha的目的是:解决CPU和主存之间的速度不匹配问题

指令系统中采用不同寻址方式的目的是:缩短指令长度、扩大寻址空间、提高编程灵活性

各个映射(又叫映像 )关系:直接映射、全相联映射、组相联映射、混合映射(P94)

-

直接映射:主存中的一个块只能映射到Cache的某一特定块中去。(适用于小容量Cache)

-

全相联映射:主存中任何一块都可以映射到Cache中的任何一块位置上。(适用于大容量高速Cache)

-

组相联映射:主存和Cache都分组,主存中一个组内的块数与Cache中的分组数相同,组间采用直接映射,组内采用全相联映射。

运算器的核心部分是(算术逻辑运算单元)。

计算机的程序是由一系列的机器指令组成的。从计算机组成的层次结构来说,计算机指令分为微指令、机器指令和宏指令。

CISC(complex instruction set computer):复杂指令系统计算机,RISC(reduced instruction set computer):精简指令系统计算机。

中断向量可提供(中断服务程序入口地址)。

同步控制是(由统一时序信号控制的方式)。

浮点数的表示范围和精度取决于(阶码的位数和尾数的位数)。

CPU响应中断的时间是(执行周期结束)。

总线中地址线的作用是(用于选择指定存储器单元和IO设备接口电路的地址)。

在程序执行过程中,控制器控制计算机的运行总是处于(取指令)、(分析指令)和(执行指令)的循环之中。

计算机中各个功能部件是通过(总线)连接的。

指令寻址的两种方式:(顺序)寻址和(跳跃)寻址。

控制存储器是用来存放实现全部指令系统的(微程序),控制存储器是一种只读存储器。

输入输出系统的信息交换方式有:(程序查询)方式、(中断)方式、(DMA)方式、通道方式和外围处理方式。

在计算机系统中,CPU管理外围设备的四种方式:程序查询方式、中断方式、DMA和通道方式。

采用 DMA(直接内存访问) 方式传送数据时,CPU 和DMA 控制器内存使用权冲突时的解决方案包括:CPU停机(成组连续传送方式)、

周期挪用方式(单字传送方式,周期窃取方式)、透明DMA方式(DMA与CPU交替操作方式,总线周期分时方式)。(P260)

计算机操作的最小时间单位是:时钟周期。

在机器数中,(补码)的零的表示形式是唯一的。

总线特性有(电气)特性、(功能)特性、(物理)特性。

动态半导体存储器的特点是(每隔一定时间,需要根据原存内容重新写入一遍)。

一个完善的指令系统包括(数据处理,数据存储,数据传送,程序控制)四大类指令。

CPU的四个基本功能:指令控制、操作控制、时间控制、数据加工。

中断向量地址是(中断服务程序入口地址指示器)。

在CPU中,跟踪后继指令地址的寄存器是(程序计数器)。

层次化存储系统分为Cache、内存和外存。

若X=11011011B,则2X=10110110B(右侧加个0),(1/2)X=01101101B(左侧加个0),(1/4)X=00110110B(左侧加两个0)。

计算机执行乘法指令时,由于其操作较复杂,需要更多的时间,通常采用(中央与局部控制相结合的)控制方式。

大题

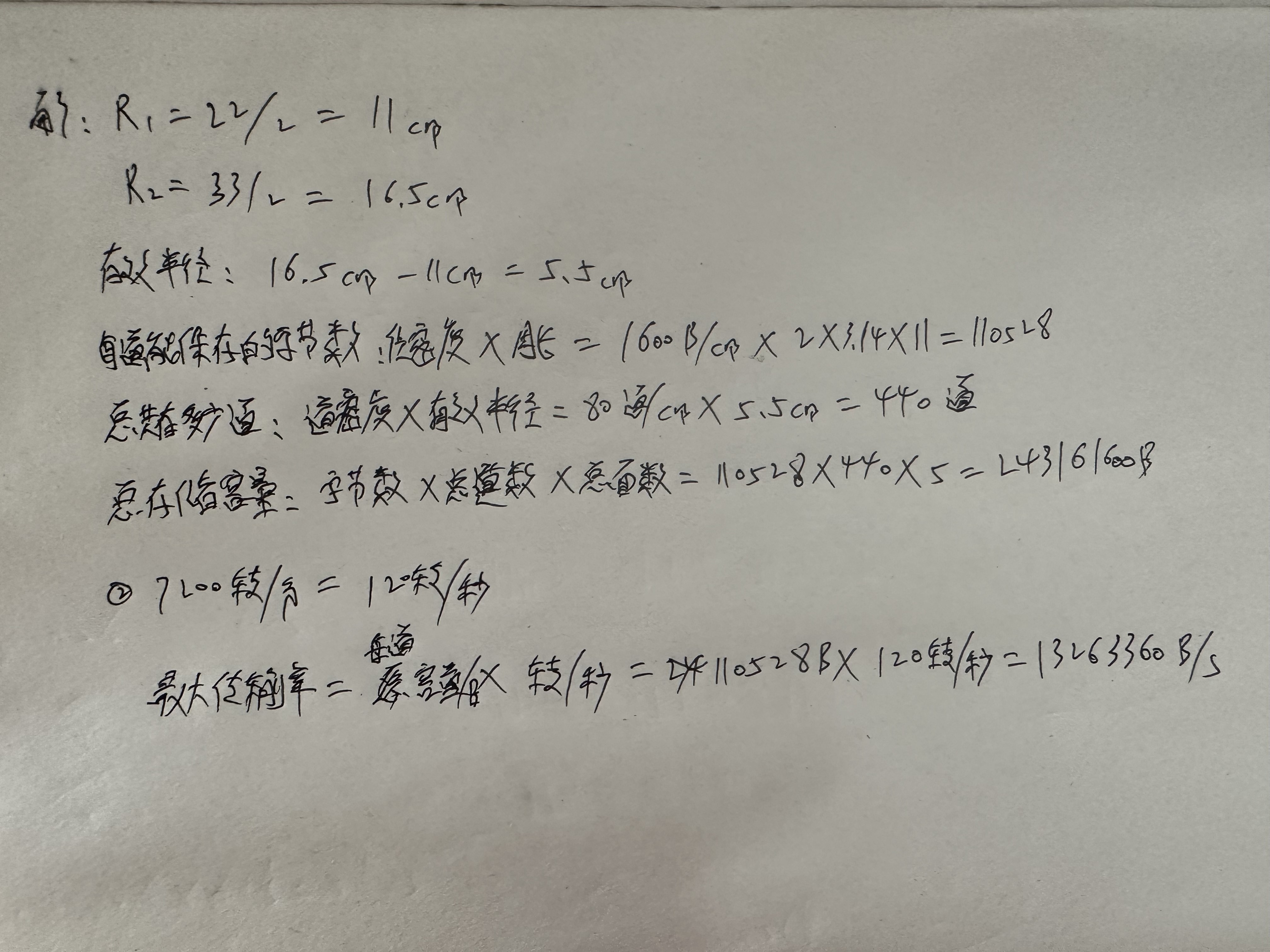

某磁盘组有4个盘片,5个记录面,每个记录面的内磁道直径为22cm,外磁道直径为33cm,最大位密度为1600B/cm,道密度为80道/cm,转速7200转速/分。

(1)磁盘的总存储容量?

(2)最大量数据传输率是多少?